一种半导体器件的制造方法

本发明涉及半导体制造,尤其涉及一种半导体器件的制造方法。

背景技术:

1、随着半导体器件的微缩,半导体器件各部分的尺寸不断缩小。相应的,在衬底上制造的为了形成埋沟式晶体管的硬掩膜图案,其尺寸也逐渐减小、甚至超出了光刻的物理极限。在此情况下,往往需要采用自对准双重图案成形技术或自对准多重图案成形技术形成上述硬掩膜图案,以克服单次构图不能达到的光刻极限。

2、但是,现有用于形成上述硬掩膜图案的方法所包括的半导体器件的工艺步骤较多,降低了半导体器件的制造效率。

技术实现思路

1、本发明的目的在于提供一种半导体器件的制造方法,用于在减少半导体器件工艺步骤的同时,提高半导体器件的制造效率。

2、为了实现上述目的,本发明提供了一种半导体器件的制造方法,该制造方法包括:

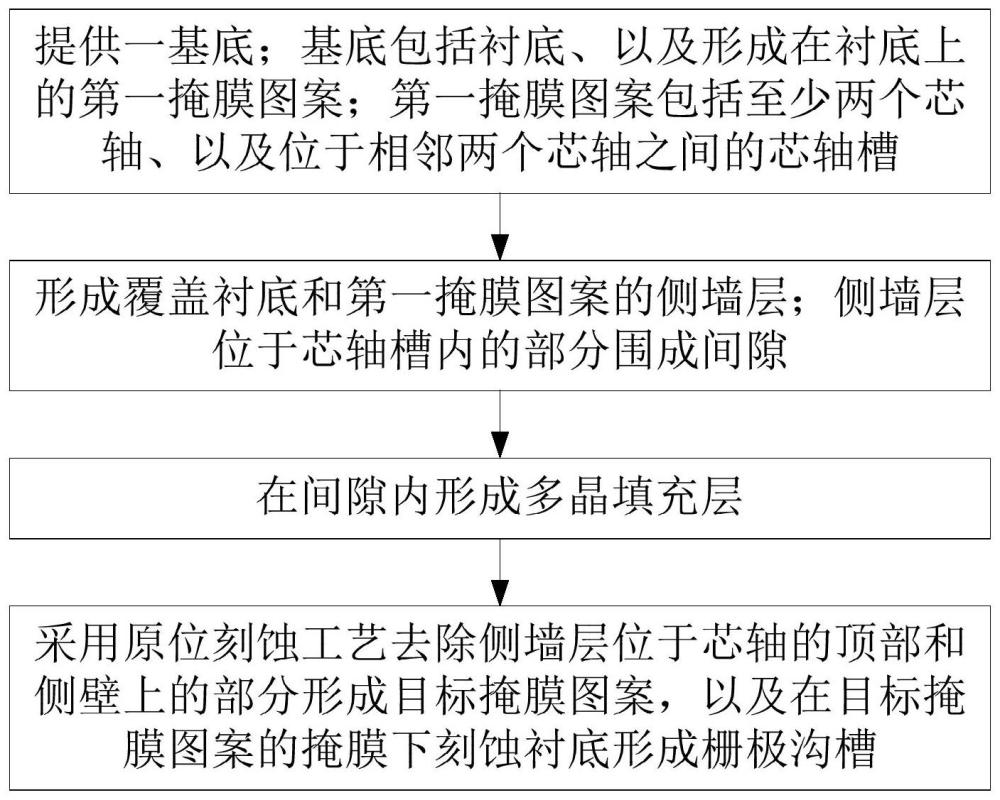

3、提供一基底;基底包括衬底、以及形成在衬底上的第一掩膜图案;第一掩膜图案包括至少两个芯轴、以及位于相邻两个芯轴之间的芯轴槽;

4、形成覆盖衬底和第一掩膜图案的侧墙层;侧墙层位于芯轴槽内的部分围成间隙;

5、在间隙内形成多晶填充层;

6、采用原位刻蚀工艺去除侧墙层位于芯轴的顶部和侧壁上的部分形成目标掩膜图案,以及在目标掩膜图案的掩膜下刻蚀衬底形成栅极沟槽。

7、与现有技术相比,本发明提供的半导体器件的制造方法中,在衬底和第一掩膜图案上形成了侧墙层。该侧墙层位于芯轴槽内的部分围成间隙。接着在间隙内形成了多晶填充层。基于此,与现有方法中采用旋涂法在间隙内形成旋涂硬掩膜相比,多晶填充层的形成工艺为相对高温的工艺,该高温工艺对形成界面的要求较低,故在衬底上通过刻蚀工艺形成第一掩膜图案后无需额外对基底进行清洗操作,减少了半导体器件的工艺步骤。此外,在间隙内形成多晶填充层后,可以通过原位刻蚀工艺去除侧墙层位于芯轴的顶部和侧壁上的部分形成目标掩膜图案,以及在目标掩膜图案的掩膜下刻蚀衬底形成栅极沟槽。换句话说,与利用旋涂硬掩模作为间隙填充层相比,在形成了多晶填充层后,无需对其上形成有侧墙层和多晶填充层的基底进行清洗操作,也无需将上述基底转移到其他不同的刻蚀设备中就可以完成对侧墙层和衬底的刻蚀,从而能够节省因清洗和转移所需的时间,提高了半导体器件的制造效率。

技术特征:

1.一种半导体器件的制造方法,其特征在于,包括:

2.根据权利要求1所述的半导体器件的制造方法,其特征在于,所述在所述间隙内形成多晶填充层,包括:

3.根据权利要求1所述的半导体器件的制造方法,其特征在于,所述多晶填充层为多晶硅层、多晶三氧化二铝层或多晶二氧化铪层。

4.根据权利要求1~3任一项所述的半导体器件的制造方法,其特征在于,所述基底还包括形成在所述衬底上的刻蚀停止层,所述第一掩膜图案位于所述刻蚀停止层上;

5.根据权利要求4所述的半导体器件的制造方法,其特征在于,所述刻蚀停止层包括层叠设在所述衬底上的二氧化硅层、无定形碳层和氮氧化硅层;所述二氧化硅层形成在衬底的表面;所述无定形碳层位于所述二氧化硅层和所述氮氧化硅层之间。

6.根据权利要求1~3任一项所述的半导体器件的制造方法,其特征在于,在所述衬底上形成所述第一掩膜图案,包括:

7.根据权利要求6所述的半导体器件的制造方法,其特征在于,所述第二掩膜图案为光刻图案;

8.根据权利要求6所述的半导体器件的制造方法,其特征在于,所述第一掩膜层为旋涂硬掩膜层。

9.根据权利要求1~3任一项所述的半导体器件的制造方法,其特征在于,采用原子层沉积工艺形成覆盖所述衬底和所述第一掩膜图案的所述侧墙层;和/或,

10.根据权利要求1~3任一项所述的半导体器件的制造方法,其特征在于,所述衬底为硅衬底。

技术总结

本发明公开了一种半导体器件的制造方法,涉及半导体制造技术领域,用于在减少半导体器件工艺步骤的同时,提高半导体器件的制造效率。所述半导体器件的制造方法包括:提供一基底。基底包括衬底、以及形成在衬底上的第一掩膜图案。第一掩膜图案包括至少两个芯轴、以及位于相邻两个芯轴之间的芯轴槽。形成覆盖衬底和第一掩膜图案的侧墙层。侧墙层位于芯轴槽内的部分围成间隙。在间隙内形成多晶填充层。采用原位刻蚀工艺去除侧墙层位于芯轴的顶部和侧壁上的部分形成目标掩膜图案,以及在目标掩膜图案的掩膜下刻蚀衬底形成栅极沟槽。

技术研发人员:姜东勋,李俊杰,周娜,李琳,王佳

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!