一种逻辑芯片及电子设备的制作方法

本技术涉及逻辑运算,尤其涉及一种逻辑芯片及电子设备。

背景技术:

1、目前,由电流驱动的磁畴壁逻辑(domain wall logic,dwl)电路与互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)逻辑电路相比在非易失性、功耗以及尺寸等方面都有较大优势。另外,cmos逻辑电路主要由“与门”、“或门”和“非门”等电路组成,结构也比dwl电路更加复杂。因此,越来越多的逻辑电路逐渐使用dwl电路实现相应的逻辑功能。

2、虽然有很多的逻辑电路使用了dwl电路实现相应的逻辑功能,但是目前“异或门(exclusive or,xor)”、“全加法器”等逻辑电路仍然是参照cmos逻辑电路的设计思路对dwl电路进行设计,使得逻辑电路的结构过于复杂,尺寸较大,增加了集成难度和功耗。因此,亟需提供一种集成度更高的dwl电路,以便于在减小逻辑电路尺寸的同时降低功耗。

技术实现思路

1、本技术提供一种逻辑芯片及电子设备,简化了衬底上xor电路和全加法器的电路结构,在减小逻辑电路尺寸的同时降低了功耗。

2、本技术实施例提供的方案如下:

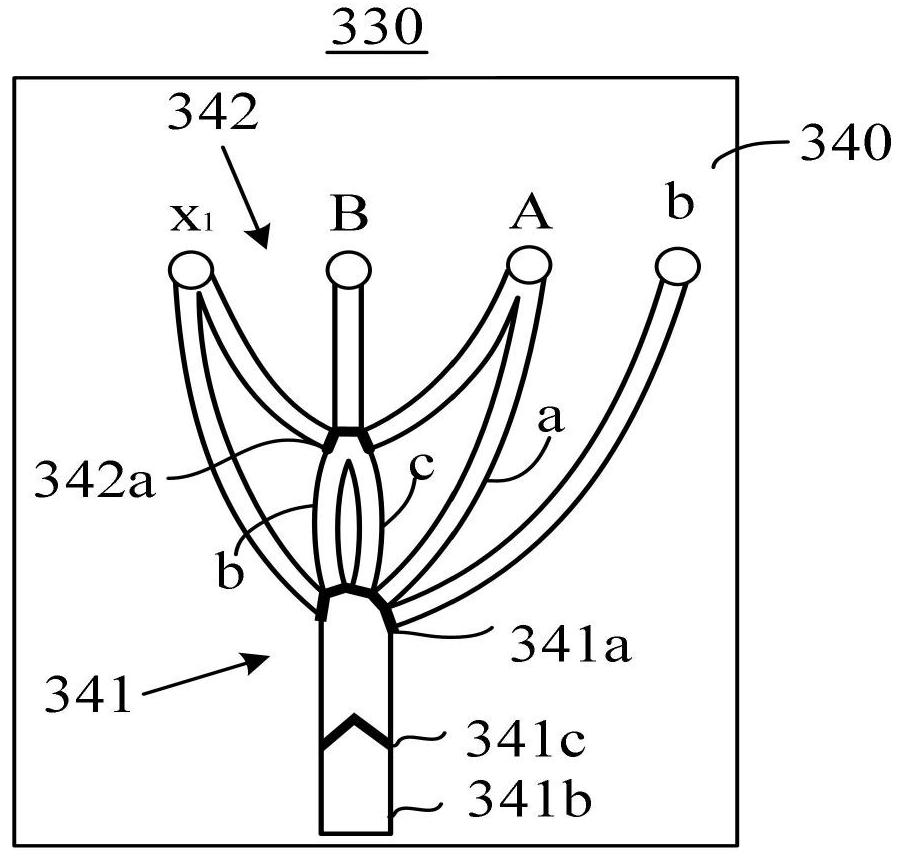

3、第一方面,提供了一种逻辑芯片,该逻辑芯片包括设置于衬底上的第一磁畴壁逻辑器件;其中,该第一磁畴壁逻辑器件包括设置在衬底上的至少四个输入极、偏置极、第一连接区域和输出极;其中第一磁畴壁逻辑器件的输入极和第一磁畴壁逻辑器件的偏置极通过第一磁畴壁逻辑器件的第一连接区域连接第一磁畴壁逻辑器件的输出极;其中,第一磁畴壁逻辑器件的输入极或第一磁畴壁逻辑器件的偏置极的磁化方向经第一磁畴壁逻辑器件的第一连接区域后在第一磁畴壁逻辑器件输出极输出相反的磁化方向;所述偏置极具有第一磁化方向。以第一磁畴壁逻辑器件具有四个输入极为例,当偏置极的信号为0(代表一个磁化方向),在电流的推动下,第一磁畴壁逻辑器件的四个输入极分别输入1(代表与0相反的另一个磁化方向)、1、0和0,经过第一连接区域,偏置极的磁化方向在输出极输出相反的磁化方向(即输出1),四个输入极的磁化方向均在输出极输出相反的磁化方向(即分别输出0、0、1和1),偏置极在输出极输出相反的磁化方向1;最终输出极输出的磁化方向取决于多数的磁化方向,即输出信号为1,实现对四个以上输入的多数决定门;与现有的利用多个级联的与非门实现多数决定的功能相比,该第一磁畴壁逻辑器件只需要通过一个连接区域形成一个多数决定门,缩短了传输路径,降低了电路的尺寸和功耗。

4、在一种可能的实现方式中,在第一磁畴壁逻辑器件的第一连接区域与第一磁畴壁逻辑器件的输出极的自由端之间还可以设置第二连接区域。其中,第一磁畴壁逻辑器件的第一连接区域与第一磁畴壁逻辑器件的第二连接区域之间具有第一磁化方向;第一磁畴壁逻辑器件的第二连接区域与第一磁畴壁逻辑器件的输出极的自由端之间具有与第一磁化方向相反的第二磁化方向。基于此,第二连接区域能够实现反相器的功能,从而对输出极输出的信号进行反相。

5、在一种可能的实现方式中,上述逻辑芯片还包括设置于衬底上的第二磁畴壁逻辑器件,第二磁畴壁逻辑器件包括设置在衬底上的至少两个输入极、偏置极、第一连接区域、输出极;第二磁畴壁逻辑器件的至少两个输入极和第二磁畴壁逻辑器件的偏置极通过第二磁畴壁逻辑器件的第一连接区域连接第二磁畴壁逻辑器件的输出极;其中,第二磁畴壁逻辑器件的输入极或第二磁畴壁逻辑器件的偏置极的磁化方向经第二磁畴壁逻辑器件的第一连接区域后在第二磁畴壁逻辑器件的输出极输出相反的磁化方向;其中,第二磁畴壁逻辑器件的偏置极与第一磁畴壁逻辑器件的偏置极连接;第一磁畴壁逻辑器件的两个输入极与第二磁畴壁逻辑器件的输出极连接;第一磁畴壁逻辑器件中剩余的输入极与第二磁畴壁逻辑器件中的输入极输入的信号相同。以第二磁畴壁逻辑器件具备两个输入极以及第一磁畴壁逻辑器件具有四个输入极为例;当偏置极的信号为0,在电流的推动下,第二磁畴壁逻辑器件的两个输入极分别输入1和0,则经过第一连接区域,两个输入极在输出极的输出信号为0和1,偏置极在输出极的输出信号为1;最终,输出极的输出信号为1;此时,第一磁畴壁逻辑器件与第二磁畴壁逻辑器件的输出极连接的两个输入极的信号均为1,另外两个输入极的信号为1和0,偏置极的信号为0;经过第二连接区域后,在第一磁畴壁逻辑器件的输出极输出的信号为0,此时可以实现异或功能。

6、在一种可能的实现方式中,第一磁畴壁逻辑器件的至少四个输入极中的两个输入极与第二磁畴壁逻辑器件的输出极独立连接。基于此,第二磁畴壁逻辑器件的其中两个输入极可以接收到相同的信号。

7、在一种可能的实现方式中,在第一磁畴壁逻辑器件上与第二磁畴壁逻辑器件的输出极连接的两个输入极采用一体化的方式。两个输入极采用一体化的方式,此时的磁畴宽度可以变成单个输入极的磁畴宽度的两倍,可以提高第二磁畴壁逻辑器件的输出极输出的信号对第一磁畴壁逻辑器件的输出极输出的信号的影响权重。

8、在一种可能的实现方式中,逻辑芯片还包括设置于衬底上的第二磁畴壁逻辑器件和第三磁畴壁逻辑器件;第二磁畴壁逻辑器件和第三磁畴壁逻辑器件均包括设置在衬底上的至少两个输入极、偏置极、第一连接区域、输出极;第二磁畴壁逻辑器件的输入极和第二磁畴壁逻辑器件的偏置极通过第二磁畴壁逻辑器件的第一连接区域连接第二磁畴壁逻辑器件的输出极;第三磁畴壁逻辑器件的输入极和第三磁畴壁逻辑器件的偏置极通过第三磁畴壁逻辑器件的第一连接区域连接第三磁畴壁逻辑器件的输出极;第二磁畴壁逻辑器件的输入极或第二磁畴壁逻辑器件的偏置极的磁化方向经第二磁畴壁逻辑器件的第一连接区域后在第二磁畴壁逻辑器件的输出极输出相反的磁化方向;第三磁畴壁逻辑器件的输入极或第三磁畴壁逻辑器件的偏置极的磁化方向经第三磁畴壁逻辑器件的第一连接区域后在第三磁畴壁逻辑器件的输出极输出相反的磁化方向;第二磁畴壁逻辑器件的偏置极和第三磁畴壁逻辑器件的偏置极均与第一磁畴壁逻辑器件的偏置极连接;第一磁畴壁逻辑器件的一个输入极与第三磁畴壁逻辑器件的输出极连接;第一磁畴壁逻辑器件的一个输入极与第二磁畴壁逻辑器件的输出极连接;其中,第一磁畴壁逻辑器件中剩余的输入极、第三磁畴壁逻辑器件的输入极以及第二磁畴壁逻辑器件的输入极输入相同的信号。以第二磁畴壁逻辑器件和第三磁畴壁逻辑器件均具备两个输入极为例以及第一磁畴壁逻辑器件具备四个输入极为例,当第二磁畴壁逻辑器件和第三磁畴壁逻辑器件的两个输入极的输入为1和0,偏置极的输入为0时,第二磁畴壁逻辑器件和第三磁畴壁逻辑器件均输出1;第一磁畴壁逻辑器件的输入极的输入则为1、0、1和1,偏置极的输入为0,则第一磁畴壁逻辑器件的输出极输出0,此时也可以实现异或功能。

9、在一种可能的实现方式中,输入极、偏置极以及输出极均包括层叠设置于衬底上的自旋轨道层、磁化层以及氧化物层。

10、在一种可能的实现方式中,第一连接区域和第二连接区域均包括设置于衬底上的自旋轨道层、磁化层以及金属层。

11、在一种可能的实现方式中,自旋轨道层的材料包括铂、钽、钨以及复合物中的至少一种;其中,该复合物采用包含铂、钽、钨中的一种或者多种的合金或者拓扑绝缘体;磁化层的材料包括钴、铁、镍中的至少一种,或者采用包含钴、铁、镍中至少一种的合金中的一种或多种。

12、在一种可能的实现方式中,磁化层的材料采用磁性复合材料。

13、第二方面,提供了一种逻辑芯片,该逻辑芯片包括设置于衬底上的第一磁畴壁逻辑器件、第二磁畴壁逻辑器件和第三磁畴壁逻辑器件;第一磁畴壁逻辑器件、第二磁畴壁逻辑器件和第三磁畴壁逻辑器件均包括设置在衬底上的第一输入极、第二输入极、第三输入极、输出极和第一连接区域;第一输入极、第二输入极和第三输入极通过第一连接区域与输出极连接;第一输入极、第二输入极或第三输入极的磁化方向经第一连接区域后在输出极输出相反的磁化方向。其中,第二磁畴壁逻辑器件的第三输入极和第三磁畴壁逻辑器件的第三输入极均与第一磁畴壁逻辑器件的第三输入极连接,且第二磁畴壁逻辑器件的第三输入极的自由端与第二磁畴壁逻辑器件的第一连接区域之间具有第二连接区域;第一磁畴壁逻辑器件的输出极的自由端与第一磁畴壁逻辑器件的第一连接区域之间具有第三连接区域;第三磁畴壁逻辑器件的第一输入极与第一磁畴壁逻辑器件的输出极连接;第三磁畴壁逻辑器件的第二输入极与第二磁畴壁逻辑器件的输出极连接,且第三磁畴壁逻辑器件的第二输入极的自由端与第三磁畴壁逻辑器件的第一连接区域之间具有第四连接区域;第三磁畴壁逻辑器件的输出极的自由端与第三磁畴壁逻辑器件的第一连接区域之间具有第五连接区域。其中,第二磁畴壁逻辑器件的第三输入极与第二连接区域之间的具有第一磁化方向;第二连接区域与第二磁畴壁逻辑器件的第一连接区域之间具有与第一磁化方向相反的第二磁化方向;第一磁畴壁逻辑器件的第一连接区域与第三连接区域之间具有第一磁化方向;第一磁畴壁逻辑器件的输出极的自由端与第三连接区域之间具有第二磁化方向;第三磁畴壁逻辑器件的第二输入极的自由端与第四连接区域之间具有第一磁化方向;第三磁畴壁逻辑器件的第一连接区域与第四连接区域之间具有第二磁化方向;第三磁畴壁逻辑器件的第一连接区域与第五连接区域之间具有第一磁化方向;第五连接区域与第三磁畴壁逻辑器件的输出极的自由端之间具有第二磁化方向。

14、基于此,当第一输入极输入0(代表一个磁化方向),第二输入极输入0,第三输入极输入0时,第一磁畴壁逻辑器件输出0,第三磁畴壁逻辑器件的输出极输出0。当第一输入极输入1(代表与0相反的另一个磁化方向),第二输入极输入0,第三输入极输入0时,第一磁畴壁逻辑器件输出0,第三磁畴壁逻辑器件的输出极输出1。当第一输入极输入1,第二输入极输入1,第三输入极输入0时,第一磁畴壁逻辑器件输出1,第三磁畴壁逻辑器件的输出极输出0。当第一输入极输入1,第二输入极输入1,第三输入极输入1时,第一磁畴壁逻辑器件输出1,第三磁畴壁逻辑器件的输出极输出1,从而实现二进制全加器的功能。

15、在一种可能的实现方式中,第一磁化方向以及第二磁化方向均垂直于衬底。此时,第一输入极、第二输入极、第三输入极以及输出极均为面外磁化区域,即磁化方向垂直于各自包含的材料层;第一连接区域、第二连接区域、第三连接区域、第四连接区域和第五连接区域为面内磁化区域,即磁化方向平行于各自包含的材料层。

16、在一种可能的实现方式中,第一输入极、第二输入极、第三输入极以及输出极均包括层叠设置于衬底上的自旋轨道层、磁化层以及氧化物层。

17、在一种可能的实现方式中,第一连接区域、第二连接区域、第三连接区域、第四连接区域和第五连接区域均包括设置于衬底上的自旋轨道层、磁化层以及金属层。

18、在一种可能的实现方式中,自旋轨道层的材料包括铂、钽、钨以及复合物中的至少一种;其中,该复合物采用包含铂、钽、钨中的一种或者多种的合金或者拓扑绝缘体;磁化层的材料包括钴、铁、镍中的至少一种,或者采用包含钴、铁、镍中至少一种的合金中的一种或多种。

19、在一种可能的实现方式中,磁化层的材料采用磁性复合材料。

20、第三方面,提供了一种逻辑芯片,包括设置于衬底上的第一磁畴壁逻辑器件、第二磁畴壁逻辑器件和第三磁畴壁逻辑器件;第一磁畴壁逻辑器件、第二磁畴壁逻辑器件和第三磁畴壁逻辑器件均包括设置在衬底上的第一输入极、第二输入极、第三输入极、输出极和第一连接区域;第一输入极、第二输入极和第三输入极通过第一连接区域与输出极连接;第一输入极、第二输入极或第三输入极的磁化方向经第一连接区域后在输出极输出相反的磁化方向。其中,第二磁畴壁逻辑器件的第一输入极与第三磁畴壁逻辑器件的第一输入极连接;第二磁畴壁逻辑器件的第三输入极与第一磁畴壁逻辑器件的第三输入极连接;第三磁畴壁逻辑器件的第二输入极与第一磁畴壁逻辑器件的输出极连接;第三磁畴壁逻辑器件的第三输入极与第二磁畴壁逻辑器件的输出极连接。

21、其中,第一磁畴壁逻辑器件的第一输入极的自由端与第一磁畴壁逻辑器件的第一连接区域之间具有第二连接区域;第一磁畴壁逻辑器件的第二输入极的自由端与第一磁畴壁逻辑器件的第一连接区域之间具有第三连接区域;第一磁畴壁逻辑器件的第三输入极的自由端与第一磁畴壁逻辑器件的第一连接区域之间具有第四连接区域;第二磁畴壁逻辑器件的第一输入极的自由端与第二磁畴壁逻辑器件的第一连接区域之间具有第五连接区域;第三磁畴壁逻辑器件的第一输入极的自由端与第三磁畴壁逻辑器件的第一连接区域之间具有第六连接区域。其中,第一磁畴壁逻辑器件的第一输入极与第二连接区域之间具有第一磁化方向;第二连接区域与第一磁畴壁逻辑器件的第一连接区域之间具有第二磁化方向;第一磁畴壁逻辑器件的第二输入极与第三连接区域之间具有第一磁化方向;第三连接区域与第一磁畴壁逻辑器件的第一连接区域之间具有第二磁化方向;第一磁畴壁逻辑器件的第三输入极的自由端与第五区域之间具有第一磁化方向;第四区域与第一磁畴壁逻辑器件的第一连接区域之间具有第二磁化方向;第二磁畴壁逻辑器件的第一输入极的自由端与第五连接区域之间具有第一磁化方向;第五连接区域与第二磁畴壁逻辑器件的第一连接区域之间具有第二磁化方向;第三磁畴壁逻辑器件的第一输入极的自由端与第六连接区域之间具有第一磁化方向;第六连接区域与第三磁畴壁逻辑器件的第一连接区域之间具有第二磁化方向。

22、基于此,当第一输入极输入0(代表一个磁化方向),第二输入极输入0,第三输入极输入0时,第一磁畴壁逻辑器件输出0,第三磁畴壁逻辑器件的输出极输出0。当第一输入极输入1(代表与0相反的另一个磁化方向),第二输入极输入0,第三输入极输入0时,第一磁畴壁逻辑器件输出0,第三磁畴壁逻辑器件的输出极输出1。当第一输入极输入1,第二输入极输入1,第三输入极输入0时,第一磁畴壁逻辑器件输出1,第三磁畴壁逻辑器件的输出极输出0。当第一输入极输入1,第二输入极输入1,第三输入极输入1时,第一磁畴壁逻辑器件输出1,第三磁畴壁逻辑器件的输出极输出1,从而实现二进制全加器的功能。

23、在一种可能的实现方式中,第一磁化方向以及第二磁化方向均垂直于衬底。

24、在一种可能的实现方式中,第一输入极、第二输入极、第三输入极以及输出极均包括层叠设置于衬底上的自旋轨道层、磁化层以及氧化物层。

25、在一种可能的实现方式中,第一连接区域、第二连接区域、第三连接区域、第四连接区域、第五连接区域和第六连接区域均包括设置于衬底上的自旋轨道层、磁化层以及金属层。

26、在一种可能的实现方式中,第五连接区域和第六连接区域为同一个连接区域。基于此,可以在实现相同功能的同时进一步降低芯片的尺寸。

27、在一种可能的实现方式中,自旋轨道层的材料包括铂、钽、钨以及复合物中的至少一种;其中,该复合物采用包含铂、钽、钨中的一种或者多种的合金或者拓扑绝缘体;磁化层的材料包括钴、铁、镍中的至少一种,或者采用包含钴、铁、镍中至少一种的合金中的一种或多种。

28、在一种可能的实现方式中,磁化层的材料采用磁性复合材料。

29、第四方面,提供了一种电子设备,该电子设备包括电路板以及与电路板连接的逻辑芯片,其中逻辑芯片为上述第一方面至第四方面中任一种可能的实现方式中的逻辑芯片。

- 还没有人留言评论。精彩留言会获得点赞!