一种半导体结构及其制作方法与流程

本公开实施例涉及半导体领域,特别涉及一种半导体结构及其制作方法。

背景技术:

1、随着半导体市场需求的不断增长,半导体存储器技术迅速发展,特别是动态随机存储器dram(dynamic random access memory)在存储器市场中,占据了最为主要的位置。常见的dram单元由一个晶体管(transistor)和一个电容器(capacitor)构成1t1c结构,为了提高单元性能并缩小单元面积,需要在单位面积上制备大电容值的电容器。

2、随着对dram单元的存储性能和单元尺寸提出越来越高的要求,给1t1c单元带来了严峻的挑战。研究表明,晶体管在一定的尺寸以及适当的掺杂剂下,也可以在不需要任何电容的情况下容纳少量的电荷,因为,晶体管的栅极是一个天然的电容。通过形成2t0c嵌入式dram结构,制作出两个晶体管且没有电容的结构,因此有必要提供一种新的2t0c的dram结构。

技术实现思路

1、本公开实施例提供一种半导体结构及其制作方法,至少可以提供一种新的2t0c的dram结构。

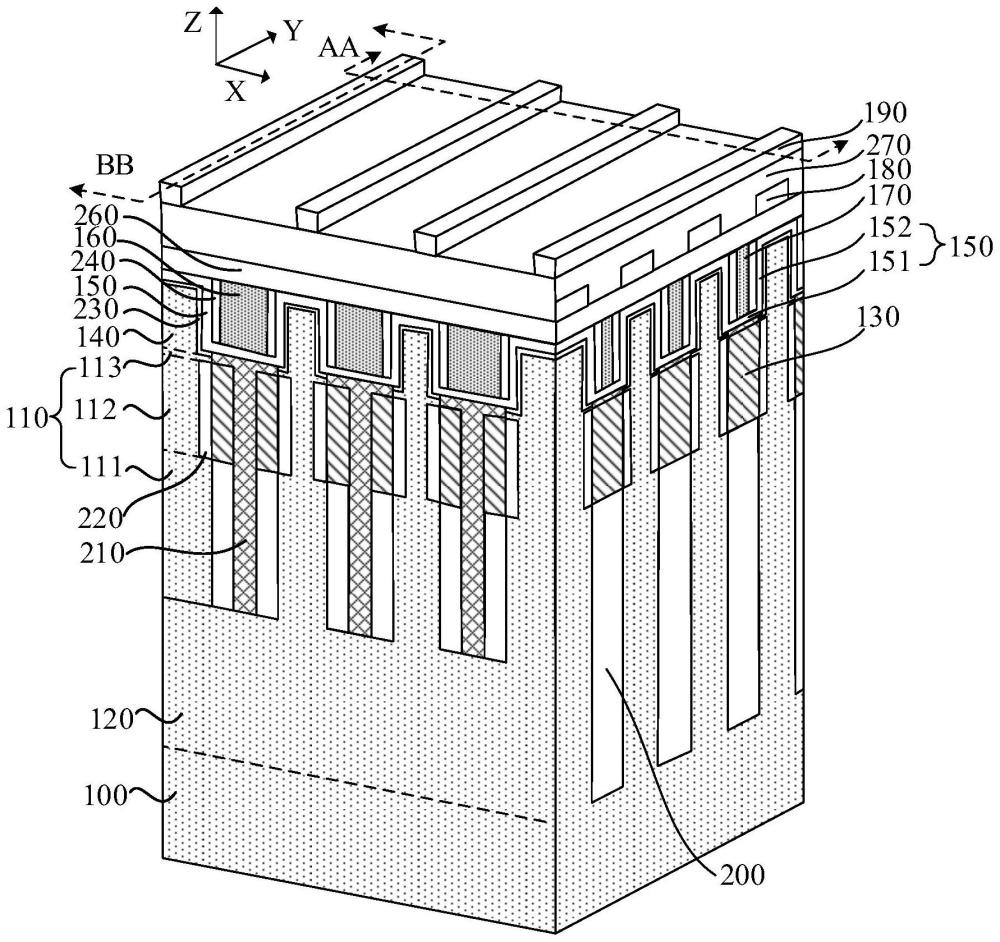

2、根据本公开一些实施例,本公开实施例一方面提供一种半导体结构,包括:基底以及位于所述基底上的多个沿第一方向以及第二方向间隔排布的半导体通道,所述半导体通道包括沿第三方向依次排布的第一掺杂区、沟道区以及第二掺杂区,每一所述半导体通道用于构成第一晶体管;多条沿所述第一方向延伸且沿所述第二方向间隔排布的第一位线,所述第一位线位于所述基底与所述半导体通道之间,每一所述第一位线与沿所述第一方向排布的所述第一掺杂区相接触;多条沿所述第二方向延伸且沿所述第一方向间隔排布的第一字线,所述第一字线环绕所述沟道区;栅导电层,所述栅导电层与所述第二掺杂区相接触,且位于所述第二掺杂区远离所述沟道区的一侧;沟道层,所述沟道层环绕所述栅导电层的外侧面设置;第一半导体掺杂层和第二半导体掺杂层,所述第一半导体掺杂层与所述第二半导体掺杂层设置在所述沟道层的外侧面,且所述第一半导体掺杂层与所述第二半导体掺杂层相间隔,所述第一半导体掺杂层、所述第二半导体掺杂层、所述沟道层以及所述栅导电层用于构成第二晶体管;第二位线,所述第二位线与所述第一半导体掺杂层或所述第二半导体掺杂层中的一者电连接;第二字线,所述第二字线与所述第一半导体掺杂层或所述第二半导体掺杂层中的另一者电连接。

3、在一些实施例中,所述半导体结构还包括:第一栅介质层,所述第一栅介质层环绕所述栅导电层的表面,且与所述栅导电层接触;所述沟道层环绕所述第一栅介质层的表面,且与所述第一栅介质层接触;第一隔离层,所述第一隔离层环绕所述沟道层的部分表面,且与所述沟道层接触。

4、在一些实施例中,还包括:第二隔离层,所述第二隔离层位于相邻的所述第一半导体掺杂层与相邻所述第二半导体掺杂层之间。

5、在一些实施例中,所述第一隔离层与所述第二隔离层的材料不同。

6、在一些实施例中,所述沟道层掺杂有第一掺杂离子,所述第一半导体掺杂层具有第二掺杂离子,所述第一掺杂离子的离子类型与所述第二掺杂离子的离子类型不同。

7、在一些实施例中,所述栅导电层与所述半导体通道为一体式结构。

8、在一些实施例中,所述沟道区包括平坦部和凸出部,所述凸出部环绕所述栅导电层,所述平坦部与所述凸出部相连,所述第一半导体掺杂层设置在所述凸出部沿所述第一方向或所述第二方向中一者排布的外侧面,与所述平坦部的顶面接触连接,所述第二半导体掺杂层设置在所述凸出部沿所述第一方向或所述第二方向中另一者排布的外侧面,与所述平坦部的顶面接触连接。

9、在一些实施例中,在所述第一方向上,所述栅导电层的宽度小于所述第二掺杂区的所述半导体通道的宽度。

10、在一些实施例中,所述第一半导体掺杂层沿所述第一方向排布,在所述第一方向上相邻的两个所述栅导电层与同一所述第一半导体掺杂层连接。

11、在一些实施例中,还包括:保护层,所述保护层覆盖所述沟道层的顶面、所述第一半导体掺杂层的部分表面及所述第二半导体掺杂层的部分表面,所述第二位线贯穿所述保护层与所述第一半导体掺杂层或所述第二半导体掺杂层中的一者接触连接,所述第二字线贯穿所述保护层与所述第一半导体掺杂层或所述第二半导体掺杂层中的另一者接触连接。

12、根据本公开一些实施例,本公开实施例另一方面还提供一种半导体结构的制作方法,包括:提供基底;形成位于所述基底上的多个沿第一方向以及第二方向间隔排布的半导体通道及栅导电层,所述半导体通道包括沿第三方向依次排布的第一掺杂区、沟道区以及第二掺杂区,每一所述半导体通道用于构成第一晶体管,所述栅导电层与所述第二掺杂区相接触,且位于所述第二掺杂区远离所述沟道区的一侧;形成多条沿所述第一方向延伸且沿所述第二方向间隔排布的第一位线,所述第一位线位于所述基底与所述半导体通道之间,每一所述第一位线与沿所述第一方向排布的所述第一掺杂区相接触;形成多条沿所述第二方向延伸且沿所述第一方向间隔排布的第一字线,所述第一字线环绕所述沟道区;形成沟道层,所述沟道层环绕所述栅导电层的外侧面设置;形成第一半导体掺杂层和第二半导体掺杂层,所述第一半导体掺杂层与所述第二半导体掺杂层设置在所述沟道层的外侧面,且所述第一半导体掺杂层与所述第二半导体掺杂层相间隔,所述第一半导体掺杂层、所述第二半导体掺杂层、所述沟道层以及所述栅导电层用于构成第二晶体管;形成第二位线,所述第二位线与所述第一半导体掺杂层或所述第二半导体掺杂层中的一者接触连接;形成第二字线,所述第二字线与所述第一半导体掺杂层或所述第二半导体掺杂层中的另一者接触连接。

13、在一些实施例中,形成所述半导体通道及所述栅导电层的方法包括:形成初始半导体通道,所述初始半导体通道位于所述基底上,且沿所述第一方向及所述第二方向间隔排布,所述初始半导体通道包括沿所述第三方向依次排布的所述第一掺杂区、所述沟道区以及第二初始掺杂区;刻蚀部分所述第二初始掺杂区,以形成第二掺杂区及栅导电层。

14、在一些实施例中,形成所述沟道层之前还包括:形成第一栅介质层,所述第一栅介质层环绕所述栅导电层的表面,且与所述栅导电层接触;形成所述沟道层之后还包括:形成第一隔离层,所述第一隔离层环绕所述沟道层的表面,且与所述沟道层接触。

15、在一些实施例中,所述沟道层包括平坦部和凸出部,所述凸出部环绕所述栅导电层,所述平坦部与所述凸出部相连,形成所述第一隔离层的方法包括:形成第一初始隔离层,所述第一初始隔离层覆盖所述沟道层的整个表面;刻蚀所述第一初始隔离层,以暴露所述凸出部的顶面及所述平坦部的顶面,剩余所述第一初始隔离层作为所述第一隔离层。

16、在一些实施例中,形成所述第一半导体掺杂层及所述第二半导体掺杂层的方法包括:形成初始掺杂层,所述初始掺杂层覆盖所述第一隔离层及所述沟道层的表面;刻蚀所述初始掺杂层,以暴露所述第一隔离层及所述沟道层的顶面,剩余所述初始掺杂层作为掺杂层;刻蚀所述掺杂层,以形成凹槽,所述凹槽暴露部分所述第一隔离层的侧壁及所述平坦部的顶面,剩余所述掺杂层作为所述第一半导体掺杂层及所述第二半导体掺杂层。

17、在一些实施例中,刻蚀所述掺杂层的方法包括:形成掩膜层,所述掩膜层覆盖所述掺杂层的顶面,且所述掩膜层包括目标图案,所述目标图案的长度等于在所述第一方向上相邻所述第一隔离层之间的间距,所述目标图案的宽度等于在所述第二方向上相邻的所述第一隔离层之间的间距;以掩膜层为掩膜刻蚀所述掺杂层,以形成所述第一半导体掺杂层及所述第二半导体掺杂层。

18、在一些实施例中,刻蚀所述掺杂层的方法包括:采用自对准工艺刻蚀所述掺杂层,以形成初始凹槽,所述初始凹槽贯穿所述掺杂层;采用过刻蚀的方式在刻蚀所述初始凹槽内刻蚀所述掺杂层,以形成所述凹槽、所述第一半导体掺杂层及所述第二半导体掺杂层。

19、在一些实施例中,还包括:形成第二隔离层,所述第二隔离层位于相邻的所述第一半导体掺杂层与相邻所述第二半导体掺杂层之间。

20、本公开实施例提供的技术方案至少具有以下优点:通过设置半导体通道用于构成第一晶体管,通过第一位线与第一掺杂区接触连接,通过第一字线环绕沟道区,以实现控制第一晶体管的关断,并向第二晶体管的栅导电层输送并存储电荷,通过栅导电层与第二掺杂区相接触从而可以接收来自第一晶体管的电荷,通过栅导电层、沟道层、第一半导体掺杂层和第二半导体掺杂层构成第二晶体管,以形成2t0c的dram结构,通过第二位线与第一半导体掺杂层或第二半导体掺杂层的一者接触,第二字线与第一半导体掺杂层或第二半导体掺杂层的另一者接触,可以实现对整个半导体结构的读取功能,本公开实施例通过采用晶体管代替电容的方式可以降低整个生产工艺的制作难度,且本公开实施例提供的2t0c的dram结构具有更高的集成密度。

- 还没有人留言评论。精彩留言会获得点赞!