半导体结构及其制作方法、存储器与流程

本公开实施例涉及半导体,涉及但不限于一种半导体结构及其制作方法、存储器。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)是一种半导体存储器,主要的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(bit)是1还是0。dram的研制过程中,随着尺寸的微缩进一步,垂直电容结构遇到的瓶颈开始出现。为了实现电容单位密度的提升,堆叠式电容开始出现。采用双向刻蚀dram源极与漏极的方式定义出的栅极结构容易具有不规则的形状,而dram器件的性能、品质均与栅极结构的规则性相关,如何控制对dram器件中的源极与漏极的刻蚀形成具有目标形状的栅极结构,成为了亟需解决的问题。

技术实现思路

1、有鉴于此,本公开实施例提供一种半导体结构及其制作方法、存储器。

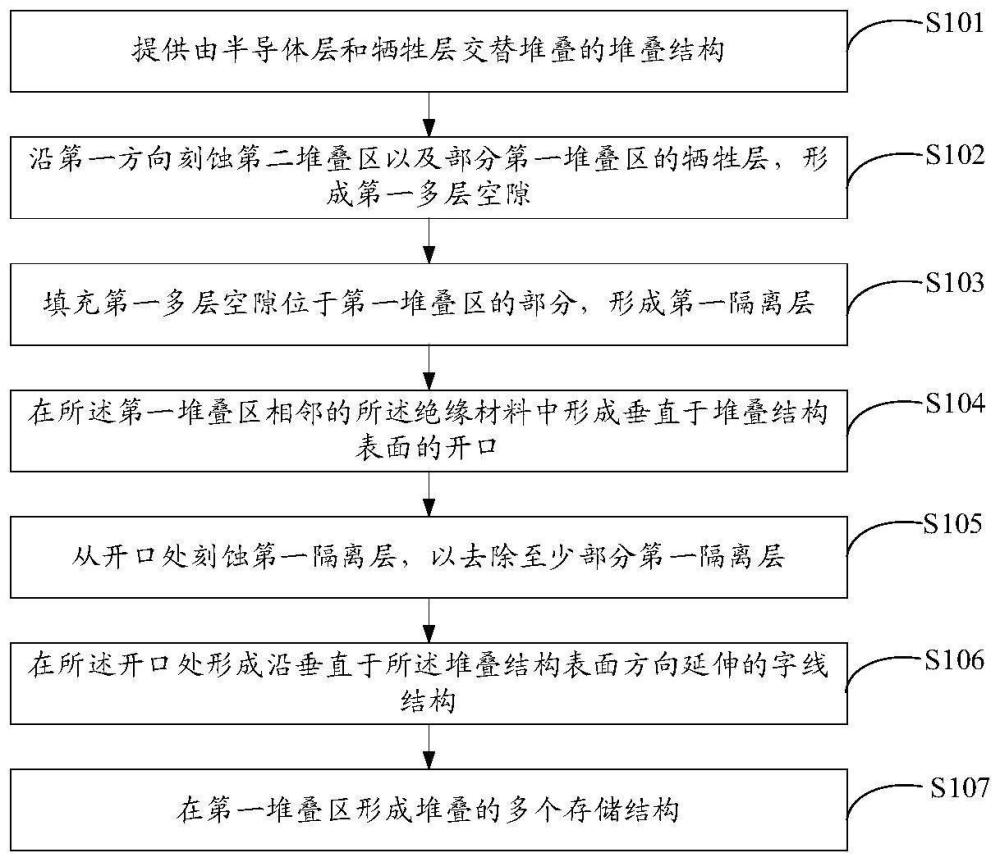

2、第一方面,本公开实施例提供一种半导体结构的制作方法,所述方法包括:

3、提供由半导体层和牺牲层交替堆叠的堆叠结构;所述堆叠结构包括沿第一方向延伸的若干条第一堆叠区,以及连接在多条所述第一堆叠区的第一端,且沿第二方向延伸的第二堆叠区;其中,所述第一方向与所述第二方向垂直;所述第一堆叠区之间填充有绝缘材料;

4、沿所述第一方向刻蚀所述第二堆叠区以及部分所述第一堆叠区的所述牺牲层,形成第一多层空隙;所述第二堆叠区的所述半导体层用于形成多个堆叠的位线结构;

5、填充所述第一多层空隙位于所述第一堆叠区的部分,形成第一隔离层;

6、在所述第一堆叠区相邻的所述绝缘材料中形成垂直于所述堆叠结构表面的开口;

7、从所述开口处刻蚀所述第一隔离层,以去除至少部分所述第一隔离层;

8、在所述开口处形成沿垂直于所述堆叠结构表面方向延伸的字线结构;

9、在所述第一堆叠区形成堆叠的多个存储结构。

10、在一些实施例中,所述牺牲层所用的牺牲层材料与半导体层所用的半导体材料的刻蚀选择比大于或等于第一预设值。

11、在一些实施例中,所述牺牲层材料为锗化硅sige,所述半导体材料为硅si。

12、在一些实施例中,所述填充所述第一多层空隙位于所述第一堆叠区的部分,形成第一隔离层,包括:

13、沿所述第一方向,向所述第一多层空隙中依次填充第一隔离材料、第二隔离材料以及所述第一隔离材料,形成所述第一隔离层;其中,所述第一隔离层沿所述第一方向的长度大于或等于所述第一多层空隙位于所述第一堆叠区内的长度。

14、在一些实施例中,所述第二隔离材料与所述第一隔离材料的刻蚀选择比大于或等于第二预设值。

15、在一些实施例中,所述向所述第一多层空隙中依次填充第一隔离材料、第二隔离材料以及所述第一隔离材料,形成所述第一隔离层,包括:

16、向所述第一多层空隙中填充第一隔离材料;

17、刻蚀所述第一隔离材料,且保留位于所述第一堆叠区的部分所述第一隔离材料;

18、向所述第一多层空隙中填充第二隔离材料;

19、刻蚀所述第二隔离材料,且保留位于所述第一堆叠区的部分所述第二隔离材料;其中,沿所述第一方向,保留的所述第二隔离材料的长度为预定的栅极长度;

20、再次向所述第一多层空隙中填充所述第一隔离材料;

21、刻蚀所述第一隔离材料,且保留位于所述第一堆叠区的部分且位于所述第二隔离材料外的所述第一隔离材料。

22、在一些实施例中,所述从所述开口处刻蚀所述第一隔离层,以去除至少部分所述第一隔离层,包括:

23、从所述开口处刻蚀所述第一隔离层,以去除所述第一隔离层中的所述第二隔离材料。

24、在一些实施例中,所述在所述开口处形成沿垂直于所述堆叠结构表面方向延伸的字线结构,包括:

25、在所述开口内的各层所述半导体层的表面形成栅极氧化层;

26、在所述栅极氧化层表面覆盖第一导电材料作为栅极导电层;

27、在覆盖有所述栅极导电层的开口内填充第二导电材料,形成所述字线结构。

28、在一些实施例中,所述提供由半导体层和牺牲层交替堆叠的堆叠结构,包括:

29、提供衬底;

30、在所述衬底上依次交替堆叠半导体材料和牺牲层材料;

31、沿所述第一方向刻蚀堆叠的所述半导体材料和牺牲层材料,形成沿所述第一方向延伸的若干条所述第一堆叠区,以及连接在多条所述第一堆叠区的第一端,且沿所述第二方向延伸的所述第二堆叠区;所述堆叠结构以外的区域为刻蚀形成的凹槽;

32、在刻蚀后形成的凹槽内填充所述绝缘材料。

33、在一些实施例中,所述方法还包括:

34、在所述第一堆叠区远离所述第二堆叠区的第二端,刻蚀所述绝缘材料形成位于相邻的所述第一堆叠区之间的开槽;

35、在所述开槽内填充隔离材料;

36、去除所述第二端远离第一端的一侧的所述绝缘材料,并从所述第二端沿第一方向刻蚀所述第一堆叠区中的部分牺牲层,形成第二多层空隙;

37、在刻蚀掉部分所述牺牲层的所述第一堆叠区的所述第二端填充所述隔离材料,形成支撑结构。

38、在一些实施例中,所述在每条所述第一堆叠区形成堆叠的多个存储结构,包括:

39、去除所述第一堆叠区之间的所述绝缘材料;

40、去除所述第一堆叠区中的所述牺牲层,使各层所述半导体层悬空;

41、在所述半导体层的表面进行金属硅化处理;

42、在金属硅化处理后的所述半导体层表面覆盖第一金属材料,形成电容结构的下电极;

43、在所述下电极的表面覆盖介电层;

44、在所述介电层的表面覆盖第三金属材料,形成所述电容结构的上电极;

45、在形成有所述上电极的各相邻半导体层之间的空隙内以及各第一堆叠区之间的凹槽内填充多晶硅材料。

46、在一些实施例中,在形成堆叠的多个电容结构之后,所述方法还包括:

47、去除所述第一堆叠区的所述第二端的隔离材料,并同时去除所述电容结构靠近所述第一端一侧的至少部分所述第一隔离层,形成位于所述电容结构两端的沟槽;

48、在所述沟槽中填充绝缘材料。

49、在一些实施例中,在形成所述第一隔离层之后,所述方法还包括:

50、在所述第二堆叠区沿第二方向对未被所述第一隔离层覆盖的所述半导体层进行金属硅化处理;

51、在所述半导体层的表面覆盖第二金属材料;

52、刻蚀各层所述半导体层沿z方向之间连接处的所述第二金属材料,使各层所述半导体层覆盖的第二金属材料之间相互分离;

53、在各层覆盖有所述第二金属材料的半导体层之间以及所述第二堆叠区远离第一堆叠区的一侧填充绝缘材料;其中,各层覆盖有所述第二金属材料的半导体层为所述位线结构。

54、在一些实施例中,所述方法还包括:

55、对所述位线结构进行处理,形成长度由下到上依次递减的台阶结构;

56、在每层所述台阶结构上形成位线引出结构。

57、第二方面,本公开实施例还提供一种半导体结构,所述半导体结构如上述实施例任一所述的方法形成。

58、第三方面,本公开实施例还提供一种存储器,包括:

59、如上述实施例任一所述的方法形成的半导体结构。

60、本公开实施例通过从侧面单向刻蚀的工艺,在形成aa(active area,有源区)区域之后,从一端单向刻蚀中间层,并填上不同隔离材料,定义出晶体管的源极、漏极以及沟道的长度和范围。如此,可以减少对源极与漏极进行双向侧面刻蚀导致的栅极结构不规则问题。

- 还没有人留言评论。精彩留言会获得点赞!