半导体中芯片到芯片互连的架构的制作方法

本发明总体涉及半导体器件。更具体地,本发明涉及不同半导体芯片之间的芯片到芯片互连。

背景技术:

1、芯片到芯片互连是在组装成一个模块的两个不同半导体芯片之间提供数据通信的功能块。在pcb、pcb基板、ic、光子ic和需要数据通信互连的其他组件中也可能需要互连。芯片到芯片互连创建了两个芯片之间的连接,以实现最大功率传输和超高带宽传输。芯片到芯片互连通常由在两个芯片上的连接焊盘之间提供无缝连接的不同控制块组成。这使用高速架构或高密度并行架构实现,高速架构或高密度并行架构被优化以支持多种先进的2d、2.5d和3d封装技术。

2、芯片到芯片互连是单片soc设计和多芯片soc设计中行业趋势的关键结构。这种方法减轻了对小型工艺节点的高成本/低产量日益增长的担忧,并提供了附加的产品模块性和灵活性。

3、为了实现良好的芯片到芯片互连,需要传输线以实现最大功率传输和超高带宽传输。可以通过广义集总元件来对传输线建模。传输线的广义集总元件模型可用于计算特性阻抗、相位速度以及传播常数的两个部分(相位和衰减)。如图21所示,该模型使用具有四个元件的传输线的无限小部分。这里的串联电阻、串联电感、并联电导和并联电容都按每单位长度归一化(用“上撇号”符号表示)。

4、l=每单位长度串联电感,单位为h/m,表示导体的总自感。

5、c=每单位长度并联电容,单位为f/m,表示由于导体极为靠近而导致的电容。

6、r=每单位长度串联电阻,单位为ω/m,表示由于导体的有限电导率而导致的电阻率损失。

7、g=每单位长度并联电导,单位为s/m,表示材料的介电损耗。

8、对于无损传输线,可以忽略串联电阻和并联电导。该模型可以简化为lc连接。lc连接形成切断高频信号的lc低通滤波器并限制传输带宽。同时,在lc连接中需要阻抗匹配,以最小化信号反射或最大化功率传输。在dc电路中,源和负载应该相等。在ac电路中,源应该等于负载或负载的复共轭,取决于目标。

9、这两个问题主导了互连的通信性能。

10、pcb通常使用两种类型的传输线:微带线和带状线。传输线中的每一种由信号迹线和(多个)参考平面组成。基于传输线几何形状,必须将信号迹线和参考平面假设为一个单元。并且,永远不要将信号迹线和参考平面分开,因为微带线和带状线具有它们独特的em场分布,这些em场分布定义了它们的属性。可以通过选择pcb材料(介电常数和损耗角正切)以及调整导波波长、传播速度和特性阻抗来改变微带线传输线和带状线传输线的em场分布。这些参数最终改变em场分布,从而改变传输线的属性。

11、在当前的封装技术中,引线接合是在两个芯片之间进行互连的最常用方法之一。au线或cu线是最常见的接合引线,通过使用超声波能量或热超声能量将其附接到引线接合焊盘上。这形成了良好的粘附并在接合引线和接合焊盘之间形成欧姆接触。然而,由于接合引线之间的电介质是空气并且线到线的距离是固定的,这意味着两条接合引线之间的电容通常是固定的。这限制了信号带宽,并且很难在源和负载之间进行良好的阻抗匹配。一般而言,引线接合技术提供高度的互连灵活性,但阻抗匹配较差。此外,在引线接合解决方案中,引线直径受到接合焊盘的尺寸的限制。此外,为了构建不同的架构,例如段差或用于两个芯片之间的倾斜接合,在组装工艺中将使用稍长一点的引线用于两个芯片之间的倾斜接合。

12、在需要高标准规范的先进技术中,将使用硅桥来建立互连。在硅桥设计中,通常将电介质固定为sio2,这意味着固定的介电常数。需要仔细设计迹线宽度以获得良好的阻抗匹配迹线。硅桥接合工艺需要倒装芯片接合工艺,这意味着在两个芯片之间需要非常严格的厚度要求。一般而言,硅桥互连提供良好的阻抗匹配互连,但它受到严格的倒装芯片接合工艺的影响。迹线宽度受到硅桥中的焊盘的间距的限制。

13、此外,由于制造工艺,硅桥为矩形。因此,倒装芯片工艺需要非常严格的高度要求。如果两个芯片之间有段差,则接合可能会打开。

14、在上述两种方法中,都经受产量损失问题。因为这两种方法都不利于再加工。接合焊盘容易被引线接合工艺或倒装芯片工艺损坏。

15、因此,需要两个芯片之间的互连,该互连为阻抗匹配要求提供灵活性,并避免产量损失问题。

16、发明目的

17、本发明的一个目的是在两个半导体芯片之间建立互连,该互连为阻抗匹配要求提供灵活性。

18、本发明的一个目的是在两个半导体芯片之间建立互连,该互连对迹线宽度选择没有限制。

19、本发明的一个目的是在两个半导体芯片之间建立互连,该互连有利于非破坏性再加工工艺。

20、本发明的另一个目的是在组装工艺中处理不同架构,例如两个芯片之间的分段(stepping)和倾斜问题。

21、本发明的另一个目的是提供类似的阻抗匹配性能,同时具有比硅桥更低的封装要求。

22、本发明的又一目的是在两个半导体芯片之间建立互连,该互连成本低、具有良好的阻抗匹配并且是可再加工的和灵活的。

23、为进一步阐明本发明的优点和特征,将参考附图中所示的具体实施例对本发明进行更详细的描述。可以理解,这些附图仅描绘了本发明的典型实施例,因此不应被视为限制其范围。

技术实现思路

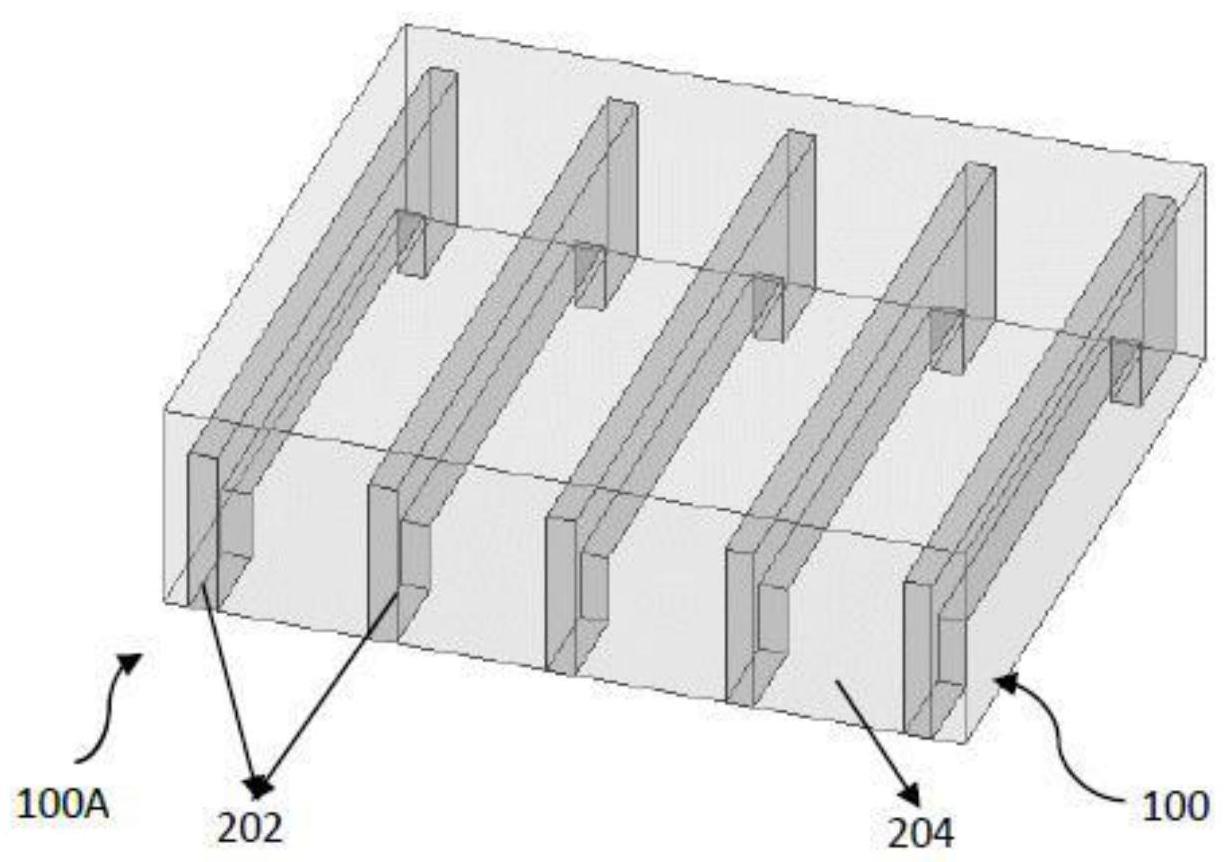

1、本发明的一个方面提供了一种pcb桥,用于两个或更多个半导体芯片的互连以在半导体芯片之间进行数据通信,包括:多个金属带,其中每个金属带一个接一个地对齐,每个金属带具有两个腿部或连接器以与半导体芯片上的连接焊盘接触和连接,并且其中使用切割技术将每个金属带的两个腿部或连接器的形状和尺寸切割成彼此相同或不同;以及介电材料,其设置在多个金属带之间,其中,在半导体模块中在垂直方向上使用pcb桥,用于两个或更多个半导体芯片的互连,其中,通过调整pcb桥的介电材料和迹线宽度,pcb桥的垂直方向提供柔性的阻抗匹配,其中,通过将阻抗与源匹配,pcb桥的垂直方向避免信号反射,以及其中,pcb桥的迹线长度受到两个半导体芯片之间的间距的限制,这进一步限制了pcb桥的迹线的电感。

2、本发明的一个实施例提供了多个金属带由铜制成,介电材料为预浸料,并且pcb桥的垂直布置提供了无限的迹线宽度,无限的迹线宽度进一步提高了阻抗匹配的灵活性。

3、本发明的一个实施例提供了介电材料具有范围为2-5的介电常数。

4、本发明的另一个实施例提供了pcb桥使用激光切割技术切割金属带的腿部或连接器制造,以通过改变激光切割图案来提供规则的或不规则的形状和尺寸。

5、本发明的一个实施例提供了具有金属带的腿部或连接器的灵活形状和尺寸的pcb桥通过使金属带的一个腿部或连接器长于金属带的其它腿部或连接器来补偿半导体模块中的段梯差问题。

6、本发明的又一个实施例提供了具有金属带的腿部或连接器的灵活形状和尺寸的pcb桥通过在激光切割技术期间制作激光切割图案的同时使pcb面板倾斜来补偿半导体模块中的倾斜问题。

7、本发明一个实施例提供了pcb桥被制造为全屏蔽带状线pcb桥结构,其中除了包括多个金属带和设置在多个金属带之间的介电材料之外,全屏蔽带状线pcb桥结构进一步包括在全屏蔽带状线pcb桥结构的顶部和底部的一个或多个金属沉积层;并且其中,全屏蔽带状线pcb桥结构形成电磁场屏障,因为全屏蔽带状线pcb桥结构被顶部和底部的金属沉积层以及介电材料的中间填充物所屏蔽,全屏蔽带状线pcb桥结构阻挡来自空间的噪声干扰。

8、本发明一个实施例提供了pcb桥被制造为在顶部具有外部组件的带状线pcb桥结构,其中除了包括多个金属带和设置在多个金属带之间的介电材料之外,在顶部具有外部元件的带状线pcb桥结构还包括在pcb桥的顶部的外部组件,并且其中,外部组件为电感器、电容器、电阻器或铁氧体磁珠中的至少一种。

9、本发明的另一个实施例提供了pcb桥被制造为带状线扇出型pcb桥结构,其中除了包括多个金属带和设置在多个金属带之间的介电材料之外,带状线扇出型pcb桥结构还包括在多个金属带之间的连接多个金属带中每两个金属带的导电材料,并且其中,带状线扇出型pcb桥结构具有两种间距,一种间距为‘p’,另一种为间距‘p’的两倍。

10、本发明的另一个实施例提供了pcb桥被制造为具有嵌入式单层电容器的带状线扇出型pcb桥结构,其中除了包括多个金属带和设置在多个金属带之间的介电材料之外,具有嵌入式单层电容器的带状线扇出型pcb桥结构还包括在多个金属带之间的连接多个金属带中每两个金属带的导电材料,以及嵌入在两个金属带之间的单层电容器。

11、本发明的又一个实施例提供了pcb桥被制造为具有嵌入式多层电容器的带状线扇出型pcb桥结构并作为接地层,其中除了包括多个金属带和设置在多个金属带之间的介电材料之外,具有嵌入式多层电容器的带状线扇出型pcb桥结构还包括将所有多个金属带在其端部连接在一起的导电材料。

12、本发明的另一个实施例提供了pcb桥被制造为作为信号层的具有嵌入式多层电容器的带状线扇出型pcb桥结构,其中除了包括多个金属带和设置在多个金属带之间的介电材料之外,具有嵌入式多层电容器的带状线扇出型pcb桥结构还包括将多个金属带中的交替的金属带在其端部连接的导电材料。

13、本发明的一个实施例提供了除了2d布置之外,在单个半导体模块中pcb桥以3d布置互连两个以上半导体芯片,其中在3d布置中pcb桥中的多个金属带包括成对金属带,其中成对金属带一个接一个地对齐,成对金属带中的每个金属带堆叠在另一个之上,并且成对金属带中的每个金属带具有两个腿部或连接器以与3d布置中的半导体芯片接触和连接;并且其中,3d布置是包括互连至少四个半导体芯片的pcb桥的3d堆叠结构,其中四个半导体芯片中的两个彼此堆叠,另外两个彼此堆叠,并且然后通过在pcb桥中在pcb桥的垂直方向上的堆叠并对齐的成对金属带将堆叠的两个半导体芯片与堆叠的其他两个半导体芯片互连。

14、本发明的另一个实施例提供了至少两个这样的pcb桥堆叠在一起并形成独立的交叉连接,以形成用于连接两个不同信号的3d交叉结构,该3d交叉结构适用于用在具有两个独立的连接的空间受限的设计中。

15、本发明的一个实施例提供了除了2d布置,在单个半导体模块中至少两个这样的pcb桥也在3d扇出交叉结构中互连两个以上半导体芯片,其中3d扇出交叉结构包括至少两个pcb桥并用于将芯片信号扇出成三路,其中,至少两个pcb桥堆叠在一起以形成扇出交叉连接,至少两个pcb桥互连至少四个半导体芯片,其中四个半导体芯片中的至少两个彼此相对,四个半导体芯片中的另外两个彼此相对,形成扇出结构,其中,至少两个pcb桥中之一的金属带和/或腿部或连接器通过连接节点与四个半导体芯片中的至少一个连接,并且其中,至少两个pcb桥在垂直方向上以互连至少四个半导体芯片。

16、本发明的一个方面提供了一种制造pcb桥的方法,pcb桥用于两个或更多个半导体芯片的互连以在半导体芯片之间进行数据通信,包括:将pcb面板固定在pcb的拐角处的一个或多个面板固定装置处;绘制激光切割线以标记pcb桥的多个金属带,其中每个金属带具有两个腿部或连接器以与半导体芯片上的连接焊盘接触和连接,并且其中每个金属带的两个腿部或连接器的形状和尺寸被绘制成彼此相同或不同以解决半导体组装问题,半导体组装问题包括段差问题和倾斜问题;沿着绘制的激光切割线进行激光切割以制造用于pcb桥的多个金属带;将切割的多个金属带一个接一个地对齐;以及在多个金属带之间设置介电材料以制造pcb桥;并且其中,在半导体组装中在垂直方向上使用pcb桥,互连两个或更多个半导体芯片,其中,通过调整pcb桥的介电材料和迹线宽度,pcb桥的垂直方向提供灵活的阻抗匹配,其中,通过将阻抗与源匹配,pcb桥的垂直方向避免信号反射,以及其中,pcb桥的迹线长度受到两个半导体芯片之间的间距的限制,这进一步限制了pcb桥的迹线的电感。

- 还没有人留言评论。精彩留言会获得点赞!