接口装置及其信号收发方法与流程

本发明涉及一种接口装置及其信号收发方法,且尤其是涉及一种可减低电路布局面积以及功率消耗的接口装置及其信号收发方法。

背景技术:

1、在现有技术领域中,在存储器电路的物理层中,常需要时钟树电路来产生用以取样资信号的时钟信号。而基于传输过程所产生的传输延迟,在三维堆栈的半导体组件中,在主、从电路间传输的数据信号会与时钟信号间产生不对齐(align)的现象。在这样的情况下,常需要在数据信号的传输路径间,加入延迟串以调整数据信号的传输时间,以与时钟信号可以对齐。

2、然而,基于数据信号常具有多个位,在这样的条件下,在主、从电路间常需要设置大量的延迟串而耗去大量的布局面积。并且,当数据信号发生转态时,这些延迟串也会因为数据信号的转态而产生不必要的功率消耗,降低半导体组件的工作效能。

技术实现思路

1、本发明是针对一种接口装置及其信号的收发方法,可有效减低电路的面积以及所需要的功率消耗。

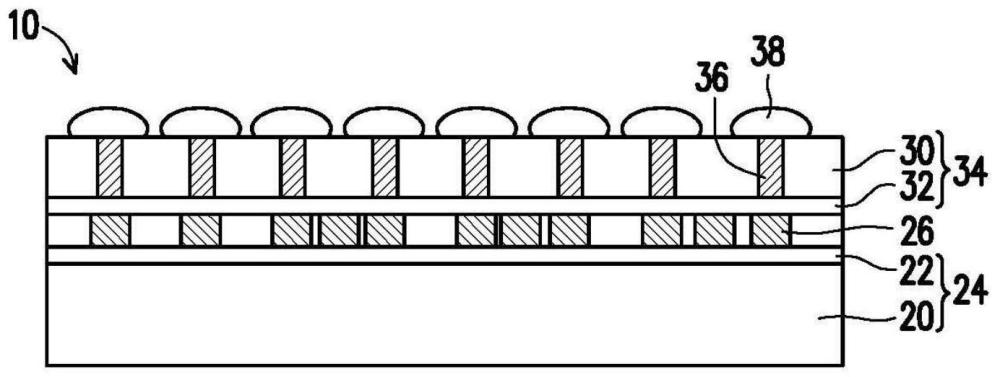

2、根据本发明的实施例,接口装置适用于一半导体装置。半导体装置包括主装置以及多个从装置,其中主装置以及从装置通过电性连接以堆栈成一三维结构。接口装置包括主电路以及从电路。主电路设置在主装置中。从电路设置在各从装置中,通过多个硅穿孔耦接至主电路。从电路包括第一可程式延迟串、第一输出时钟产生器以及第一相位检测器。第一可程式延迟串根据第一调整信号以提供第一调整延迟量,根据第一调整延迟量以延迟第一时钟信号来产生第一延迟时钟信号。第一输出时钟产生器耦接第一可程式延迟串,根据第一延迟时钟信号以产生第二时钟信号。第一相位检测器根据检测第一时钟信号以及第一时钟信号的相位差来产生第一相位领先或落后信息。其中第一调整信号根据第一相位领先或落后信息来产生。

3、根据本发明的实施例,收发方法包括:根据第一调整信号以提供第一调整延迟量,根据第一调整延迟量以延迟第一时钟信号来产生第一延迟时钟信号;根据第一延迟时钟信号以产生第二时钟信号;根据检测第一时钟信号以及第一时钟信号的相位差来产生第一相位领先或落后信息;以及,根据第一相位领先或落后信息来产生中第一调整信号。

4、基于上述,本发明的接口装置通过可程式延迟串来针对时钟信号进行延迟,并经由调整信号来调整可程式延迟串提供的调整延迟量,可产生正确的时钟信号来取样主电路所传送的数据信号。如此一来,接口装置不需设置大量的延迟器来延迟数据信号的多个位,可有效降低电路布局所需要的面积,并减少延迟器中因数据信号转态所产生的功率消耗。

技术特征:

1.一种接口装置,适用于一半导体装置,所述半导体装置包括主装置以及多个从装置,其中所述主装置以及所述多个从装置通过电性连接以堆栈成三维结构,所述接口装置包括:

2.根据权利要求1所述的接口装置,其中所述第一输出时钟产生器包括:

3.根据权利要求2所述的接口装置,其中所述第一输出时钟产生器还包括:

4.根据权利要求2所述的接口装置,其中所述第一输出时钟产生器还包括:

5.根据权利要求2所述的接口装置,其中所述第一调整延迟量、所述匹配延迟量与所述第二时钟树电路的延迟量的总和实质上等于所述第一时钟信号的周期。

6.根据权利要求1所述的接口装置,还包括:

7.根据权利要求1所述的接口装置,其中所述主电路包括:

8.根据权利要求7所述的接口装置,其中所述第二输出时钟产生器包括:

9.根据权利要求8所述的接口装置,其中所述第二输出时钟产生器还包括:

10.根据权利要求8所述的接口装置,其中所述第二输出时钟产生器包括:

11.根据权利要求8所述的接口装置,其中所述第一时钟树电路的延迟量与由所述第二可程式延迟串提供的所述第二调整延迟量的总和实质上等于所述第三时钟信号的周期。

12.根据权利要求7所述的接口装置,还包括:

13.一种信号的收发方法,适用于一半导体装置,所述半导体装置包括主装置以及多个从装置,其中所述主装置以及所述多个从装置通过电性连接相互堆栈,所述信号的收发方法包括:

14.根据权利要求13所述的信号收发方法,还包括:

15.根据权利要求14所述的信号收发方法,还包括:

16.根据权利要求14所述的信号收发方法,还包括:

17.根据权利要求14所述的信号收发方法,其中所述第一调整延迟量、所述匹配延迟量与所述第二时钟树电路的延迟量的总和实质上等于所述第一时钟信号的周期。

18.根据权利要求16所述的信号收发方法,还包括:

19.根据权利要求18所述的信号收发方法,还包括:

20.根据权利要求18所述的信号收发方法,还包括:

技术总结

本发明提供一种接口装置及其信号收发方法。接口装置包括主电路以及从电路。主电路通过多个硅穿孔耦接至从电路。从电路包括第一可程式延迟串、第一输出时钟产生器以及第一相位检测器。第一可程式延迟串根据第一调整信号以提供第一调整延迟量,根据第一调整延迟量以延迟第一时钟信号来产生第一延迟时钟信号。第一输出时钟产生器根据第一延迟时钟信号以产生第二时钟信号。第一相位检测器根据检测第一时钟信号以及第一时钟信号的相位差来产生第一相位领先或落后信息。其中第一调整信号根据第一相位领先或落后信息来产生。

技术研发人员:李必扬,毅格·艾尔卡诺维奇,张鸿仪,高士政

受保护的技术使用者:创意电子股份有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!