延迟锁相环及其锁相方法、存储装置与流程

本发明涉及延迟锁相环,特别涉及一种延迟锁相环及其锁相方法、存储装置。

背景技术:

1、延迟锁相环(delay-locked loop,简称dll)技术被广泛应用于时序领域中,具体地,当从外部装置施加的外部时钟信号被用于相应的半导体装置内部时,可产生由内部电路引起的延迟或时钟偏差,dll可通过补偿这种延迟,使得内部时钟信号和外部时钟信号的相位一致(或者说,边沿对齐、相位锁定),实现内部时钟信号和外部时钟信号的同步。

2、例如,在ddr(double data rate,双倍速率)sdram(synchronous dynamicrandom-access memory,同步动态随机存取内存)等存储装置领域,dll可以实现外部输入的外部时钟信号与存储装置内部的内部时钟信号dqs(或dq)之间的相位锁定(即相位差在预设范围内),以保证数据无误地传输至存储装置中,或从存储装置中读取数据。但是,在dll的相位锁定过程中,其电源电压可能会由于噪声而产生抖动,由此导致存储装置的内部时钟信号dqs通路上的时延改变,进而导致dll的相位锁定时间变长。

技术实现思路

1、本发明的目的在于提供一种延迟锁相环及其锁相方法、存储装置,能够对dll锁定过程进行改进,减弱电源噪声对dll锁定时间的影响,避免电源噪声导致dll的锁定时间加长的问题。

2、为实现上述目的,本发明提供一种延迟锁相环的锁相方法,在所述延迟锁相环的锁定过程中,先进行延迟粗调,后进行延迟细调,直至所述延迟锁相环输出的内部时钟信号和所述延迟锁相环接收的外部时钟信号的相位一致,其中,所述延迟锁相环进行延迟粗调的步骤包括:

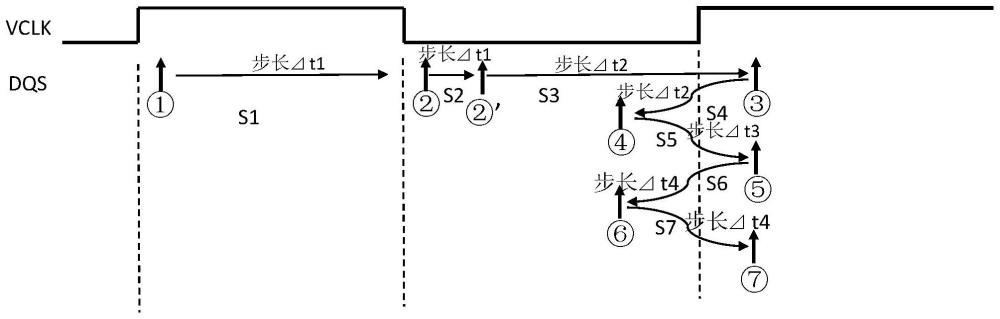

3、s1,以第一粗调步长粗调延迟,使得所述内部时钟信号整体向右调整若干拍,直至所述内部时钟信号的上升沿到达所述外部时钟信号的下降沿右侧;

4、s2,以所述第一粗调步长继续粗调延迟,以强制所述内部时钟信号整体向右调整至少一拍;

5、s3,以小于所述第一粗调步长的第二粗调步长粗调延迟,使得所述内部时钟信号整体向右调整若干拍,直至所述内部时钟信号的所述上升沿到达所述外部时钟信号的所述下降沿后的下一个上升沿右侧。

6、可选地,所述第二粗调步长为所述延迟锁相环的最小粗调步长,所述第一粗调步长为所述第二粗调步长的p倍,其中p为正整数,在s2步骤中,以所述第一粗调步长强制所述内部时钟信号整体向右调整一拍。

7、可选地,在步骤s3之后,所述延迟锁相环进行延迟粗调的步骤还包括:s4,以所述第二粗调步长继续粗调延迟,使得所述内部时钟信号整体向左调整若干拍,直至所述内部时钟信号的所述上升沿到达所述外部时钟信号的所述下降压后的所述下一个上升沿左侧。

8、可选地,所述延迟锁相环进行延迟细调的步骤包括:

9、s5,以小于所述第二粗调步长的第一细调步长细调延迟,使得所述内部时钟信号整体向右调整若干拍,直至所述内部时钟信号的所述上升沿再次到达所述外部时钟信号的所述下降压后的所述下一个上升沿右侧;

10、s6,以小于所述第一细调步长的第二细调步长细调延迟,使得所述内部时钟信号整体向左调整若干拍,直至所述内部时钟信号的所述上升沿再次到达所述外部时钟信号的所述下降压后的所述下一个上升沿左侧;

11、s7,以所述第二细调步长细调延迟,使得所述内部时钟信号整体向右调整若干拍,直至所述内部时钟信号的所述上升沿再次到达所述外部时钟信号的所述下降压后的所述下一个上升沿右侧。

12、可选地,所述第二细调步长为所述延迟锁相环的最小细调步长,所述第二粗调步长为所述第二细调步长的n倍,所述第一细调步长为所述第二细调步长的m倍,其中m和n均为2的次幂,且m小于n。

13、可选地,所述的锁相方法更包括:s8,当所述内部时钟信号的所述上升沿穿越至所述外部时钟信号的所述下降压后的所述下一个上升沿左侧或右侧的次数达到一定阈值,则判定所述内部时钟信号和所述外部时钟信号的相位一致。

14、基于同一发明构思,本发明还提供一种延迟锁相环,包括:

15、延迟链,被配置为接收和延迟外部时钟信号,以输出相应的内部时钟信号;

16、控制电路,耦接所述延迟链,并被配置为在所述延迟锁相环的锁定过程中,控制所述延迟链先进行延迟粗调,后进行延迟细调,以使得所述内部时钟信号和所述外部时钟信号的相位一致,完成延迟锁相环的锁定;

17、其中,在进行延迟粗调的过程中,所述控制电路还被进一步配置为执行以下步骤:

18、s1,控制所述延迟链以第一粗调步长粗调延迟,使得所述内部时钟信号整体向右调整若干拍,直至所述内部时钟信号的上升沿到达所述外部时钟信号的下降沿右侧;

19、s2,控制所述延迟链以所述第一粗调步长继续粗调延迟,以强制所述内部时钟信号整体向右调整至少一拍;

20、s3,控制所述延迟链以小于所述第一粗调步长的第二粗调步长粗调延迟,使得所述内部时钟信号整体向右调整若干拍,直至所述内部时钟信号的所述上升沿到达所述外部时钟信号的所述下降沿后的下一个上升沿右侧。

21、可选地,所述第二粗调步长为所述延迟链的最小粗调步长,所述第一粗调步长为所述第二粗调步长的p倍,其中p为正整数;在进行延迟粗调的过程中,所述控制电路还进一步被配置为:在s2步骤中,控制所述延迟链以所述第一粗调步长继续粗调延迟,以强制所述内部时钟信号整体向右调整一拍。

22、可选地,所述控制电路还进一步被配置为:在步骤s3之后执行步骤s4,控制所述延迟链以所述第二粗调步长继续粗调延迟,使得所述内部时钟信号整体向左调整若干拍,直至所述内部时钟信号的所述上升沿到达所述外部时钟信号的所述下降压后的所述下一个上升沿左侧。

23、可选地,所述控制电路还被进一步配置为执行以下步骤:

24、s5,控制所述延迟链以小于所述第二粗调步长的第一细调步长细调延迟,使得所述内部时钟信号整体向右调整若干拍,直至所述内部时钟信号的所述上升沿再次到达所述外部时钟信号的所述下降压后的所述下一个上升沿右侧;

25、s6,控制所述延迟链以小于所述第一细调步长的第二细调步长细调延迟,使得所述内部时钟信号整体向左调整若干拍,直至所述内部时钟信号的上所述升沿再次到达所述外部时钟信号的所述下降压后的所述下一个上升沿左侧;

26、s7,控制所述延迟链以所述第二细调步长细调延迟,使得所述内部时钟信号整体向右调整若干拍,直至所述内部时钟信号的所述上升沿再次到达所述外部时钟信号的所述下降压后的所述下一个上升沿右侧。

27、可选地,所述第二细调步长为所述延迟锁相环的最小细调步长,所述第二粗调步长为所述第二细调步长的n倍,所述第一细调步长为所述第二细调步长的m倍,其中m和n均为2的次幂,且m小于n。

28、可选地,所述控制电路包括耦接所述延迟链的状态机,所述状态机内部设有状态指示信号,所述状态指示信号根据在所述内部时钟信号的上升沿对所述外部时钟信号采样的高低进行翻转,所述状态机根据所述状态指示信号的翻转进入不同状态,且所述状态机处于不同状态下,控制所述延迟链以不同的调节步长或者调整方向调整延迟,其中所述状态机根据所述状态指示信号的翻转判定从所述步骤s1的状态进入所述步骤s3的状态,在控制所述延迟链进行所述步骤s3的调节之前,所述状态机强制所述延迟链保持所述步骤s1的所述调节步长和调整方向再调整至少一拍。

29、可选地,所述的延迟锁相环还包括:

30、时钟缓冲电路,耦接所述延迟链,并被配置为:将所述延迟链输出的时钟信号输出为所述内部时钟信号;

31、复制时钟缓冲电路,耦接所述延迟链,并被配置为:根据所述延迟链输出的时钟信号产生反馈时钟信号;

32、鉴相器,耦接所述复制时钟缓冲电路和所述控制电路,并被配置为:比较所述外部时钟信号和所述反馈时钟信号之间的相位差,使得所述控制电路根据所述相位差控制所述延迟链的延迟调整。

33、可选地,所述的延迟锁相环还包括配置电路,耦接所述控制电路,其配置所述控制电路在控制所述延迟链进行延迟粗调的过程中执行或者跳过s2步骤。

34、可选地,所述配置电路为电子熔丝或一次性可编程存储器。

35、基于同一发明构思,本发明还提供一种存储装置,包括本发明所述的延迟锁相环,所述延迟锁相环从所述存储装置外部接收外部时钟信号并输出相对所述外部时钟信号延迟的内部时钟信号,所述内部时钟信号为所述存储装置的数据选取脉冲信号,所述延迟锁相环在调整所述内部时钟信号至与所述外部时钟信号相位一致后锁定。

36、与现有技术相比,本发明的技术方案至少具有以下有益效果之一:

37、1、当内部时钟信号dqs的上升沿以第一粗调步长(例如为2c)调整到外部时钟信号vclk下降沿右侧后,强制dqs的上升沿以该第一粗调步长向右调整至少一拍。由于第一粗调步长相对后续的第二粗调步长较大,因此在强制dqs的上升沿以该第一粗调步长向右调整至少一拍后,dqs的上升沿距离vclk的下降沿较远,由此,当电源噪声导致延迟锁相环的延迟减小时,dqs的上升沿回到vclk下降沿左侧的概率大大减小,进而使得dll的锁定时间受电源噪声的影响较小。

38、2、本方案不需要复杂的检测电路检测内部时钟信号dqs的上升沿是否实际发生抖动(由于电源噪声造成),电路简单,易于实施。

- 还没有人留言评论。精彩留言会获得点赞!