阵列和外围区域掩模的制作方法

本公开大体上涉及半导体存储器和方法,且更具体地说,涉及用于阵列和外围区域掩模的设备和方法。

背景技术:

1、通常将存储器装置提供为计算机或其它电子系统中的内部半导体集成电路。存在许多不同类型的存储器,包含易失性存储器和非易失性存储器。易失性存储器可能需要电力来维持其数据(例如,主机数据、误差数据等),并且包含随机存取存储器(ram)、动态随机存取存储器(dram)、静态随机存取存储器(sram)、同步动态随机存取存储器(sdram)以及闸流体随机存取存储器(tram)等。非易失性存储器可以通过在未被供电时保留所存储数据来提供永久数据,并且可以包含nand快闪存储器、nor快闪存储器和电阻可变存储器,例如相变随机存取存储器(pcram)、电阻式随机存取存储器(rram)和磁阻式随机存取存储器(mram),例如自旋力矩转移随机存取存储器(stt ram)等。

2、电子系统通常包含数个处理资源(例如,一或多个处理器),其可检索并执行指令。处理器可包括可执行指令以对数据(例如,一或多个操作数)执行逻辑运算(例如,and、or、not、nand、nor和xor逻辑运算)的数个功能单元(例如,在本文中被称为功能单元电路系统),例如算术逻辑单元(alu)电路系统、浮点单元(fpu)电路系统和/或组合逻辑块。

技术实现思路

1、在一个方面中,本公开提供一种用于形成阵列和外围区域掩模的方法,其包括:在阵列有源区域和外围组件有源区域中同时形成阵列有源区域掩模;在所述外围组件有源区域中形成外围组件有源区域掩模;使用所述阵列有源区域掩模在所述阵列有源区域和所述外围组件有源区域中同时形成蚀刻终止间隔物;以及使用所述外围组件有源区域掩模连同所形成的蚀刻终止间隔物来蚀刻所述外围组件有源区域的一部分以开放外围组件导电接触通孔,以便减少对装置阱的开口的过蚀刻,同时增大对外围组件导电接触件开放的表面积。

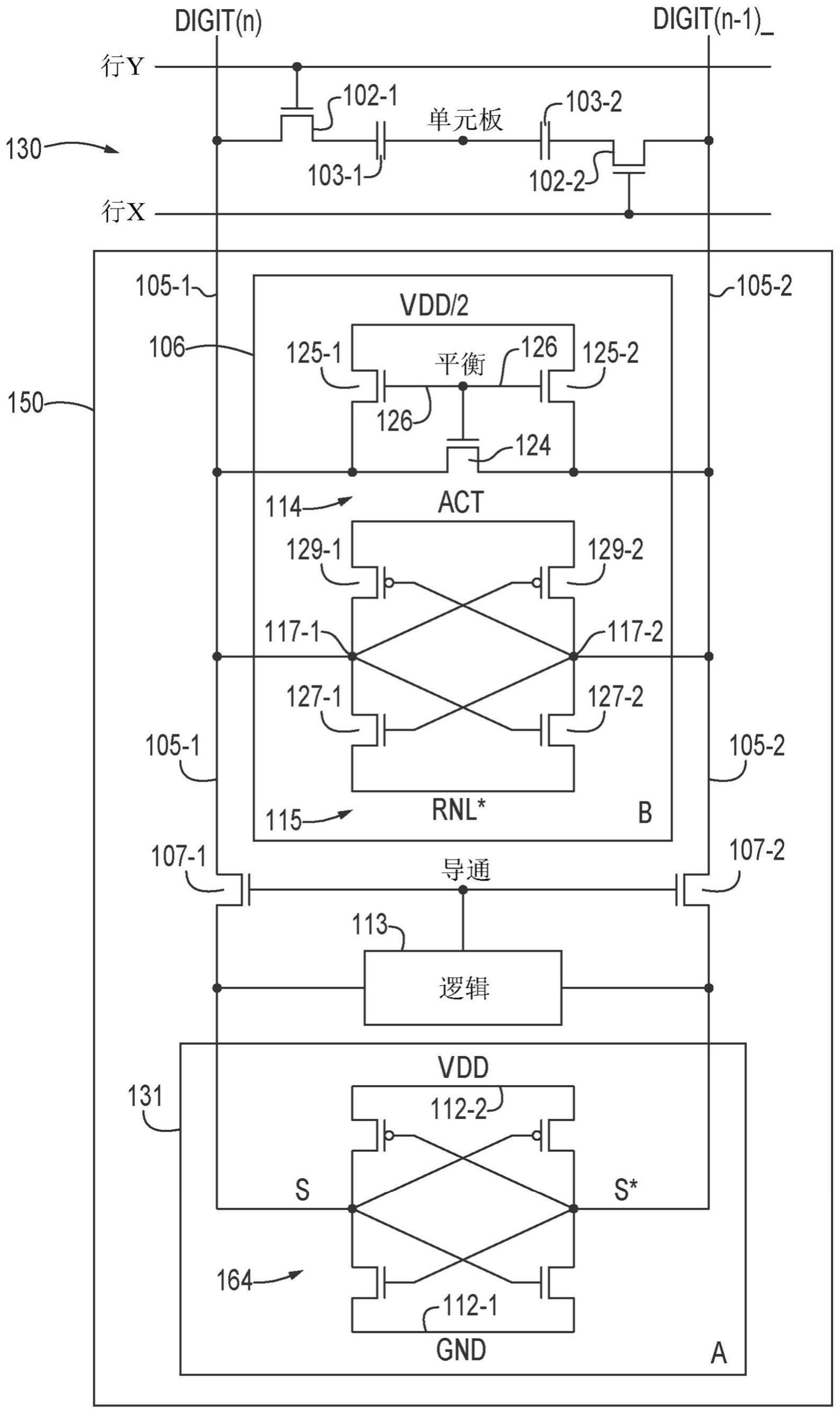

2、在另一方面中,本公开提供一种用于形成阵列和外围区域掩模的方法,其包括:在阵列有源区域和外围组件有源区域中同时形成阵列有源区域掩模;在所述阵列有源区域和所述外围组件有源区域中同时形成外围组件有源区域掩模;使用所述阵列有源区域掩模在所述阵列有源区域和所述外围组件有源区域中同时形成氧化物蚀刻终止间隔物;以及使用所述外围组件有源区域掩模连同氧化物蚀刻终止间隔物蚀刻所述外围组件有源区域的一部分以开放外围组件导电接触通孔,以便增大感测放大器的着陆容限;将导电材料沉积于开放的外围组件导电接触通孔中以形成与所述外围组件导电接触件的局部电互连。

3、在另一方面中,本公开提供一种用于形成阵列和外围区域掩模的方法,其包括:在阵列有源区域和外围组件有源区域中同时形成阵列有源区域掩模;使用所述阵列有源区域掩模在所述阵列有源区域和所述外围组件有源区域中同时形成第一蚀刻终止间隔物柱和第二蚀刻终止间隔物柱;在所述外围组件有源区域中形成外围组件有源区域掩模;在所述阵列有源区域中形成所述外围组件有源区域掩模;将蚀刻终止间隔物同时形成到所述阵列有源区域和所述外围组件有源区域中的所述第一蚀刻终止间隔物和所述第二蚀刻终止间隔物柱内的空间中;以及使用所述外围组件有源区域掩模连同蚀刻终止间隔物蚀刻所述外围组件有源区域的一部分以开放外围组件导电接触通孔,以便形成将一个晶体管的源极/漏极区与所述外围组件有源区域中的另一晶体管的栅极交叉耦合的局部电互连。

技术特征:

1.一种用于形成阵列和外围区域掩模的方法,其包括:

2.根据权利要求1所述的方法,其中所述方法进一步包括使用开放的外围导电接触通孔以形成与所述外围有源区域中的p型金属氧化物半导体pmos晶体管的源极/漏极区的局部电互连。

3.根据权利要求1所述的方法,其中所述方法进一步包括将导电材料沉积于开放的外围导电接触通孔中,以形成将一个晶体管的源极/漏极区与所述外围组件有源区域中的另一晶体管的栅极交叉耦合的局部电互连。

4.根据权利要求1至3中任一权利要求所述的方法,其中所述方法进一步包括将导电材料沉积于所述开放的外围导电接触通孔中,以用电气方式将一个互补金属氧化物半导体cmos晶体管对中的源极/漏极区与另一cmos晶体管对的栅极电耦合,从而在外围区域中形成感测放大器。

5.根据权利要求1至3中任一权利要求所述的方法,其中所述方法进一步包括蚀刻所述外围组件有源区域的所述部分,以开放直径为十(10)纳米或更小纳米的外围组件导电接触通孔。

6.一种用于形成阵列和外围区域掩模的方法,其包括:

7.根据权利要求6所述的方法,其中形成所述阵列有源区域掩模且根据光刻掩模形成所述外围组件有源区域掩模。

8.根据权利要求6所述的方法,其中蚀刻所述外围组件有源区域的所述部分包括蚀刻到硅衬底中。

9.根据权利要求6所述的方法,其中蚀刻所述外围组件有源区域的所述部分包括使用干式蚀刻或化学机械抛光cmp中的一者。

10.一种用于形成阵列和外围区域掩模的方法,其包括:

11.根据权利要求10所述的方法,其中形成所述第一蚀刻终止间隔物柱和所述第二蚀刻终止间隔物柱包括形成干式带。

12.根据权利要求10所述的方法,其进一步包括在于所述外围组件有源区域中形成外围组件有源区域掩模之前蚀刻所述第二蚀刻终止间隔物柱。

13.根据权利要求10至12中任一权利要求所述的方法,其进一步包括将硬掩模材料(322)和氧化物(324)的重复叠加沉积于衬底(328)上以在所述阵列有源区域和所述外围组件有源区域中形成半导体结构。

14.根据权利要求13所述的方法,其中蚀刻所述外围组件有源区域的一部分包括蚀刻所述半导体结构内的材料。

15.根据权利要求13所述的方法,其中蚀刻所述外围组件有源区域的所述部分包括使用对所述半导体结构内的所述材料选择性的蚀刻材料来蚀刻所述沉积。

16.根据权利要求10至12中任一权利要求所述的方法,其进一步包括从一晶体管一电容器1t1c存储器单元的dram阵列形成存储器裸片。

17.根据权利要求10至12中任一权利要求所述的方法,其进一步包括通过放置形成于所述第一蚀刻终止间隔物柱与所述第二蚀刻终止间隔物柱之间的所述阵列有源区域掩模来形成多个开口。

技术总结

本公开包含与阵列和外围区域掩模相关的设备和方法。示例方法包括在阵列有源区域和外围组件有源区域中同时形成阵列有源区域掩模。所述方法进一步包括在所述外围组件有源区域中形成外围组件有源区域掩模。所述方法进一步包括使用所述阵列有源区域掩模在所述阵列有源区域和所述外围组件有源区域中同时形成蚀刻终止间隔物。所述方法进一步包括使用所述外围组件有源区域掩模连同所形成的蚀刻终止间隔物来蚀刻所述外围组件有源区域的一部分以开放外围组件导电接触通孔,以便减少对装置阱的开口的过蚀刻,同时增大对外围组件导电接触件开放的表面积。

技术研发人员:李奎锡

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!