RC延时电路调整方法、电子设备和存储介质与流程

本申请涉及芯片应用,特别涉及一种rc延时电路调整方法、电子设备和存储介质。

背景技术:

1、在芯片应用的很多场景中,需要一个比较准确的绝对时间。譬如,当一个动作发生后的t时间时,触发另外一个动作发生;譬如需要在芯片内部集成一个精确的时钟,作为芯片某些功能的运算基础。

2、在芯片内部解决时间t精度的问题,变得尤为重要,而电阻的精度是时间t精度的最大影响因素。因此,如何控制电阻精度以解决芯片内部时间t精度的问题成为亟待解决的难题。

技术实现思路

1、有鉴于此,本发明旨在至少在一定程度上解决相关技术中的问题之一。为此,本申请的目的在于提供一种rc延时电路调整方法、电子设备和存储介质。

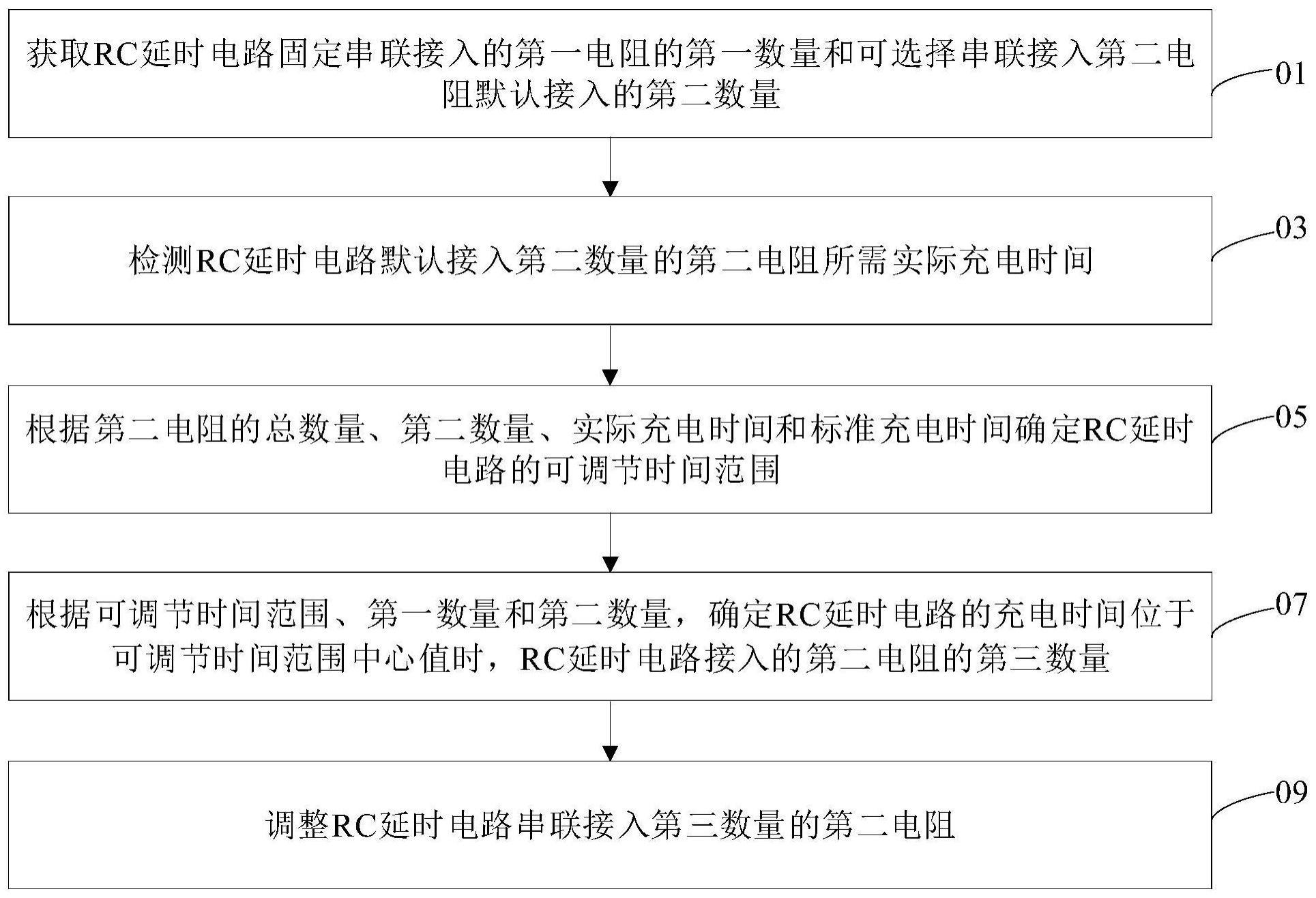

2、本申请实施方式提供一种rc延时电路调整方法。所述rc延时电路调整方法包括:获取rc延时电路固定串联接入的第一电阻的第一数量和可选择串联接入第二电阻默认接入的第二数量;检测所述rc延时电路默认接入所述第二数量的所述第二电阻所需实际充电时间;根据所述第二电阻的总数量、所述第二数量、所述实际充电时间和标准充电时间确定所述rc延时电路的充电时间的可调节时间范围;根据所述可调节时间范围、所述第一数量和所述第二数量,确定所述rc延时电路的充电时间位于所述可调节时间范围中心值时,所述rc延时电路接入的所述第二电阻的第三数量;调整所述rc延时电路串联接入所述第三数量的所述第二电阻。

3、在某些实施方式中,所述根据所述第二电阻的总数量、所述第二数量、所述实际充电时间和标准充电时间确定所述rc延时电路的充电时间的可调节时间范围的步骤之前,所述rc延时电路调整方法包括:根据所述rc延时电路控制输出的标准时钟信号周期确定所述标准充电时间。

4、在某些实施方式中,所述rc延时电路调整方法还包括:根据所述rc延时电路控制输出的目标时钟信号周期确定目标充电时间;根据所述目标充电时间确定待调节的所述第二电阻的第四数量;调节所述rc延时电路串联接入所述第四数量的所述第二电阻,以使所述rc延时电路控制输出所述目标时钟信号。

5、在某些实施方式中,所述根据所述实际充电时间和标准充电时间确定所述rc延时电路的可调节时间范围的步骤通过下列条件式实现:

6、

7、其中,t0为标准充电时间,tdut为实际充电时间,n为所述rc延时电路接入的所述第一数量的所述第一电阻和所述第二数量的所述第二电阻的数量和,δn为选择接入的所述第二电阻的数量与所述第二数量的差值。

8、在某些实施方式中,所述根据所述可调节时间范围、所述第一数量和所述第二数量,确定所述rc延时电路的充电时间位于所述可调节时间范围中心值时,所述rc延时电路接入的所述第二电阻的第三数量,包括:确定所述rc延时电路的充电时间位于所述可调节时间范围中心值的本征时间;获取期望调节时间范围相对于所述本征时间的比率;根据所述第一数量、所述第二数量和所述期望调节时间范围相对于所述本征时间的比率确定所述第三数量。

9、在某些实施方式中,所述根据所述第一数量、所述第二数量和所述期望调节时间范围相对于所述本征时间的比率确定所述第三数量的步骤通过下列条件式实现:

10、

11、其中,nx为所述rc延时电路接入的所述第一数量的第一电阻和所述第三数量的第二电阻的数量和,n为所述rc延时电路接入的所述第一数量的所述第一电阻和所述第二数量的所述第二电阻的数量和,x为所述期望调节时间范围相对于所述本征时间的比率。

12、在某些实施方式中,所述rc延时电路调整方法包括:根据所述第一数量、所述第二数量和所述期望调节时间范围相对于所述本征时间的比率确定电阻调整范围。

13、在某些实施方式中,所述根据所述第一数量、所述第二数量和所述期望调节时间范围相对于所述本征时间的比率确定电阻调整范围的步骤中,确定所述电阻调整范围的上限通过下列条件式实现:

14、

15、确定所述电阻调整范围的上限通过下列条件式实现:

16、

17、其中,δn+为所述rc延时电路的充电时间为所述期望调节时间上限时,选择接入的所述第二电阻的数量与所述第二数量的差值,δn-为所述rc延时电路的充电时间为所述期望调节时间下限时,选择接入的所述第二电阻的数量与所述第二数量的差值,n为所述rc延时电路接入的所述第一数量的所述第一电阻和所述第二数量的所述第二电阻的数量和,x为所述期望调节时间范围相对于所述本征时间的比率。

18、本申请还提供一种电子设备。所述电子设备包括处理器和存储器,所述存储器存储有计算机程序,所述计算机程序被所述处理器执行时,实现上述实施方式中任一项所述的rc延时电路调整方法。

19、本申请还提供一种计算机可读存储介质。所述计算机可读存储介质存储有计算机程序,当所述计算机程序被一个或多个处理器执行时,实现上述实施方式中任一项所述的rc延时电路调整方法。

20、本申请的rc延时电路调整方法、电子设备和存储介质根据可调节时间范围、第一数量和第二数量,确定rc延时电路的充电时间位于可调节时间范围中心值时,rc延时电路接入的第二电阻的第三数量,调整rc延时电路串联接入第三数量的第二电阻,从而避免实测时间调整的覆盖范围中心值偏移的问题,实现对电阻精度的控制,以解决芯片内部时间精度的问题。

21、本申请的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本申请的实践了解到。

技术特征:

1.一种rc延时电路调整方法,其特征在于,包括:

2.根据权利要求1所述的rc延时电路调整方法,其特征在于,所述根据所述第二电阻的总数量、所述第二数量、所述实际充电时间和标准充电时间确定所述rc延时电路的充电时间的可调节时间范围的步骤之前,所述rc延时电路调整方法包括:

3.根据权利要求2所述的rc延时电路调整方法,其特征在于,所述rc延时电路调整方法还包括:

4.根据权利要求1所述的rc延时电路调整方法,其特征在于,所述根据所述实际充电时间和标准充电时间确定所述rc延时电路的可调节时间范围的步骤通过下列条件式实现:

5.根据权利要求1所述的rc延时电路调整方法,其特征在于,所述根据所述可调节时间范围、所述第一数量和所述第二数量,确定所述rc延时电路的充电时间位于所述可调节时间范围中心值时,所述rc延时电路接入的所述第二电阻的第三数量,包括:

6.根据权利要求5所述的rc延时电路调整方法,其特征在于,所述根据所述第一数量、所述第二数量和所述期望调节时间范围相对于所述本征时间的比率确定所述第三数量的步骤通过下列条件式实现:

7.根据权利要求5所述的rc延时电路调整方法,其特征在于,所述rc延时电路调整方法包括:

8.根据权利要求7所述的rc延时电路调整方法,其特征在于,所述根据所述第一数量、所述第二数量和所述期望调节时间范围相对于所述本征时间的比率确定电阻调整范围的步骤中,确定所述电阻调整范围的上限通过下列条件式实现:

9.一种电子设备,其特征在于,包括处理器和存储器,所述存储器存储有计算机程序,所述计算机程序被所述处理器执行时,实现权利要求1-8任一项所述的rc延时电路调整方法。

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机程序,当所述计算机程序被一个或多个处理器执行时,实现权利要求1-8任一项所述的rc延时电路调整方法。

技术总结

本申请公开了一种RC延时电路调整方法。该调整方法包括:获取固定串联接入的第一电阻的第一数量和可选择串联接入第二电阻默认接入的第二数量;检测默认接入第二数量的第二电阻所需实际充电时间;根据第二电阻的总数量、第二数量、实际充电时间和标准充电时间确定RC延时电路的可调节时间范围;根据可调节时间范围、第一数量和第二数量,确定RC延时电路的充电时间位于可调节时间范围中心值时,接入的第二电阻的第三数量;调整串联接入第三数量的第二电阻。本申请通过确定RC延时电路的充电时间位于可调节时间范围中心值时,接入的第二电阻的第三数量,调整RC延时电路,避免实测时间调整的覆盖范围中心值偏移的问题,实现对电阻精度的控制。

技术研发人员:王蒙,白青刚

受保护的技术使用者:深圳市创芯微微电子有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!