存储器装置、存储器电路及存储器电路的制造方法与流程

本发明涉及一种存储器装置、存储器电路及存储器电路的制造方法。

背景技术:

1、电子可抹除可编程只读存储器(以下简称eeprom)为一种可在无电源供应的状态下保存数据的存储器装置,其具有存取速度快、容量大以及体积小等优点,因此eeprom目前已广泛地应用于各种电子产品中。

2、在一般的eeprom中,通过对栅极施加不同的控制栅电压(vg),以控制电子是否隧穿至浮置栅中。当电子进入浮置栅中,eeprom的存储胞将存入「1」。反之,当电子由浮置栅中逃脱,则eeprom的存储胞将存入「0」。

技术实现思路

1、本发明提供一种存储器装置、存储器电路以及存储器电路的制造方法,其中存储器装置具有存取速度快的优点。

2、本发明的至少一实施例提供一种存储器装置。存储器装置包括基板、氧化物绝缘层、第一金属氧化物层、第一栅介电层、第二金属氧化物层、第二栅介电层、第一栅极、源极以及漏极。氧化物绝缘层位于基板之上。第一金属氧化物层位于氧化物绝缘层之上。第一栅介电层位于第一金属氧化物层之上。第二金属氧化物层位于第一栅介电层之上。第二栅介电层位于第二金属氧化物层之上。第一栅极位于第二栅介电层之上。第二金属氧化物层位于第一栅极与第一金属氧化物层之间。源极以及漏极电连接第一金属氧化物层。

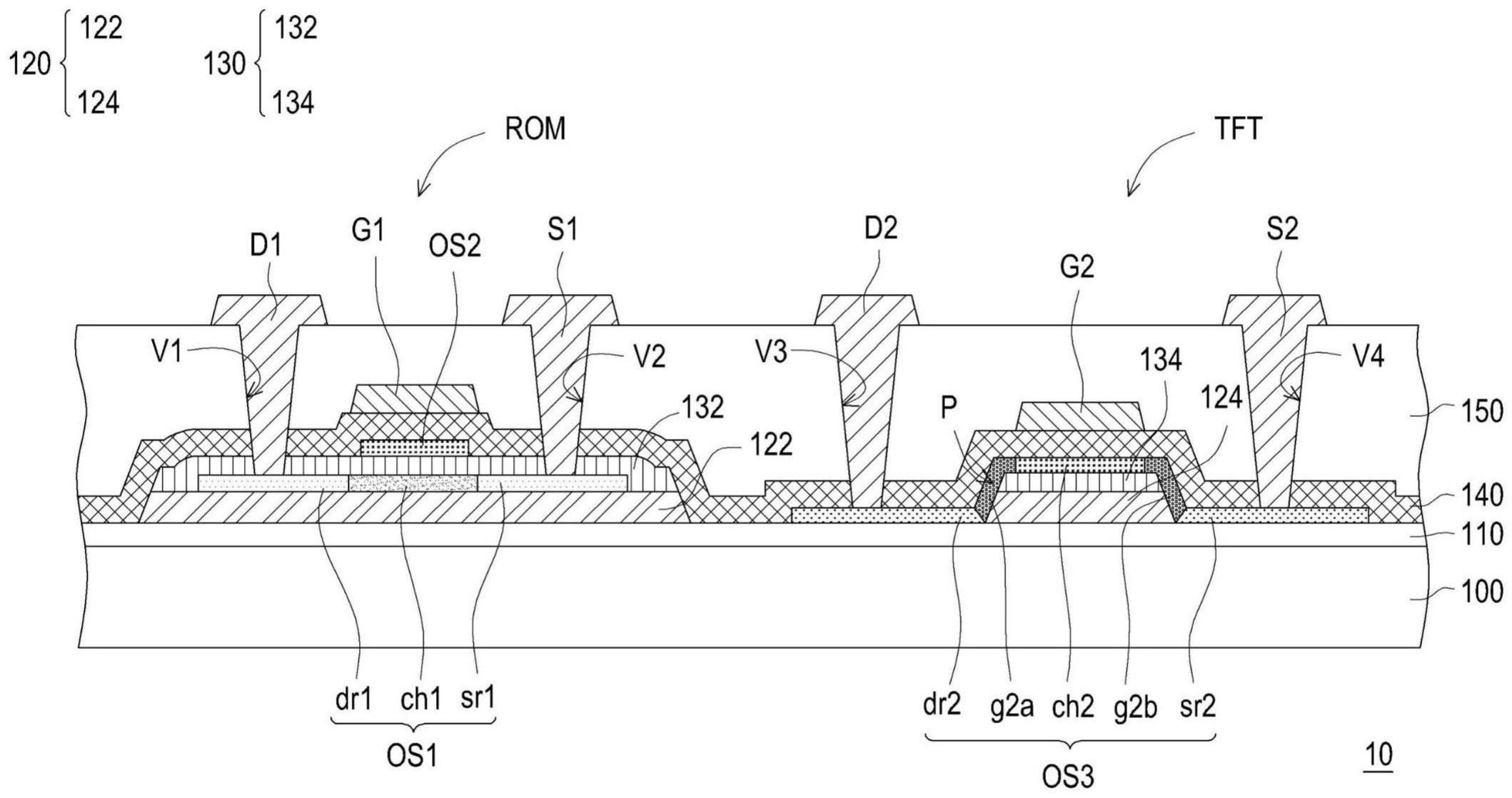

3、本发明的至少一实施例提供一种存储器电路。存储器电路包括基板、氧化物绝缘层、第一栅介电层、第二栅介电层、存储器装置以及薄膜晶体管。氧化物绝缘层位于基板之上,且包括第一含氧结构以及第二含氧结构。第一栅介电层位于氧化物绝缘层之上,且包括第一介电结构以及第二介电结构。第二含氧结构与第二介电结构互相堆叠以构成凸起结构。第二栅介电层位于第一栅介电层之上。存储器装置包括第一金属氧化物层、第二金属氧化物层、第一栅极、第一源极以及第一漏极。第一金属氧化物层位于第一含氧结构之上。第一介电结构位于第一金属氧化物层与第二金属氧化物层之间。第二栅介电层位于第二金属氧化物层与第一栅极之间。第二金属氧化物层位于第一栅极与第一金属氧化物层之间。第一源极以及第一漏极电连接第一金属氧化物层。薄膜晶体管包括第三金属氧化物层、第二栅极、第二源极以及第二漏极。第三金属氧化物层覆盖凸起结构的顶面以及侧面。第二栅极重叠于第三金属氧化物层。第二栅介电层位于第二栅极与第三金属氧化物层之间。第二源极以及第二漏极电连接该第三金属氧化物层。

4、本发明的至少一实施例提供一种存储器电路的制造方法,包括:形成氧化物绝缘层于基板之上;形成第一金属氧化物层于氧化物绝缘层之上;形成第一栅介电层于第一金属氧化物层之上;形成第二金属氧化物层于第一栅介电层之上;形成第二栅介电层于第二金属氧化物层之上;形成第一栅极于第二栅介电层之上,其中第二金属氧化物层位于第一栅极与第一金属氧化物层之间;形成电连接至第一金属氧化物层的源极以及漏极。

技术特征:

1.一种存储器装置,包括:

2.如权利要求1所述的存储器装置,其中该第一金属氧化物层包括源极区、漏极区以及位于该源极区与该漏极区之间的沟道区,其中该源极区与该漏极区的电阻率低于该沟道区的电阻率,且该第二金属氧化物层位于该沟道区与该第一栅极之间。

3.如权利要求2所述的存储器装置,还包括:

4.如权利要求3所述的存储器装置,其中该第一金属氧化物层还包括:

5.如权利要求1所述的存储器装置,其中该第一栅介电层的厚度小于该第二栅介电层的厚度。

6.如权利要求1所述的存储器装置,其中在该基板的顶面的法线方向上,该第一栅极完全遮蔽该第二金属氧化物层。

7.一种存储器电路,包括:

8.如权利要求7所述的存储器电路,其中该第三金属氧化物层包括:

9.如权利要求8所述的存储器电路,还包括:

10.如权利要求7所述的存储器电路,还包括:

11.如权利要求7所述的存储器电路,其中该薄膜晶体管还包括:

12.如权利要求11所述的存储器电路,其中该底栅极的长度大于该第二栅极的长度。

13.如权利要求7所述的存储器电路,其中该第二金属氧化物层与该第三金属氧化物层属于同一图案化层。

14.一种存储器电路的制造方法,包括:

15.如权利要求14所述的存储器电路的制造方法,还包括:

16.如权利要求15所述的存储器电路的制造方法,还包括:

17.如权利要求15所述的存储器电路的制造方法,还包括:

技术总结

本发明公开一种存储器装置、存储器电路及存储器电路的制造方法,其中该存储器装置包括基板、氧化物绝缘层、第一金属氧化物层、第一栅介电层、第二金属氧化物层、第二栅介电层、第一栅极、源极以及漏极。氧化物绝缘层位于基板之上。第一金属氧化物层位于氧化物绝缘层之上。第一栅介电层位于第一金属氧化物层之上。第二金属氧化物层位于第一栅介电层之上。第二栅介电层位于第二金属氧化物层之上。第一栅极位于第二栅介电层之上。第二金属氧化物层位于第一栅极与第一金属氧化物层之间。源极以及漏极电连接第一金属氧化物层。

技术研发人员:黄震铄

受保护的技术使用者:友达光电股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!