一种可扩展低压信令标准的驱动器及其驱动方法与流程

1.本发明属于集成电路设计技术领域,尤其涉及一种可扩展低压信令标准的驱动器及其驱动方法。

背景技术:

2.可扩展低压信号标准(slvs,scalable low-voltage signaling)描述了一种差分电流控制协议。slvs是一种芯片到芯片信令协议,作为快速串行数据传输接口标准,由于它具有低功耗和可扩展性,以及降低噪音、更快的电路速度和降低功耗等优点,近年来用于神经生物学实验、辐射探测器和其他应用的多通道集成电路等场景愈加广泛。

3.然而,传统的slvs驱动器的晶体管(例如nmos晶体管)工作在线性区,需要大尺寸的晶体管,导致寄生电容较大,因此信号转换期间的过冲电压较大,也增大了驱动器面积。此外,在较高的数据速率下,通道损耗使信号高频成分衰减严重,影响信号传输完整性。

4.因此,如何优化slvs驱动器,以进一步提高slvs驱动器的输出信号质量,降低驱动器的面积等,是亟待解决的问题。

技术实现要素:

5.本发明是为解决上述现有技术的全部或部分问题,提供了一种可扩展低压信令标准的驱动器,以进一步提高slvs驱动器的输出信号质量。

6.本发明提供了一种可扩展低压信令标准的驱动器,包括:主体驱动电路,用于输出期望差分信号;共模反馈电路,用于稳定所述期望差分信号的共模电压;预加重电路,用于提高期望差分信号的高频分量幅度;所述预加重电路和所述共模反馈电路分别与所述主体驱动电路连接。本发明通过共模反馈电路调节期望差分信号的共模电压,同时利用预加重电路补偿信号在传输过程中高频衰减,以提高输出期望差分信号的质量。

7.所述驱动器,还包括:单端转差分电路,用于将数据输入信号转换为第一差分信号;电平转换电路,用于转换所述第一差分信号的电压;边缘对齐电路,用于提高所述第一差分信号的对称性;预驱动电路,用于将所述第一差分信号转换为第二差分信号,所述第二差分信号用于驱动主体驱动电路;脉冲生成电路,用于检测所述第一差分信号的上升沿产生脉冲控制信号,所述脉冲控制信号用于驱动所述预加重电路;所述单端转差分电路、所述电平转换电路、所述边缘对齐电路和所述预驱动电路依次连接,所述电平转换电路和所述脉冲生成电路连接。单端转差分电路可以提高信号的抗干扰能力,能有效抑制电磁干扰,且信号的时序定位更加准确。电平转换电路在不同工作电平域的电路模块之间能够实现高电平与低电平之间的转换,这样,电平域不同的模块电路之间便能更好地进行通讯。边缘对齐电路可以提高所述第一差分信号的对称性。预驱动电路可以在保持相位关系不变的情况下,为主体驱动电路提供更适合的驱动电流,更好的驱动主体驱动电路。脉冲生成电路包括上升沿检测电路,用于检测所述第一差分信号的上升沿产生脉冲控制信号,用于驱动预加重电路。

8.所述第二差分信号包括第一输入信号和第二输入信号,所述主体驱动电路包括:第一nmos晶体管、第二nmos晶体管、第三nmos晶体管、第四nmos晶体管、第五nmos晶体管、第一pmos晶体管、第二pmos晶体管、第三pmos晶体管、第四pmos晶体管、第一负载和第二负载;其中,所述第三pmos晶体管、所述第四pmos晶体管和第一电流源组成偏置电路,用于为所述主体驱动电路提供偏置电流;所述第一pmos晶体管的源极与所述第二pmos晶体管的源极连接至偏置电路;所述第一nmos晶体管、所述第三nmos晶体管和所述第一pmos晶体管的栅极分别与所述第一输入信号连接;所述第二nmos晶体管、所述第四nmos晶体管和所述第二pmos晶体管的栅极分别与所述第二输入信号连接;所述第一nmos晶体管的漏极、所述第三nmos晶体管的漏极、所述第一pmos晶体管的漏极连接至第一节点,所述第一节点与所述第一负载的第一端相连接;所述第二nmos晶体管的漏极、所述第四nmos晶体管的漏极、所述第二pmos晶体管的漏极连接至第二节点,所述第二节点和所述第二负载的第一端相连接;所述第一负载的第二端与所述第二负载的第二端连接至第三节点,所述第三节点耦合至共模反馈电路;所述第五nmos晶体管的栅极与共模反馈电路连接,所述第五nmos晶体管的漏极、所述第三nmos晶体管的源极和所述第四nmos晶体管的源极连接至第四节点;所述第五nmos晶体管、所述第一nmos晶体管和所述第二nmos晶体管的源极连接至第五节点,所述第五节点耦合至共模反馈电路。主体驱动电路中尾晶体管采用并联的形式可以大幅度降低晶体管尺寸,同时可以使得共模反馈输出的调节信号的可调节幅度增大,利于调节。

9.所述主体驱动电路还包括:第一电容、第二电容和第三电容;其中,所述第一电容的第一端、所述第二电容的第一端和所述第三电容的第一端连接,所述第一电容的第二端连接第一pmos晶体管的漏极,所述第二电容的第二端连接所述第二pmos晶体管的漏极,所述第三电容的第二端连接所述第三pmos晶体管的漏极。第一电容c1、第二电容c2和第三电容c3组成t形去耦电容,采用t形去耦电容来减少第二差分信号的跳变对期望差分信号耦合产生的共模干扰。

10.所述共模反馈电路包括:第五pmos晶体管、第六pmos晶体管、第七pmos晶体管、第八pmos晶体管、第九pmos晶体管、第十pmos晶体管、第六nmos晶体管、第七nmos晶体管、第八nmos晶体管、第九nmos晶体管、第十nmos晶体管、第十一nmos晶体管、第十二nmos晶体管,第四电容,第五电容;其中,所述第五pmos晶体管、所述第八pmos晶体管、所述第九pmos晶体管、所述第十pmos晶体管的源极与工作电源相连接;所述第十pmos晶体管的栅极与所述第五pmos晶体管的栅极相连接;所述第六pmos晶体管、所述第七pmos晶体管、所述第八pmos晶体管、所述第九pmos晶体管和所述第十pmos晶体管的漏极分别与所述第六nmos晶体管、所述第七nmos晶体管、所述第八nmos晶体管、所述第九nmos晶体管和所述第十nmos晶体管的漏极相连接;所述第五pmos晶体管的漏极、所述第六pmos晶体管的源极和所述第七pmos晶体管的源极连接至第七节点;所述第七nmos晶体管、所述第八pmos晶体管和所述第十pmos晶体管的栅极分别与其漏极相连接,所述第八nmos晶体管的栅极与所述第六nmos晶体管的漏极相连接;所述第五pmos晶体管、所述第八pmos晶体管、所述第六nmos晶体管的栅极分别与所述第十pmos晶体管、所述第九pmos晶体管、所述第七nmos晶体管的栅极相连接;所述第六nmos晶体管、所述第七nmos晶体管、所述第八nmos晶体管、所述第九nmos晶体管、所述第十nmos晶体管和所述第十二nmos晶体管的源极接地;所述第十nmos晶体管的栅极连接使能信号,所述第六pmos晶体管的栅极连接参考电压,所述第七pmos晶体管的栅极连接至第三

节点;所述第七pmos晶体管的漏极与所述第九nmos晶体管的栅极相连接;所述第九nmos晶体管的栅极通过所述第四电容与所述第九nmos晶体管的漏极相连接;所述第七pmos晶体管的漏极通过所述第五电容与所述第十一nmos晶体管的漏极相连接;所述第七pmos晶体管的栅极与所述第十一nmos晶体管的漏极相连接;所述第十一nmos晶体管的源极与所述第十二nmos晶体管的栅极相连接;所述第十二nmos晶体管的漏极与所述第五nmos晶体管的源极相连接;所述第十一nmos晶体管的栅极与工作电源相连接。如此,利用第一电阻、第二电阻产生期望差分信号的共模信号vcm,共模调节路径使用共模反馈至尾部nmos管可以始终维持共模电平的较高精度,且第十一nmos晶体管、第十二nmos晶体管构成的rc网络增强稳定性,防止振荡。

11.所述预加重电路包括:第十一pmos晶体管、第十二pmos晶体管、第十三pmos晶体管、第十四pmos晶体管、第十五pmos晶体管、第十六pmos晶体管、第十三nmos晶体管、第十四nmos晶体管、第十五nmos晶体管和第十六nmos晶体管;其中,所述第十一pmos晶体管、所述第十二pmos晶体管和第二电流源组成偏置电路,用于为预加重电路提供偏置电流;所述第十三pmos晶体管、所述第十四pmos晶体管、所述第十五pmos晶体管、所述第十六pmos晶体管的源极与所述第十一pmos晶体管的漏极相连;所述第十三nmos晶体管、所述第十四nmos晶体管、所述第十五nmos晶体管和所述第十六nmos晶体管的源极接地;所述第十三pmos晶体管、所述第十四pmos晶体管的漏极与所述第十三nmos晶体管、所述第十四nmos晶体管的漏极连接;所述第十五pmos晶体管、所述第十六pmos晶体管的漏极与所述第十五nmos晶体管、所述第十六nmos晶体管的漏极连接。如此,采用预加重电路可以补偿信号在信道中的高频成分衰减,提高了工作频率。

12.本发明还提供了一种可扩展低压信令标准的驱动器的驱动方法,包括:将输入信号经由单端转差分电路转换为第一差分信号;第一差分信号经由电平转换电路转换所述第一差分信号的电压;第一差分信号经由边缘对齐电路和预驱动电路,将所述第一差分信号转换为第二差分信号;通过第二差分信号驱动主体驱动电路输出期望差分信号;其中,所述第一差分信号还经由预加重电路,提高期望差分信号的高频分量幅度;所述期望差分信号还经由共模反馈电路,稳定所述期望差分信号的共模电压。

13.所述第一差分信号还经由预加重电路,提高期望差分信号的高频分量幅度,包括:所述第一差分信号经由脉冲生成电路,检测所述第一差分信号的上升沿产生脉冲控制信号,所述脉冲控制信号用于驱动所述预加重电路。

14.所述主体驱动电路包括开关控制路径与共模调节路径,所述开关控制路径与所述共模调节路径并联。如此,可有效节省器件的面积。

15.与现有技术相比,本发明的主要有益效果:本发明提供了一种可扩展低压信令标准的驱动器,通过共模反馈电路调节期望差分信号的共模电压,利用预加重电路补偿信号在传输过程中高频衰减,以提高输出期望差分信号的质量。

16.在一些实施例中,驱动器采用并联控制尾晶体管使晶体管面积大幅度减少,寄生电容较低,关键节点充放电速度快。

17.在一些实施例中,本发明提供的驱动器在关键节点采用t形去耦电容对节点充电降低因预驱动输出信号的耦合造成的共模噪声,使输出信号眼图质量提高。

附图说明

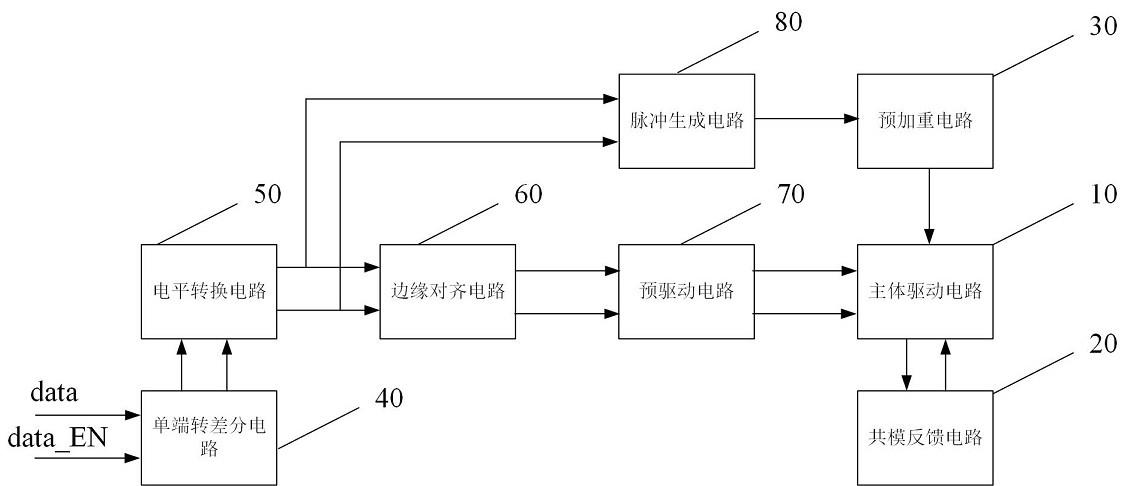

18.图1为本发明实施例提供的slvs驱动器的结构示意图;图2为本发明实施例提供的单端转差分电路、电平转换电路、边缘对齐电路和预驱动电路的电路结构图;图3为本发明实施例提供的脉冲生成电路的电路结构图;图4为本发明实施例提供的主体驱动电路和共模反馈电路的电路结构图;图5为本发明实施例提供的预加重电路的电路结构图;图6为本发明实施例提供的预加重电路的原理示意图;图7为本发明提供的slvs驱动器的驱动方法的流程框图。

具体实施方式

19.下面将对本发明具体实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

20.相关技术中,slvs驱动器一般直接利用低压差线性稳压器(ldo)为驱动器提供较低的电压,从而使得驱动器输出较低共模电平的差分信号,但是这种方法对pvt(process voltage temperature,工艺 电压 温度)变化敏感,不能精确调节共模电压、输出阻抗以及输出信号的摆幅。另一种精度有所提高的slvs驱动器则是利用共模反馈调节共模电压,并利用电流镜像控制输出电流大小(2ma),这种控制方法保持了较高的精度,但是由于输出信号的差分信号其中低电平为100mv,尾电流源晶体管和驱动器的开关管串联在一起就必须使用更大尺寸的晶体管,使得面积增大,寄生电容更高。

21.同时,在传统补偿信号的高频分量的预加重电路中一般会使用较多的电阻,或者为了保证预加重信号在数据跳边沿时工作,还需要复杂的控制电路和时钟网络,从而导致电路规模和面积非常庞大。

22.基于此,参见附图1,本发明提供了一种可扩展低压信令标准的驱动器,驱动器包括:主体驱动电路10,用于输出期望差分信号;共模反馈电路20,用于稳定期望差分信号;预加重电路30,用于提高期望差分信号的高频分量幅度;预加重电路和共模反馈电路分别与主体驱动电路连接。本发明通过共模反馈电路调节期望差分信号的共模电压,利用预加重电路补偿信号在传输过程中高频衰减,以提高输出期望差分信号的质量。

23.参见附图1,驱动器还包括:单端转差分电路40,用于将数据输入信号转换为第一差分信号;电平转换电路50,用于转换第一差分信号的电压;边缘对齐电路60,用于提高第一差分信号的对称性;预驱动电路70,用于将第一差分信号转换为第二差分信号,第二差分信号用于驱动主体驱动电路10;脉冲生成电路80,用于检测第一差分信号的上升沿产生脉冲控制信号,脉冲控制信号用于驱动预加重电路30;单端转差分电路40、电平转换电路50、边缘对齐电路60和预驱动电路70依次连接,电平转换电路50和脉冲生成电路80连接。

24.单端转差分电路40,用于将输入信号转换为第一差分信号。如附图2所示,单端转差分电路40包括:第一与非门401、第二与非门402、第三与非门403、第四与非门404、第一反相器405、第二反相器406和第三反相器407;其中第一与非门401、第二与非门402、第三与非

门403和第四与非门404的第一输入端连接使能信号data_en,第一与非门401的第二输入端连接数据输入信号data,第三与非门403的输入端通过第一反相器405连接数据输入信号data,第一与非门401的输出端、第三与非门403的输出端分别与第二与非门402的第二输入端、第四与非门404的第二输入端相连接;第二与非门402的第二输入端与第四与非门404的输出端连接,第四与非门404的第二输入端与第二与非门402的输出端连接;第二与非门402的输出端连接第二反相器406,第四与非门404的输出端连接第三反相器407。在实际操作中,使能信号的逻辑状态可以为“1”或“0”,使能信号例如可以为高电压使得逻辑状态为“1”,用于驱动单端转差分电路40工作。当使能信号data_en始终为“1”时,第一至第四与非门可以看作反相器的功能,即第一与非门401、第二与非门402和第二反相器406,可以看作奇数个串联的反相器组;第一反相器405、第三与非门403、第四与非门404和第三反相器407,可以看作偶数个串联的反向器组,如此使得单端信号转换为第一差分信号,第一差分信号的两个输出信号的相位差180度,振幅相同。单端转差分电路可以提高信号的抗干扰能力,能有效抑制电磁干扰,且信号的时序定位更加准确。

25.参见附图2,电平转换电路(level shifter)50,用于转换第一差分信号的电压。电平转换电路在不同工作电平域的电路模块之间能够实现高电平与低电平之间的转换,这样,电平域不同的模块电路之间便能更好地进行通讯。具体的,电平转换电路50例如可以提升第一差分信号的电压。例如,数据输入信号data是低电平0.8v的信号,而主驱动器是1.8v电平域的晶体管,则数据输入信号data需要转换为1.8v的信号。在一些实施例中,电平转换电路还有一定的隔离和滤波的作用。

26.参见附图2,在实际操作中,芯核电平域的输入使能信号data_en和数据输入信号data经由单端转差分电路和电平转换电路产生io电平域的第一差分信号,第一差分信号包括第一输出信号p1和第二输出信号p2。

27.继续参见附图2,边缘对齐电路60,用于提高第一差分信号的对称性。边缘对齐电路60,包括:第四反相器601,第五反相器602,第六反相器603,第七反相器604;其中,第一输出信号p1、第二输出信号p2分别连接第四反相器601的输入端、第五反相器602的输入端;第六反相器603和第七反相器604交叉连接。如此,可以提高第一差分信号的对称性。

28.参见附图2,预驱动电路(pre-driver)70,用于将第一差分信号转换为第二差分信号,第二差分信号用于驱动主体驱动电路10。预驱动电路70,包括:第一反相器串联组701,包括偶数个串联的反相器;和第二反相器串联组702,包括偶数个串联的反相器;第一反相器串联组701的反相器数量等于第二反相器串联组702的反相器数量。第一输出信号p1和第二输出信号p2分别经过第一反相器串联组701和第二反相器串联组702,从而转换为第二差分信号,第二差分信号包括第一输入信号inn和第二输入信号inp。如此在保持相位关系不变的情况下,为主体驱动电路提供更适合的驱动电流,更好的驱动主体驱动电路。在一些实施例中,预驱动电路70起到波形整形、平衡信号延时的作用。

29.在实际操作中,第一输出信号p1和第二输出信号p2经由边缘对齐电路60和预驱动电路70产生第一输入信号inn和第二输入信号inp。

30.参见附图3,脉冲生成电路80,用于检测第一差分信号的上升沿产生脉冲控制信号,脉冲控制信号用于驱动预加重电路30。脉冲生成电路包括:开关pmos晶体管mp0、开关nmos晶体管mn0、第一与门801、第八反相器802、第九反相器803、第十反相器804和第十一反

相器805;其中,开关pmos晶体管mp0的源极接高电平,开关nmos晶体管mn0的源极接地,开关pmos晶体管mp0的漏极、开关nmos晶体管mn0的漏极和第一与门的第一输入端连接;开关pmos晶体管mp0的栅极、第一与门的第二输入端连接至第一差分信号,第一与门的输出端连接开关nmos晶体管mn0的栅极;第八反相器802、第九反相器803、第十反相器804和第十一反相器805依次串联;第一与门801的输出端连接第八反相器802的输入端;第八反相器802的输出端产生第一路脉冲控制信号p1_a(p2_a),第九反相器803的输出端产生第二路脉冲控制信号p1_b(p2_b),第十反相器804的输出端产生第三路脉冲控制信号p1_c(p2_c),第十一反相器805的输出端产生第四路脉冲控制信号p1_d(p2_d)。

31.开关pmos晶体管mp0、开关nmos晶体管mn0和第一与门801构成上升沿检测电路,第一差分信号(p1、p2)为低电平时,开关pmos晶体管mp0的漏极为高电平,第一与门801输出为低电平。当第一差分信号(p1、p2)从低电平转为高电平时,首先第一与门801输出为高电平,使得开关nmos晶体管mn0导通,第一与门801的第一输入转为低电平,第一与门801输出再次转换为低电平。第一差分信号(p1、p2)经由上升沿检测电路和串联的四个反相器产生四路脉冲控制信号,脉冲控制信号用于驱动预加重电路30。

32.参见附图4,主体驱动电路包括:第一nmos晶体管mn1、第二nmos晶体管mn2、第三nmos晶体管mn3、第四nmos晶体管mn4、第五nmos晶体管mn5、第一pmos晶体管mp1、第二pmos晶体管mp2、第三pmos晶体管mp3、第四pmos晶体管mp4、第一负载r1和第二负载r2;其中,第三pmos晶体管mp3、第四pmos晶体管mp4和第一电流源i1组成偏置电路,用于为主体驱动电路10提供偏置电流;第一pmos晶体管mp1的源极与第二pmos晶体管mp2的源极连接至偏置电路;第一nmos晶体管mn1、第三nmos晶体管mn3和第一pmos晶体管mp1的栅极分别与第一输入信号inp连接;第二nmos晶体管mn2、第四nmos晶体管mn4和第二pmos晶体管mp2的栅极分别与第二输入信号inn连接;第一nmos晶体管mn1的漏极、第三nmos晶体管mn3的漏极、第一pmos晶体管mp1的漏极连接至第一节点101,第一节点101与第一负载r1的第一端相连接;第二nmos晶体管的漏极、第四nmos晶体管的漏极、第二pmos晶体管的漏极连接至第二节点102,第二节点102和第二负载r2的第一端相连接;第一负载r1的第二端与第二负载r2的第二端连接至第三节点103,第三节点103耦合至共模反馈电路20;第五nmos晶体管mn5的栅极与共模反馈电路20连接,第五nmos晶体管mn5的漏极、第三nmos晶体管mn3的源极和第四nmos晶体管mn4的源极连接至第四节点104;第五nmos晶体管mn5、第一nmos晶体管mn1和第二nmos晶体管mn2的源极连接至第五节点105,第五节点105耦合至共模反馈电路20。第一节点101和第二节点102分别用于输出第一期望差分信号outn和第二期望差分信号outp。

33.参见附图4,电流偏置包括:第三pmos晶体管mp3、第四pmos晶体管mp4和第一电流源i1;其中,第三pmos晶体管mp3的栅极、第四pmos晶体管mp4的栅极和第一电流源的第一端连接至第六节点106;第三pmos晶体管mp3和第四pmos晶体管mp4的源极与工作电压vdd连接;第一电流源的第一端与第四pmos晶体管mp4的漏极连接,第一电流源的第二端接地;第三pmos晶体管mp3的漏极连接至第一pmos晶体管mp1和第二pmos晶体管mp2的源极。

34.主体驱动电路中尾晶体管采用并联的形式可以较串联形式大幅度降低晶体管尺寸,同时可以使得共模反馈输出的调节信号的可调节幅度增大,利于调节。这里并联是指,第一nmos晶体管mn1和第三nmos晶体管mn3、第五nmos晶体管mn5支路并联,和,第二nmos晶体管mn2和第四nmos晶体管mn4、第五nmos晶体管mn5支路并联。当第一输入信号inp为高电

平、第二输入信号inn为低电平时,第一pmos晶体管mp1、第二nmos晶体管mn2、第四nmos晶体管mn4关断,第二pmos晶体管mp2、第一nmos晶体管mn1、第三nmos晶体管mn3导通,输出的第二期望差分信号outp为高电平,输出的第一期望差分信号outn为低电平。当第一输入信号inp为低电平、第二输入信号inn为高电平时,第一pmos晶体管mp1、第二nmos晶体管mn2、第四nmos晶体管mn4导通,第二pmos晶体管mp2、第一nmos晶体管mn1、第三nmos晶体管mn3关断,输出的第二期望差分信号outp为低电平,输出的第一期望差分信号outn为高电平。

35.参见附图4,主体驱动电路还包括:第一电容c1、第二电容c2和第三电容c3;其中,第一电容c1的第一端、第二电容c2的第一端和第三电容c3的第一端连接,第一电容c1的第二端连接第一pmos晶体管mp1的漏极,第二电容c2的第二端连接第二pmos晶体管mp2的漏极,第三电容c3的第二端连接第三pmos晶体管mp3的漏极。如此,第一电容c1、第二电容c2和第三电容c3组成t形去耦电容,第一输入信号inp(第二输入信号inn)从高电平转换为低电平时,第一输入信号inp(第二输入信号inn)通过第一pmos晶体管mp1、第一nmos晶体管mn1、第三nmos晶体管mn3的寄生电容耦合到输出第一期望差分信号outn(第二期望差分信号outp),使本应从低电平转换为高电平的第一期望差分信号outn(第二期望差分信号outp)先产生负的过冲,即从第一节点(第二节点)抽取电流。通过电容第一电容c1、第三电容c3(第二电容c2、第三电容c3)对第一节点(第二节点)进行充电以降低负的过冲电压的现象,减少共模噪声。

36.参见附图4,共模反馈电路包括:第五pmos晶体管mp5、第六pmos晶体管mp6、第七pmos晶体管mp7、第八pmos晶体管mp8、第九pmos晶体管mp9、第十pmos晶体管mp10、第六nmos晶体管mn6、第七nmos晶体管mn7、第八nmos晶体管mn8、第九nmos晶体管mn9、第十nmos晶体管mn10、第十一nmos晶体管mn11、第十二nmos晶体管mn12,第四电容c4,第五电容c5;其中,第五pmos晶体管mp5、第八pmos晶体管mp8、第九pmos晶体管mp9和第十pmos晶体管mp10的源极与工作电源vdd相连接;第十pmos晶体管mp10的栅极与第五pmos晶体管mp5的栅极相连接;第六pmos晶体管mp6、第七pmos晶体管mp7、第八pmos晶体管mp8、第九pmos晶体管mp9和第十pmos晶体管mp10的漏极分别与第六nmos晶体管mn6、第七nmos晶体管mn7、第八nmos晶体管mn8、第九nmos晶体管mn9和第十nmos晶体管mn10的漏极相连接;第五pmos晶体管mp5的漏极、第六pmos晶体管mp6的源极和第七pmos晶体管mp7的源极连接至第七节点107;第七nmos晶体管mn7、第八pmos晶体管mp8和第十pmos晶体管mp10的栅极分别与其漏极相连接,第八nmos晶体管mn8的栅极与第六nmos晶体管mn6的漏极相连接;第五pmos晶体管mp5、第八pmos晶体管mp8、第六nmos晶体管mn6的栅极分别与第十pmos晶体管mp10、第九pmos晶体管mp9、第七nmos晶体管mp7的栅极相连接;第六nmos晶体管mn6、第七nmos晶体管mn7、第八nmos晶体管mn8、第九nmos晶体管mn9、第十nmos晶体管mn10和第十二nmos晶体管mn12的源极接地;第十nmos晶体管mn10的栅极连接使能信号data_en,第六pmos晶体管mp6的栅极连接参考电压vref,第七pmos晶体管mp7的栅极连接至第三节点103;第七pmos晶体管mp7的漏极与第九nmos晶体管mn9的栅极相连接;第九nmos晶体管mn9的栅极通过第四电容c4与第九nmos晶体管mn9的漏极相连接;第七pmos晶体管mp7的漏极通过第五电容c5与第十一nmos晶体管mn11的漏极相连接;第七pmos晶体管mp7的栅极与第十一nmos晶体管mn11的漏极相连接;第十一nmos晶体管mn11的源极与第十二nmos晶体管mn12的栅极相连接;第十二nmos晶体管mn12的漏极与第五nmos晶体管mn5的源极相连接;第十一nmos晶体管mn11的栅极与工

作电源vdd相连接。如此,利用第一电阻r1、第二电阻r2产生第一期望差分信号outp、第二期望差分信号outn的共模信号vcm。第五pmos晶体管至第十pmos晶体管(mp5~mp10)和第六nmos晶体管至第十pmos晶体管(mn6~mn10)以及第四电容c4、第五电容c5组成二级运放用作共模反馈电路。利用使能信号data_en使能共模反馈电路,当共模反馈电路被使能正常工作时,若共模信号vcm低于参考电压vref,则输出信号vctrl降低,第五nmos晶体管mn5阻抗提高,使共模信号vcm提高,反之,输出信号vctrl提高,第五nmos晶体管mn5阻抗降低,使共模信号vcm降低。第十一nmos晶体管mn11、第十二nmos晶体管mn12构成的rc网络增强稳定性,防止振荡。

37.参见附图5,预加重电路包括:第十一pmos晶体管mp11、第十二pmos晶体管mp12、第十三pmos晶体管mp13、第十四pmos晶体管mp14、第十五pmos晶体管mp15、第十六pmos晶体管mp16、第十三nmos晶体管mn13、第十四nmos晶体管mn14、第十五nmos晶体管mn15和第十六nmos晶体管mn16;其中,第十一pmos晶体管mp11、第十二pmos晶体管mp12和第二电流源i2组成偏置电路,用于为预加重电路提供偏置电流;第十三pmos晶体管、第十四pmos晶体管、第十五pmos晶体管、第十六pmos晶体管的源极与第十一pmos晶体管的漏极相连;第十三nmos晶体管、第十四nmos晶体管、第十五nmos晶体管和第十六nmos晶体管的源极接地;第十三pmos晶体管、第十四pmos晶体管的漏极与第十三nmos晶体管、第十四nmos晶体管的漏极连接;第十五pmos晶体管、第十六pmos晶体管的漏极与第十五nmos晶体管、第十六nmos晶体管的漏极连接。

38.参见附图5,电流偏置包括:第十一pmos晶体管mp11、第十二pmos晶体管mp12和第二电流源i2;其中,第十一pmos晶体管mp11的栅极、第十二pmos晶体管mp12的栅极和第二电流源i2的第一端连接至第八节点301;第十一pmos晶体管mp11和第十二pmos晶体管mp12的源极与工作电压vdd连接;第二电流源i2的第一端与第十二pmos晶体管mp12的漏极连接,第二电流源i2的第二端接地;第十一pmos晶体管mp11的漏极连接至第十三pmos晶体管至第十六pmos晶体管(mp13~mp16)的源极。

39.第一路脉冲控制信号包括第一第一路脉冲控制信号p1_a和第二第一路脉冲控制信号p2_a,第二路脉冲控制信号包括第一第二路脉冲控制信号p1_b和第二第二路脉冲控制信号p2_b,第三路脉冲控制信号包括第一第三路脉冲控制信号p1_c和第二第三路脉冲控制信号p2_c,第四路脉冲控制信号包括第一第四路脉冲控制信号p1_d和第二第四路脉冲控制信号p2_d。第十三pmos晶体管mp13的栅极和第十四pmos晶体管mp14的栅极分别连接第一第一路脉冲控制信号p1_a和第二第一路脉冲控制信号p2_a;第十三nmos晶体管mn13的栅极和第十四nmos晶体管mn14的栅极分别连接第二第二路脉冲控制信号p2_b和第一第二路脉冲控制信号p1_b;第十五pmos晶体管mp15的栅极和第十六pmos晶体管mp16的栅极分别连接第二第三路脉冲控制信号p2_c和第一第三路脉冲控制信号p1_c;第十五nmos晶体管mn15的栅极和第十六nmos晶体管mn16的栅极分别连接第一第四路脉冲控制信号p1_d和第二第四路脉冲控制信号p2_d。参见附图6,附图6示出了期望差分信号经由预加重电路优化(with pre-emphasis)和不经由预加重电路优化(without pre-emphasis)的比较示意图,期望差分信号经过预加重之后可以在转换期间引入高频分量。其中,vdp和vdn例如可以分别为第一期望差分信号outn和第二期望差分信号outp的幅度。脉冲控制信号分别在预驱动控制信号转换期间控制对应晶体管的导通关断,使期望输出信号在转换期间幅度增大,增加数据

高频分量,实现预加重功能。

40.如附图7所示,本发明还提供了一种可扩展低压信令标准的驱动器的驱动方法,包括:步骤901:将输入信号经由单端转差分电路转换为第一差分信号;步骤902:第一差分信号经由电平转换电路转换第一差分信号的电压;步骤903:第一差分信号经由边缘对齐电路和预驱动电路,将第一差分信号转换为第二差分信号;步骤904:通过第二差分信号驱动主体驱动电路输出期望差分信号;其中,第一差分信号还经由预加重电路,提高期望差分信号的高频分量幅度;期望差分信号还经由共模反馈电路,稳定期望差分信号的共模电压。

41.第一差分信号还经由预加重电路,提高期望差分信号的高频分量幅度,包括:第一差分信号经由脉冲生成电路,检测第一差分信号的上升沿产生脉冲控制信号,脉冲控制信号用于驱动预加重电路。

42.主体驱动电路包括开关控制路径与共模调节路径,开关控制路径与共模调节路径并联。如此,可有效节省器件的面积。结合附图4,第一nmos晶体管mn1和第三nmos晶体管mn3所在的支路为开关控制路径,第五nmos晶体管mn5所在的支路为共模调节路径。

43.使能该slvs驱动器之后,数据输入信号后经由单端转差分电路转换为第一差分信号,第一差分信号经由电平转换电路由内核电平转换为io电平输出,此输出信号一方面经由预驱动电路生成控制信号来控制主体驱动电路的开关管,同时经由脉冲生成电路检测其上升沿,产生脉冲信号用以控制预加重电路,以此补偿信号在信道中的高频衰减成分。共模反馈电路接收驱动器输出的共模电平并与标准共模电平比较之后输出控制信号调节驱动器的晶体管阻抗。

44.综上,本发明提供了一种可扩展低压信令标准的驱动器,通过共模反馈电路调节期望差分信号的共模电压,利用预加重电路补偿信号在传输过程中高频衰减,以提高输出期望差分信号的质量。且本发明通过并联开关控制路径与共模调节路径以节省晶体管面积,其中共模调节路径使用共模反馈至尾部nmos管可以始终维持共模电平的较高精度,使用t形去耦电容减少输出信号在转换期间的超调量。

45.本发明为了便于叙述清楚而采用的一些常用的英文名词或字母只是用于示例性指代而非限定性解释或特定用法,不应以其可能的中文翻译或具体字母来限定本发明的保护范围。

46.还需要说明的是,在本文中,诸如“第一”和“第二”等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1