高速串行接口无时钟线应用下的并行化解码装置及方法与流程

本发明涉及现场可编程逻辑门阵列(field programmable gate array,fpga)芯片,特别涉及高速串行接口无时钟线应用下的并行化解码装置及方法。

背景技术:

1、fpga芯片是在可编程阵列逻辑、通用阵列逻辑等可编程器件的基础上进一步发展的产物。在fpga芯片领域,有串行通信方式以及并行通信方式之分。其中,并行通信系统一般采用时钟+数据的并行接口实现,而串行通信系统,则采用单端io(input/output,输入输出)、差分io以及专用高速收发io中的一种方式实现。

2、其中,差分io主要基于低电压差分信号(low-voltage differential signaling,lvds)技术,上升沿较小,在发送端提供随路时钟的情况下,线速率最高可以达到1.25gbps,是较为理想的通讯方式。

3、然而,在应用场景内无法提供时钟线的情况,例如50m-550mbps的数据通信场景下,对于宽带需求中等,但要求成本低,使用线缆少,因此无法增加与随路时钟对应的线缆。在此情况下,暂无合适的fpga芯片设计方式。

技术实现思路

1、本发明的目的在于克服已有技术中存在的不足,从而提供高速串行接口无时钟线应用下的并行化解码装置及方法,以适配宽带需求中等,但要求成本低,使用线缆少,无法应用随路时钟线缆场景的情况。该技术方案如下:

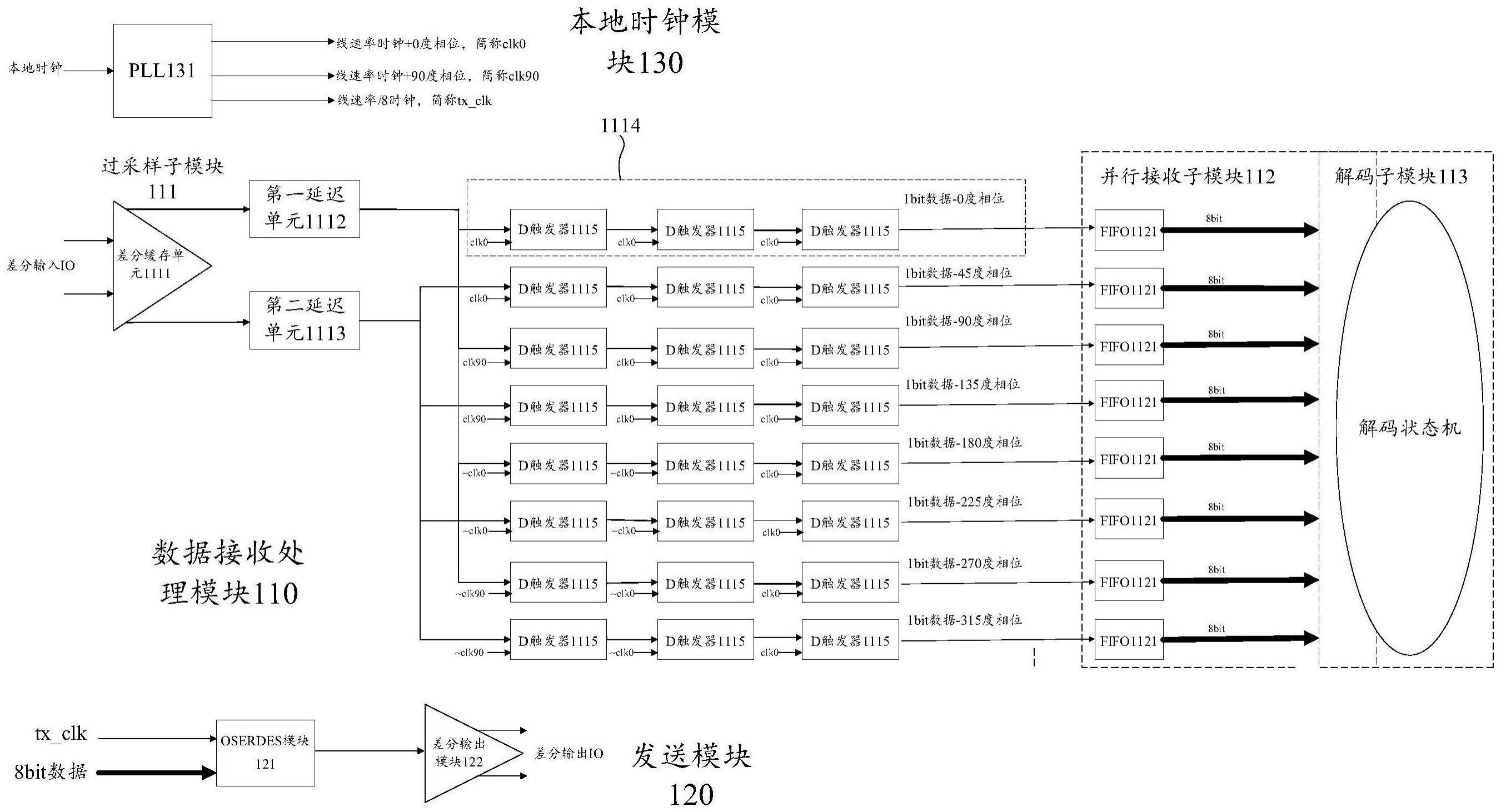

2、一方面,提供了一种高速串行接口无时钟线应用下的并行化解码装置,该装置包括数据接收处理模块、数据发送模块以及本地时钟模块;

3、本地时钟模块分别与数据接收处理模块以及数据发送模块连接;

4、数据接收处理模块的数据输出端与数据发送模块的数据输入端连接;

5、数据接收处理模块包括过依次连接的过采样子模块、并行接收子模块以及解码子模块;

6、过采样子模块中包括差分缓存单元、第一延迟单元、第二延迟单元以及8路采样单元,每路采样单元中包括3个d触发器;

7、并行接收模块中包括8路先进先出(first input first output,fifo)存储器,每路fifo存储器与每路采样单元对应连接;

8、解码子模块包括解码状态机,解码状态机用于输出并行数据;

9、数据发送模块包括oserdes子模块以及差分输出子模块,oserdes子模块用于进行并串转换;

10、本地时钟模块包括锁相回路(phase-locked loop,pll)模块,pll模块包括1/8时钟输出端以及两个相位输出端,1/8时钟输出端与数据发送模块连接,两个相位输出端与接收模块连接。

11、另一方面,提供了一种高速串行接口无时钟线应用下的并行化解码方法,该方法应用于如上所述的高速串行接口无时钟线应用下的并行化解码装置中,该方法包括:

12、将初始数据输入数据接收处理模块,并经过差分缓存模块;

13、将经过差分缓存模块的初始数据经过第一延迟单元以及第二延迟单元,输出得到0ps延迟数据和1/8线速率延迟数据;

14、将0ps延迟数据以及1/8线速率延迟数据分别通过8路采样单元,同时通过时钟模块的两个相位输出端调节采样单元中d触发器的工作相位,得到8路相位数据;

15、通过8路fifo存储器对于8路相位数据进行缓存;

16、响应于缓存完成,通过8路相位数据向状态解码机并行输出数据,并通过状态解码机进行同步解码,得到并联式8bit数据;

17、将并行式8bit数据发送至数据发送模块,并配置本地时钟模块的1/8时钟输出端输出的1/8时钟信号;

18、通过oserdes子模块接收并行式8bit数据以及1/8时钟信号,输出串行数据;

19、将串行数据通过差分输出子模块,输出差分输出信号。

20、本发明提供的技术方案带来的有益效果至少包括:

21、在时钟模块本地化的情况下,对应设置数据接收处理模块以及数据发送模块,并在数据接收处理模块中,以过采样的方法,结合时钟模块的相位调节,实现8路相位数据的采集以及统一解码,并通过发送模块进行数据的并串转换,最终将稳定性高的并行解码与串行数据输出相结合。在无时钟对应线缆的情况下,适配通用化的通信需求,实现了串行数据的稳定输出。

技术特征:

1.一种高速串行接口无时钟线应用下的并行化解码装置,其特征在于,所述装置包括数据接收处理模块、数据发送模块以及本地时钟模块;

2.根据权利要求1所述的高速串行接口无时钟线应用下的并行化解码装置,其特征在于,所述两个相位输出端的相位差为90度。

3.根据权利要求2所述的高速串行接口无时钟线应用下的并行化解码装置,其特征在于,所述两个相位输出端分别与每个所述d触发器连接。

4.根据权利要求1所述的高速串行接口无时钟线应用下的并行化解码装置,其特征在于,所述第一延迟单元的延迟为0,所述第二延迟单元的延迟为1/8线速率。

5.一种高速串行接口无时钟线应用下的并行化解码方法,其特征在于,所述方法应用于如权利要求1至4所述的高速串行接口无时钟线应用下的并行化解码装置中,所述方法包括:

6.根据权利要求5所述的高速串行接口无时钟线应用下的并行化解码方法,其特征在于,8路相位数据的相位差分别为0度、45度、90度、135度、180度、225度、270度以及315度。

7.根据权利要求5所述的高速串行接口无时钟线应用下的并行化解码方法,其特征在于,所述通过所述状态解码机进行同步解码,得到并联式8bit数据,包括:

8.根据权利要求7所述的高速串行接口无时钟线应用下的并行化解码方法,其特征在于,所述方法还包括;

9.根据权利要求7所述的高速串行接口无时钟线应用下的并行化解码方法,其特征在于,信号抖动限定值的数值范围为4至8。

技术总结

本发明关于高速串行接口无时钟线应用下的并行化解码装置及方法,涉及FPGA芯片应用领域。该装置包括数据接收处理模块、数据发送模块以及本地时钟模块。数据接收处理模块包括依次连接的过采样子模块、并行接收子模块以及解码子模块;数据发送模块包括OSERDES子模块以及差分输出子模块。本地时钟模块包括PLL模块。该装置以过采样的方法,结合时钟模块的相位调节,实现8路相位数据的采集以及统一解码,并通过发送模块进行数据的并串转换,最终将稳定性高的并行解码与串行数据输出相结合。在无时钟对应线缆的情况下,适配通用化的通信需求,实现了串行数据的稳定输出。

技术研发人员:官剑,韩留军,邵春伟,郝国锋,薛培,沈小波

受保护的技术使用者:无锡华普微电子有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!