一种占空比可调电路、芯片及电子设备的制作方法

本技术涉及芯片领域,具体而言,涉及一种占空比可调电路、芯片及电子设备。

背景技术:

1、大规模集成电路中,时钟信号驱动所有的时序逻辑器件,决定着芯片的工作频率。随着芯片的工作频率越来越高,时钟信号的质量要求也越来越高,一般需要高速、低抖动、高精度的时钟信号。某些电路设计中,还需要根据特定的设计需求,对时钟信号的占空比做出调整,产生特定占空比的时钟信号。

2、随着时钟信号的传输,电路中的电源噪声或者是信号噪声,会使得时钟信号的占空比偏离50%。信号传输的距离越长,偏离的程度越高,到达时序逻辑器件时,时钟信号的占空比可能已经严重偏离50%,这种时钟信号会极大的影响整个芯片的性能,所以需要在时钟信号到达时序逻辑器件前,对时钟信号进行矫正,使得时钟信号在远距离传输时,占空比重新回到50%。

3、某些数字电路设计时,会使用特定占空比的时钟信号,这种时钟信号占空比不等于50%,可能等于20%或者80%,如何产生这种高精度的时钟信号,也是芯片设计的一个难题。

4、不仅如此,在电路设计中,可能会存在需要根据设计的功能,动态调整时钟信号的占空比的情况。例如,如果在测试中发现某些占空比不能满足设计要求,需要快速切换到另外一种占空比的时钟信号,以满足芯片的功能。

5、针对以上这些情况,就要求提供一种可以实现信号占空比能够准确受控调整的电路。

技术实现思路

1、本技术实施例的目的在于提供一种可以实现信号占空比能够准确受控调整的占空比可调电路、芯片、电子部件及电子设备。

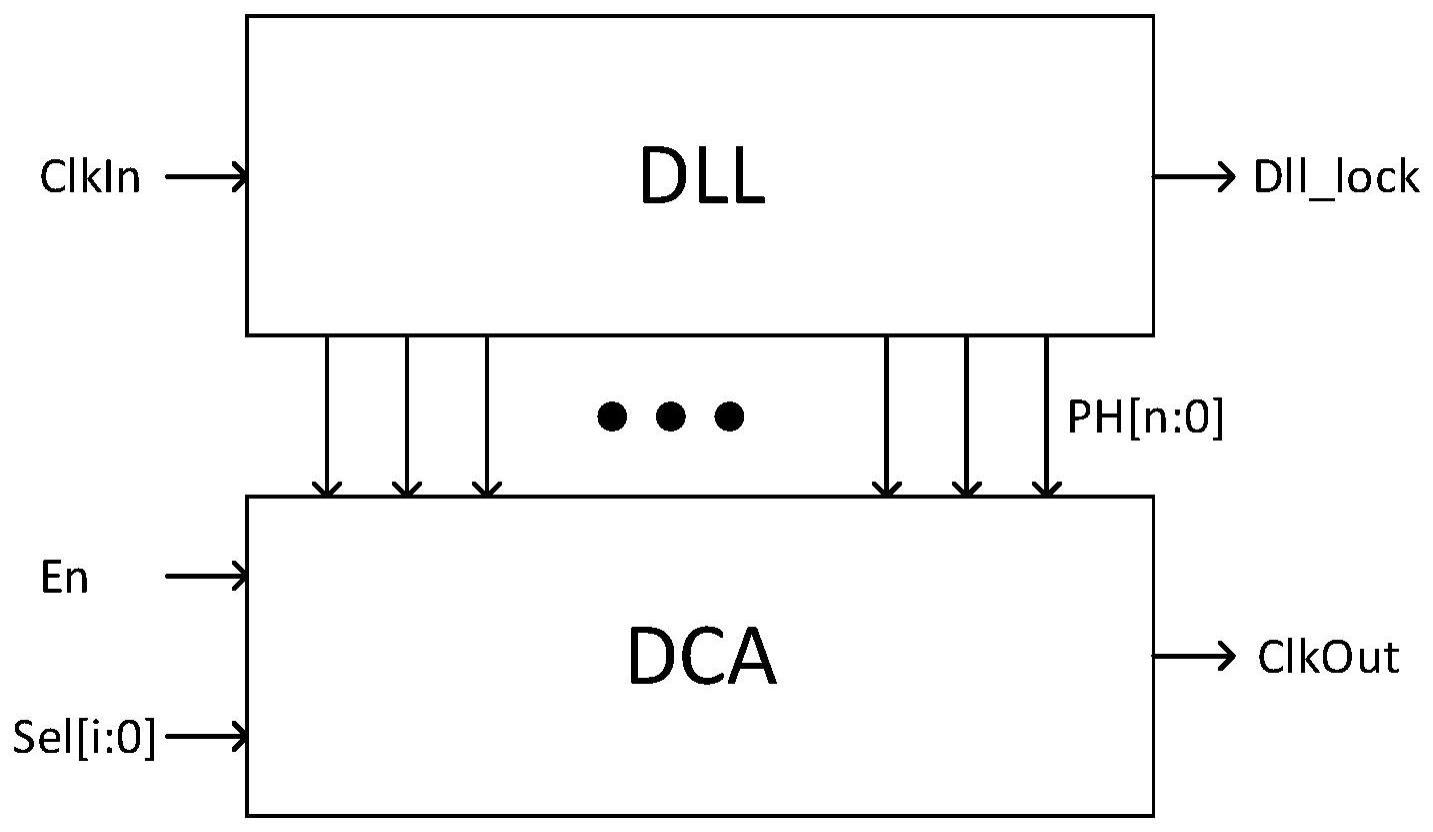

2、本技术实施例提供了一种占空比可调电路,包括:延迟锁相环电路,被配置为接收原始时钟信号,并对所述原始时钟信号进行延迟产生n个相位等差的第一时钟信号;所述n为大于等于2的正整数;占空比调节电路,与所述延迟锁相环电路电连接,并被配置为接收占空比选择信号,并根据所述占空比选择信号从n个所述第一时钟信号中选择两个目标第一时钟信号,以根据两个所述目标第一时钟信号生成第二时钟信号;所述第二时钟信号具有设定的占空比。

3、在上述实现结构中,通过延迟锁相环电路可以稳定地产生出n个相位等差的第一时钟信号,进而通过占空比调节电路根据占空比选择信号从中选择出两个目标第一时钟信号,基于目标第一时钟信号进行最终的第二时钟信号的生成第二时钟信号。而可以理解,在占空比调节电路确定的情况下,两个目标第一时钟信号直接的相位差是确定的,那么对应可生成的第二时钟信号的占空比也就是确定的,且随着两个目标第一时钟信号直接的相位差的不同,可生成的第二时钟信号的占空比也会不同,例如基于两个相位相差(n-1/2)个时钟周期的目标第一时钟信号可以生成的占空比为50的第二时钟信号,又例如基于两个相位相差(1/(n-1))个时钟周期的目标第一时钟信号可以生成的占空比为(1/(n-1))的第二时钟信号。因此,基于本技术实施例所提供的占空比可调电路,只需根据需要向占空比可调电路中输出对应的占空比选择信号,即可使得占空比可调电路产生所需占空比的第二时钟信号,实现时钟信号的准确受控调整,无论是针对需要根据特定的设计需求,对时钟信号的占空比做出调整,产生特定占空比的时钟信号这一场景,还是针对时钟信号在远距离传输时的时钟信号矫正这一场景,还是针对如何产生高精度特定占空比的时钟信号这一场景,还是针对多种占空比的时钟信号需要快速切换的场景,基于本技术的上述实现方式都可以满足,本技术的上述实现方式具有非常强的普适性。

4、进一步地,所述延迟锁相环电路包括:原始时钟信号输入端,用于接收所述原始时钟信号;延迟链,包括多个与所述原始时钟信号输入端顺序串联的延迟单元电路;状态机,分别与各所述延迟单元电路的连接,以调整各所述延迟单元电路的延迟值。

5、在上述实现过程中,通过多个与所述原始时钟信号输入端顺序串联的延迟单元电路,并通过状态机调整各延迟单元电路的延迟值,这就可以通过状态机的设置使得各第一时钟信号之间的相位差是固定在一个设计出的相位差上的,从而保证后续可以基于对第一时钟信号的选择产生所需占空比的第二时钟信号。

6、进一步地,所述延迟锁相环电路还包括:相位检测器,分别与所述延迟链中第一级所述延迟单元电路的信号输入端、最后一级所述延迟单元电路的信号输出端、以及所述状态机连接,用于在输入至所述延迟链中第一级所述延迟单元电路中的信号与所述延迟链中最后一级所述延迟单元电路输出的所述第一时钟信号的相位相差一个时钟周期时,向所述状态机输出锁定信号;所述状态机用于逐步增大各所述延迟单元电路的延迟值,并在接收到所述锁定信号时维持各所述延迟单元电路的延迟值。

7、在上述实现方式中,通过相位检测器的作用可以将相邻第一时钟信号之间的相位差控制为(1/(n-1))个时钟周期,从而便于进行目标第一时钟信号的选取。

8、进一步地,所述延迟单元电路包括:并联的缓冲器和可调电容,且所述可调电容与所述状态机连接。

9、在上述实现方式中,状态机通过控制可调电容的值即可有效调整整个延迟单元电路的延迟值,实现延迟单元电路的受控调整,实现结构简单。

10、进一步地,所述占空比调节电路包括:第一多路选择器,信号输入端分别与所述延迟锁相环电路中各所述第一时钟信号的信号输出端连接,且所述第一多路选择器的使能端并被配置为接收所述占空比选择信号,以使所述第一多路选择器根据所述占空比选择信号选择两个所述目标第一时钟信号输出;时钟信号产生电路,与所述第一多路选择器的信号输出端连接,以根据两个所述目标第一时钟信号生成所述第二时钟信号。

11、在上述实现方式中,通过第一多路选择器的作用即可实现基于占空比选择信号对于目标第一时钟信号的选择,进而通过时钟信号产生电路即可生成第二时钟信号,实现结构简单、可靠。

12、进一步地,所述时钟信号产生电路包括:第二多路选择器,所述第二多路选择器的信号输入端分别与所述第一多路选择器的两个信号输出端连接;触发器,所述触发器的时钟信号输入端与所述第二多路选择器的信号输出端连接,所述触发器的数据输出端通过反相器与所述触发器的数据输入端连接;所述第二多路选择器的使能端与所述触发器的数据输入端连接。

13、在上述实现方式中,触发器初始时数据输出端输出的信号处于低电平,经过反相器之后,输出高电平,使得触发器的数据输入端的信号din等于1,第二多路选择器将第一个目标第一时钟信号发送到触发器的时钟信号输入端。正工作时,第一个目标第一时钟信号上升沿触发触发器将din传输到数据输出端,数据输出端输出的gclk信号从低电平翻转为高电平,高电平再经过反相器后,输出低电平,使得din等于0,从而使得第二多路选择器将第二个目标第一时钟信号传输到触发器的时钟信号输入端口。

14、随着时间的推移,第二个目标第一时钟信号上升沿触发触发器将din信号传输到数据输出端,gclk信号从高电平翻转为低电平。gclk信号经过反相器后,输出高电平,使得din等于1,将第一个目标第一时钟信号传输到触发器的时钟信号输入端口。然后再延迟第一个目标第一时钟信号的上升沿到来的时间之后,第一个目标第一时钟信号的上升沿触发触发器将din信号传输到数据输出端,gclk信号从低电平翻转为高电平。不断重复该过程,即可使得gclk信号具有特定的占空比。可见,该结构可以有效实现第二时钟信号的产生,且该结构实现简单,利于在芯片中实施。

15、进一步地,所述占空比调节电路还包括:第三多路选择器,所述第三多路选择器的一个信号输入端与所述触发器的数据输出端连接,所述第三多路选择器的另一个信号输入端被配置为接收所述原始时钟信号;所述第三多路选择器的使能端被配置为接收使能信号,且所述触发器的使能端也被配置为接收所述使能信号。

16、在上述实现方式中,通过第三多路选择器和使能信号的作用,可以在触发器未使能时输出原始时钟信号,保证时钟信号的正确传输。

17、进一步地,所述时钟信号产生电路包括:第一脉冲产生电路,所述第一脉冲产生电路的信号输入端与所述第一多路选择器的一个信号输出端连接;第二脉冲产生电路,所述第二脉冲产生电路的信号输入端与所述第一多路选择器的另一个信号输出端连接;锁存器,所述锁存器的置位端口与所述第一脉冲产生电路的信号输出端连接,所述锁存器的复位端口与所述第二脉冲产生电路的信号输出端连接。

18、在上述实现方式中,经过第一脉冲产生电路和第二脉冲产生电路可以产生脉冲时钟信号,由于第一脉冲产生电路和第二脉冲产生电路是分别基于第一个目标第一时钟信号和第二个目标第一时钟信号产生的脉冲时钟信号,因此两个脉冲时钟信号之间的上升沿间隔等于两个目标第一时钟信号之间的相位差,从而驱动锁存器后,即可以产生与两个目标第一时钟信号之间的相位差相关的特定占空比的时钟信号。可见,该结构可以有效实现第二时钟信号的产生,且该结构实现简单,利于在芯片中实施。

19、进一步地,所述占空比调节电路还包括:第四多路选择器,所述第四多路选择器的一个信号输入端与所述触发器的信号输出端连接,所述第四多路选择器的另一个信号输入端被配置为接收所述原始时钟信号,所述第四多路选择器的使能端被配置为接收使能信号;所述锁存器的置位端口和复位端口被配置为通过反相器接收所述使能信号。

20、在上述实现方式中,通过第四多路选择器和使能信号的作用,可以在锁存器未使能时输出原始时钟信号,保证时钟信号的正确传输。

21、本技术实施例还提供了一种芯片,包括前述任一种的占空比可调电路。

22、本技术实施例还提供了一种电子设备,包括前述芯片。

- 还没有人留言评论。精彩留言会获得点赞!