一种比较器、模数转换器和半导体芯片的制作方法

本技术实施例涉及集成电路,尤其涉及一种比较器、模数转换器和半导体芯片。

背景技术:

1、sigma-delta模数转换器是一种可以将模拟信号转换为数字信号的器件,sigma-delta模数转换器的工作过程中,会产生一种量化误差。sigma-delta模数转换器中积分器的输出端电连接比较器的输入端,可以向积分器的输出信号添加抖动信号,使得比较器基于添加抖动信号的积分输出信号进行比较,能够降低sigma-delta模数转换器工作过程中产生的量化误差,提升sigma-delta模数转换器的精度。

2、现有技术中,sigma-delta模数转换器电路包括积分器和比较器,可以在积分器和比较器之间加入加法器,通过加法器加入抖动信号。同样,在其他类型的半导体器件中,可以在比较器之前加入加法器,通过加法器向输入至比较器的信号中加入抖动信号。

3、然而,采用现有技术需要在半导体器件中添加另外的加法器,导致器件的面积较大,成本较高。

技术实现思路

1、鉴于上述问题,本技术实施例提供了一种比较器、模数转换器和半导体芯片,能够在比较器中集成添加抖动信号的功能,无需在半导体器件中添加另外的加法器,从而能够降低器件的面积和成本。

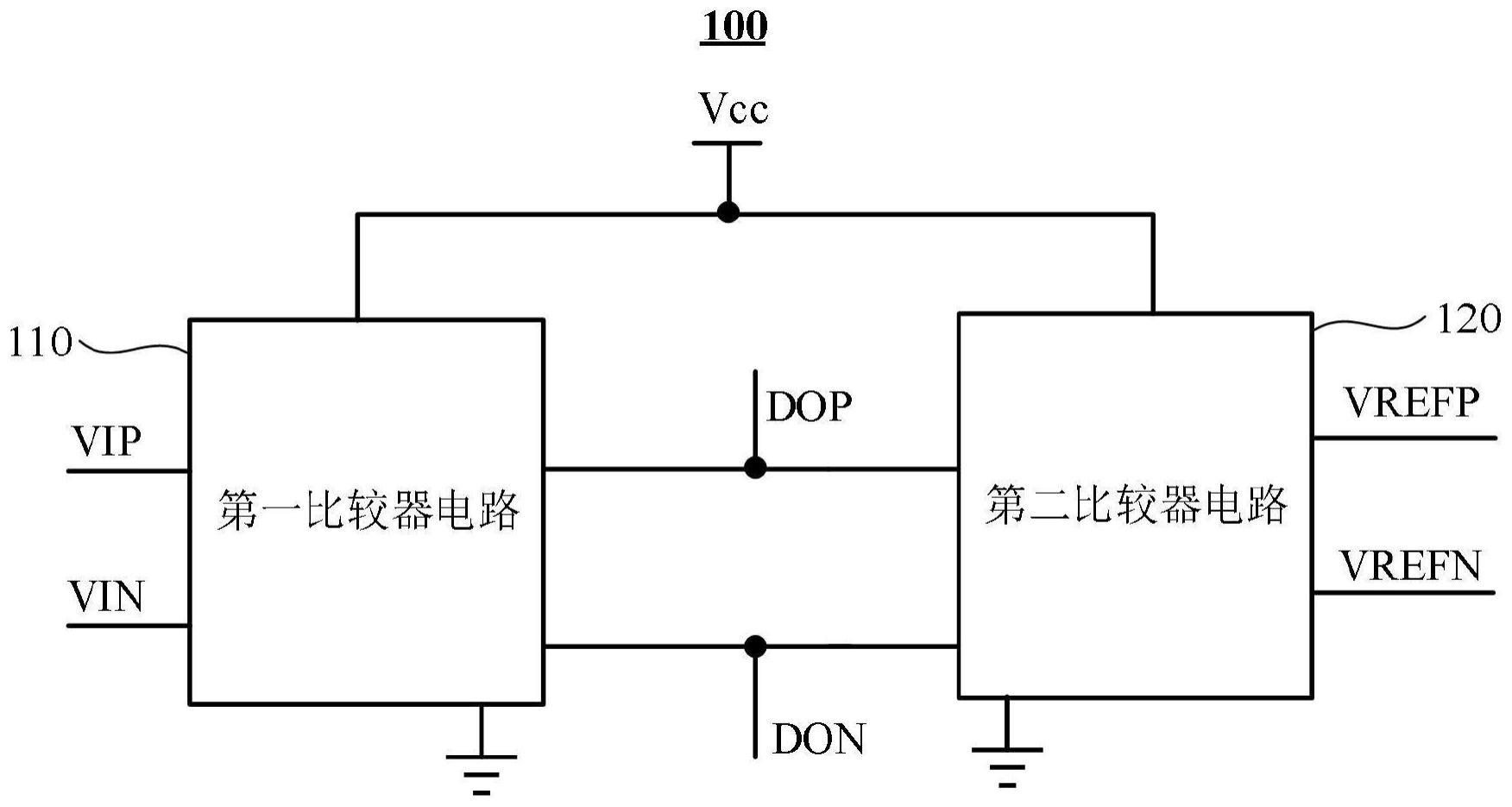

2、第一方面,本技术实施例提供了一种比较器,包括:第一比较器电路和第二比较器电路;

3、所述第一比较器电路的第一输入端电连接正输入电压信号,所述第一比较器电路的第二输入端电连接负输入电压信号,所述第二比较器电路的第一输入端电连接正参考电压信号,所述第二比较器电路的第二输入端电连接负参考电压信号,所述第一比较器电路的电源输入端和所述第二比较器电路的电源输入端均电连接电源正电压,所述第一比较器电路的电源输出端和所述第二比较器电路的电源输出端均接地,所述第一比较器电路的第一输出端和所述第二比较器电路的第一输出端均电连接所述比较器的第一输出端,所述第一比较器电路的第二输出端和所述第二比较器电路的第二输出端均电连接所述比较器的第二输出端;其中,所述正输入电压信号和所述负输入电压信号为一组差分信号,所述正参考电压信号和所述负参考电压信号为一组差分信号;

4、所述比较器,用于将所述正输入电压信号与所述正参考电压信号进行叠加得到正电压信号,将所述负输入电压信号与所述负参考电压信号进行叠加得到负电压信号,并对所述正电压信号和所述负电压信号进行比较。

5、一些实施例中,所述第一比较器电路包括第一开关管组件、第二开关管组件和第三开关管组件;

6、所述第一开关管组件的第一端和所述第二开关管组件的第一端均电连接所述电源正电压,所述第一开关管组件的第二端和所述第二开关管组件的第一控制端均电连接所述第一比较器电路的第一输出端,所述第一开关管组件的第三端和所述第二开关管组件的第二控制端均电连接所述第一比较器电路的第二输出端,所述第一开关管组件的第四端电连接所述第二开关管组件的第二端和所述第三开关管组件的第一端,所述第一开关管组件的第五端电连接所述第二开关管组件的第三端和所述第三开关管组件的第二端,所述第一开关管组件的控制端电连接时钟信号;

7、所述第三开关管组件的第一控制端电连接所述正输入电压信号,所述第三开关管组件的第二控制端电连接所述负输入电压信号,所述第三开关管组件的第三控制端电连接所述时钟信号,所述第三开关管组件的第三端接地。

8、一些实施例中,所述第一开关管组件包括第一开关管、第二开关管、第三开关管和第四开关管;

9、所述第一开关管的第一端、所述第二开关管的第一端、所述第三开关管的第一端和所述第四开关管的第一端均电连接所述电源正电压,所述第一开关管的第二端电连接所述第二开关管组件的第一控制端,所述第三开关管的第二端电连接所述第二开关管组件的第二控制端,所述第二开关管的第二端电连接所述第三开关管组件的第一端,所述第四开关管的第二端电连接所述第三开关管组件的第二端,所述第一开关管的控制端、所述第二开关管的控制端、所述第三开关管的控制端和所述第四开关管的控制端均电连接时钟信号。

10、一些实施例中,所述第二开关管组件包括第五开关管、第六开关管、第七开关管和第八开关管;

11、所述第五开关管的第一端和所述第六开关管的第一端均电连接所述电源正电压,所述第五开关管的第二端电连接所述第七开关管的第一端、所述第六开关管的控制端、所述第八开关管的控制端和所述第一比较器电路的第一输出端,所述第六开关管的第二端电连接所述第五开关管的控制端、所述第七开关管的控制端、所述第八开关管的第一端和所述第一比较器电路的第二输出端,所述第七开关管的第二端电连接所述第三开关管组件的第一端,所述第八开关管的第二端电连接所述第三开关管组件的第二端。

12、一些实施例中,所述第三开关管组件包括第九开关管、第十开关管和第十一开关管;

13、所述第九开关管的第一端电连接所述第二开关管组件的第二端,所述第十开关管的第一端电连接所述第二开关管组件的第三端,所述第九开关管的控制端电连接所述负输入电压信号,所述第十开关管的控制端电连接所述正输入电压信号,所述第九开关管的第二端和所述第十开关管的第二端均电连接所述第十一开关管的第一端,所述第十一开关管的第二端接地,所述第十一开关管的控制端电连接所述时钟信号。

14、一些实施例中,所述第二比较器电路包括第四开关管组件、第五开关管组件和第六开关管组件;

15、所述第四开关管组件的第一端和所述第五开关管组件的第一端均电连接所述电源正电压,所述第四开关管组件的第二端电连接所述第五开关管组件的第二端和所述第六开关管组件的第一端,所述第四开关管组件的第三端电连接所述第五开关管组件的第三端和所述第六开关管组件的第二端,所述第四开关管组件的控制端电连接所述时钟信号;

16、所述第五开关管组件的第一控制端电连接所述第二比较器电路的第一输出端,所述第五开关管的第二控制端电连接所述第二比较器电路的第二输出端;

17、所述第六开关管组件的第一控制端电连接所述正参考电压信号,所述第六开关管组件的第二控制端电连接所述负参考电压信号,所述第六开关管组件的第三控制端电连接所述时钟信号,所述第六开关管组件的第三端接地。

18、一些实施例中,所述第四开关管组件包括第十二开关管和第十三开关管;

19、所述第十二开关管的第一端和所述第十三开关管的第一端均电连接所述电源正电压,所述第十二开关管的第二端电连接所述第六开关管组件的第一端,所述第十三开关管的第二端电连接所述第六开关管组件的第二端,所述第十二开关管的控制端和所述第十三开关管的控制端均电连接所述时钟信号。

20、一些实施例中,所述第五开关管组件包括第十四开关管、第十五开关管、第十六开关管和第十七开关管;

21、所述第十四开关管的第一端和所述第十五开关管的第一端均电连接所述电源正电压,所述第十四开关管的第二端电连接所述第十六开关管的第一端、所述第十五开关管的控制端、所述第十七开关管的控制端和所述第二比较器电路的第一输出端,所述第十五开关管的第二端电连接所述第十四开关管的控制端、所述第十六开关管的控制端、所述第十七开关管的第一端和所述第二比较器电路的第二输出端,所述第十六开关管的第二端电连接所述第六开关管组件的第一端,所述第十七开关管的第二端电连接所述第六开关管组件的第二端。

22、一些实施例中,所述第六开关管组件包括第十八开关管、第十九开关管和第二十开关管;

23、所述第十八开关管的第一端电连接所述第五开关管组件的第二端,所述第十九开关管的第一端电连接所述第五开关管组件的第三端,所述第十八开关管的控制端电连接所述负参考电压信号,所述第十九开关管的控制端电连接所述正参考电压信号,所述第十八开关管的第二端和所述第十九开关管的第二端均电连接所述第二十开关管的第一端,所述第二十开关管的第二端接地,所述第二十开关管的控制端电连接所述时钟信号。

24、第二方面,本技术实施例提供了一模数转换器,包括:第一方面提供的任一比较器。

25、第三方面,本技术实施例提供了一种半导体芯片,包括:第二方面提供的任一模数转换器。

26、本技术实施例的技术方案中,比较器包括第一比较器电路和第二比较器电路,第一比较器电路的第一输入端电连接正输入电压信号,第一比较器电路的第二输入端电连接负输入电压信号,第二比较器电路的第一输入端电连接正参考电压信号,第二比较器电路的第二输入端电连接负参考电压信号,第一比较器电路的电源输入端和第二比较器电路的电源输入端均电连接电源正电压,第一比较器电路的电源输出端和第二比较器电路的电源输出端均接地,第一比较器电路的第一输出端和第二比较器电路的第一输出端均电连接比较器的第一输出端,第一比较器电路的第二输出端和第二比较器电路的第二输出端均电连接比较器的第二输出端;其中,正输入电压信号和负输入电压信号为一组差分信号,正参考电压信号和负参考电压信号为一组差分信号。通过比较器能够将正输入电压信号与正参考电压信号进行叠加得到正电压信号,将负输入电压信号与负参考电压信号叠加得到负电压信号,并对正电压信号和负电压信号进行比较,如此,将正参考电压信号和负参考电压信号组成的差分信号作为抖动信号,将正输入电压信号和负输入电压信号组成的差分信号作为输入至比较器的信号,可以将输入至比较器的信号和抖动电压信号进行叠加,能够在比较器中集成添加抖动信号的功能,故而无需在半导体器件中添加另外的加法器,从而能够降低器件的面积和成本。

27、上述说明仅是本技术实施例技术方案的概述,为了能够更清楚了解本技术实施例的技术手段,而可依照说明书的内容予以实施,并且为了让本技术实施例的上述和其它目的、特征和优点能够更明显易懂,以下特举本技术的具体实施方式。

- 还没有人留言评论。精彩留言会获得点赞!