移相器电路和装置的制作方法

移相器电路和装置

1.相关申请的交叉引用

2.本技术要求2021年1月15日提交的题为“移相器180度拓扑”的美国临时专利申请第63/138054号的优先权和利益,通过引用将其全部纳入其中,如充分阐述下文和所有适用的目的。

技术领域

3.本公开一般涉及集成电路,更具体地说,涉及移相器(例如,在相控阵系统中)。

背景技术:

4.移相器和真实时间延迟(ttd)组件通常用于高频系统,尤其是毫米波段,用于信号调整。虽然信号的相位延迟或定时延迟基本相同,但移相器和tdd延迟线的设计目标不同。例如,移相器可在设计频率范围内提供频率上的信号调整,而tdd延迟线可在设计频率范围内提供时间上的信号调整。在一些示例中,移相器可能更适合于调整带宽较窄的信号,而ttd延迟线可能更适合于调整带宽较宽的信号。

5.利用移相器的一些示例系统和/或设备可包括无线通信系统,例如长期演进(lte)和第五代(5g),其在约3千赫兹(khz)到300千兆赫兹(ghz)的射频(rf)范围内以电磁波的形式发送和接收信号。例如,无线通信系统可利用相控阵天线系统(其也可被称为电可控阵列(esa))进行无线发射和接收。相控阵天线系统可包括天线单元阵列(例如,约64、128、256、1024或更多)。单个天线单元可以发射相同频率的信号,但是阵列中的每个天线单元之间具有一定的相移。可以计算相移以在期望的空间方向上提供建设性干扰,而在其他方向上可能发生破坏性干扰。这样,来自天线元件的组合发射信号可以在期望的空间方向上提供更好的增益、方向性和性能。换言之,天线元件的相位受到控制,以迫使电磁波以特定角度与阵列相加。为此,相位天线阵列系统可利用移相器来移相将由天线元件发射的信号。调整由阵列中的天线元件发射的信号的相位的过程可称为波束形成。相移可以在0度到360度之间的任何位置变化。180度的相移(其中移相器提供相位差为180度的两个输出相态)可能是各种相移中最具挑战性的设计,例如,就插入损耗、可操作带宽和/或可操作带宽上的相位平坦度而言。因此,提供180度移相器的技术改进可能是可取的。

技术实现要素:

6.根据本公开的一个方面,提供了一种移相器电路,该移相器电路包括:第一节点;第二节点;耦合在所述第一节点和所述第二节点之间的第一信号路径,所述第一信号路径包括正耦合变压器;在所述第一节点和所述第二节点之间的第二信号路径,所述第二信号路径包括负耦合变压器;和多个开关,用于选择所述第一信号路径或所述第二信号路径。

7.在一个实施例中,所述正耦合变压器的初级线圈两端的电压和所述正耦合变压器的次级线圈两端的电压同相;和所述负耦合变压器的初级线圈两端的电压和所述负耦合变压器的次级线圈两端的电压不同相。

8.在一个实施例中,所述多个开关的第一开关耦合在所述第一节点和所述正耦合变压器之间,并响应于第一控制信号;和所述多个开关的第二开关耦合在所述第一节点和所述负耦合变压器之间,并响应于第二控制信号。

9.在一个实施例中,与所述第一信号路径相关联的第一控制信号和与所述第二信号路径相关联的第二控制信号具有相反的相位。

10.在一个实施例中,所述移相器电路还包括:耦合到所述第一信号路径的分流路径,其中,所述多个开关的第三开关设置在所述分流路径上,并响应于所述第二控制信号。

11.在一个实施例中,所述第一开关或所述第二开关中的至少一个包括一个或多个场效应晶体管(fet)。

12.在一个实施例中,所述正耦合变压器和所述负耦合变压器具有不同的尺寸。

13.在一个实施例中,所述移相器电路还包括:耦合在所述正耦合变压器的初级线圈和次级线圈两端的电容器。

14.在一个实施例中,所述移相器电路还包括以下至少一种:与所述正耦合变压器的初级线圈或次级线圈并联的电容器;或与所述负耦合变压器的初级线圈或次级线圈并联的电容器。

15.在一个实施例中,所述移相器电路是180度移相器电路。

16.在一个实施例中,所述移相器电路是多位移相器电路。

17.根据本公开的另一个方面,提供了一种装置,该装置包括:第一移相器,包括:第一节点,用于接收输入信号;第二节点;耦合在所述第一节点和所述第二节点之间的第一信号路径,所述第一信号路径包括正耦合变压器;耦合在所述第一节点和所述第二节点之间的第二信号路径,所述第二信号路径包括负耦合变压器,其中所述第二信号路径与所述第二节点处的所述第一信号路径不同相;和多个开关,用于选择所述第一信号路径或所述第二信号路径。

18.在一个实施例中,所述第一移相器还包括以下至少一个:耦合在所述正耦合变压器的初级线圈两端的第一电容器;耦合在所述正耦合变压器的次级线圈两端的第二电容器;耦合在所述负耦合变压器的初级线圈两端的第三电容器;或耦合在所述负耦合变压器的次级线圈两端的第四电容器。

19.在一个实施例中,所述装置还包括:与所述第一移相器串联的第二移相器。

20.在一个实施例中,所述第一移相器响应于第一控制位;和所述第二移相器响应于与所述第一控制位分离的第二控制位。

21.在一个实施例中,该装置为相控阵系统;和该装置还包括:天线阵列;和耦合到所述天线阵列的多个移相器,所述多个移相器包括所述第一移相器。

附图说明

22.为了更全面地理解本公开及其特征和优点,结合附图参考以下描述,其中相同的附图标记代表相同的部分,其中:

23.图1是说明示例性基于开关滤波器的移相器电路的示意图;

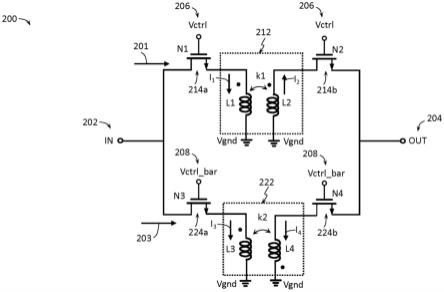

24.图2a是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路的示意图;

25.图2b是图示根据本公开的一些实施例的图2a的基于开关变压器的移相器电路的更详细视图的示意图;

26.图3a是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路的示意图;

27.图3b是图示根据本公开的一些实施例的示例性开关电路的示意图;

28.图4是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路的示意图;

29.图5是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路的示意图;

30.图6是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路的示意图;

31.图7是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路的示意图;

32.图8是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路的示意图;

33.图9是图示根据本公开的一些实施例的示例性多位移相器的示意图;

34.图10是示出了根据本公开的一些实施例的示例性相控阵系统的框图;

35.图11是图示根据本公开的一些实施例的用于执行相移的示例性方法的流程图。

具体实施方式

36.综述

37.本公开的系统、方法和设备均具有若干创新实施例,其中没有一个单独负责本文公开的所有期望属性。本说明书中描述的主题的一个或多个实现的细节在以下描述和附图中阐述。

38.移相器是一个双端口网络,它接收输入信号并输出输入信号的移相版本。如上所述,移相器可用于各种系统,例如相控阵天线系统和/或波束成形集成电路装置。移相器的性能可以通过其在所有相位状态下的插入损耗(或增益)和/或幅度、其跨频率相位响应的平坦度、互易网络性能、工作带宽、功率处理能力和/或尺寸来表征(例如,硅芯片面积)。一般而言,可能希望移相器具有较低的插入损耗、在较宽的带宽上工作且在较宽的带宽上具有平坦的相移(恒定相位)并且具有较小的管芯尺寸。

39.如上所述,在各种相移的移相器中,180度移相器可能是最具挑战性的设计。180度移相器是一个双端口网络,提供两个相差180度的输出相位状态。实现180度移相器的一种方法是使用开关滤波器拓扑。例如,180度移相器可以在高通和低通滤波器网络(例如,使用电感器和电容器的组合))之间切换,以匹配它们在工作中心频率处的插入损耗。这种方法的一个缺点是低通和高通滤波器网络是围绕中心工作频率设计的,因此工作频率带宽可能会受到限制。

40.使用开关滤波器技术在宽带宽上提供具有平坦相位(例如,恒定相位)的180度移相器,同时保持低插入损耗,这可能具有挑战性。例如,当使用开关滤波器技术时,插入损耗通常会受到影响,以在感兴趣的带宽上提供平坦的相位。例如,为了平衡基于开关滤波器的

180度移相器的相位平坦度,以在ku频段(例如,在12到18ghz范围内)或ka频段(例如,在26.5到40ghz范围),插入损耗可能大于约1.5分贝(db)。在相控阵天线系统中,大的插入损耗可能是不可取的,因为提供相同的输出功率会消耗更多的功率。虽然可以将额外的电路组件(例如,电感器)添加到开关滤波器拓扑中以改善相位平坦度,同时插入损耗较小,但添加的组件会增加管芯尺寸,因此可能并不理想。

41.本公开描述了用于以可以解决上述插入损耗、相位平坦度和管芯尺寸问题的方式提供180度移相器的机制。本公开的一个方面提供了一种使用拓扑结构的180度移相器,该拓扑结构在两个变压器路径之间切换,一个具有正耦合而另一个具有负耦合。例如,移相器电路可以包括第一节点和第二节点之间的两条信号路径,其中第一路径可以包括正耦合变压器并且第二信号路径可以包括负耦合变压器。对于正耦合变压器,初级线圈两端的电压和次级线圈两端的电压同相(提供0度相移)。另一方面,对于负耦合变压器,初级线圈两端的电压和次级线圈两端的电压是异相的(提供180度相移)。换言之,正耦合变压器的初级线圈可具有与正耦合变压器次级线圈的走线结构相同方向的走线结构,而负耦合变压器的初级线圈可以具有与负耦合变压器的次级线圈的走线结构在相反方向上的走线结构。移相器电路还可以包括多个开关(例如,使用场效应晶体管(fet)实现)以选择第一信号路径或第二信号路径。第一信号路径(具有正耦合)和第二信号路径(具有负耦合)在第二节点处可以彼此异相。换言之,移相器电路可以在选择第一信号路径时提供第一输出相位状态并且在选择第二信号路径时提供第二输出相位状态,其中第一输出相位状态与第二输出相位状态具有约180度的相对相位差。

42.为了提供第一信号路径和第二信号路径之间的选择,多个开关中的第一开关可以耦合在第一节点和正耦合变压器之间,多个开关中的第二开关可以耦合在第一节点和负耦合变压器之间,多个开关中的第三开关可以耦合在正耦合变压器和第二节点之间,并且多个开关中的第四开关可以耦合在负耦合变压器和第二节点之间。第一和第三开关可以响应于第一控制信号,而第二和第四开关可以响应于第二控制信号。第一控制信号和第二控制信号可以具有相反的相位,使得在给定时间仅选择第一信号路径或第二信号路径中的一个。

43.本公开还可以为基于变压器的移相器电路提供各种性能改进。例如,在一些方面,移相器电路还可以包括分流fet以在两个信号路径之间提供更好的隔离。附加地或替代地,移相器电路可以将堆叠的fet用于开关以增加功率处理能力。附加地或替代地,移相器电路可以包括各种调谐电容器以平衡正耦合变压器和负耦合变压器之间的寄生电容差异。平衡正耦合变压器和负耦合变压器之间的寄生电容差异可以提高相位精度。

44.在一些方面,基于开关变压器的180度移相器可以集成为多位移相器的一部分、波束成形集成设备的一部分和/或相位天线阵列系统的一部分。

45.此处描述的系统、方案和机制可以提供若干益处。例如,正耦合和负耦合路径自然会导致两条路径之间存在180度的相位差,因此基于开关变压器的移相器电路可以在宽带宽上运行,并在宽带宽上提供基本平坦的相位响应,而无需与开关滤波器拓扑相同的限制。此外,因为没有滤波器响应限制,也不需要像开关滤波器设计那样在相位平坦度和插入损耗之间做出妥协,基于开关变压器的180度移相器的插入损耗可能主要由控制fet的“导通”电阻(例如,当开关打开时)、变压器的磁耦合损耗以及变压器线圈(电感器)的金属电阻造

成。所有这些导致插入损耗的因素可能很小。此外,变压器(正耦合变压器和/或负耦合变压器)的尺寸可以显着小于用于形成开关滤波器拓扑的电感器和电容器。这样,基于开关变压器的移相器电路可以提供低插入损耗,同时在所有输出相位状态(例如,第一路径提供的第一输出相位状态和第二路径提供的第二输出相位状态)和小芯片尺寸的宽带宽内保持平坦的相位响应。此外,因为具有电容器的集成电路中的工艺变化可能很大,而具有变压器(例如,变压器中的线圈或电感器)的集成电路中的工艺变化可能很小,所以基于开关变压器的移相器(利用变压器)可能比基于开关滤波器的移相器(利用电容器)更不容易受到过程变化的影响。

46.所公开的实施例可适用于无线通信系统和/或传感器系统。特别地,本文描述的系统、方案和机制可以有利地改进高频(例如,毫米波)通信和/或传感器系统中的波束形成性能。

47.基于开关滤波器的移相器示例

48.图1是图示示例性基于开关滤波器的移相器电路100的示意图。移相器电路100可以是集成电路器件的一部分。在一些情况下,移相器电路100可以是多位移相器的一部分。在一些情况下,移相器电路100可以是射频(rf)设备的一部分。移相器电路100可以利用开关滤波器拓扑来提供具有大约180度的相位差的两个输出相位状态。

49.如图所示,移相器电路100可以包括输入节点102、输出节点104、布置在输入节点102和输出节点104之间的第一信号路径101以及布置在输入节点102和输出节点104之间的第二信号路径103。第一信号路径101可以包括低通滤波器网络110、耦合在低通滤波器网络110和输入节点102之间的开关114a、以及耦合在低通滤波器网络110和输出节点104之间的另一个开关114b。低通滤波器网络110可以包括以∏形状配置布置在两个电容器116之间的电感器118,其中每个电容器116可以具有耦合到电感器118的一端和耦合到地电位(示为vgnd)的另一端。第一信号路径101中的低通滤波器网络110可以被配置为提供大约180度的相移。可以使用fet来实现开关114。如图所示,fet 114a的漏极端子可以耦合到输入节点102并且fet 114a的源极端子可以耦合到低通滤波器网络110。fet 114b的漏极端子可以耦合到低通滤波器网络110并且fet 114b的源极端子可以耦合到输出节点104。fet 114a和114b的栅极端子均可以耦合到电阻器112并且由(或响应于)第一控制信号106(示为vctrl)控制。例如,开关114可以在相应的栅极端子接收到逻辑高(例如,vctrl是逻辑高)时被接通并且可以在相应的栅极端子接收到逻辑低(例如,vctrl是逻辑低)时被关闭。

50.第二信号路径103可以包括高通滤波器网络120、耦合在高通滤波器网络120和输入节点102之间的开关124a、以及耦合在高通滤波器网络120和输出节点104之间的另一个开关124b。高通滤波器网络120可以包括两个串联电容器126和一个以t形配置布置的电感器128,其中电感器128的一端可以耦合到两个电容器126之间的节点,而另一端耦合到接地电位。第二信号路径103中的高通滤波器网络120可以被配置为提供大约0度的相移。类似地,可以使用fet来实现开关124。如图所示,fet 124a的漏极端子可以耦合到输入节点102并且fet 124a的源极端子可以耦合到高通滤波器网络120。fet 114b的漏极端子可以耦合到高通滤波器网络120并且fet 124b的源极端子可以耦合到输出节点104。fet 124a和124b的栅极端子可以各自耦合到电阻器112并由(或响应于)第二控制信号108(示为vctrl_bar)控制。第二控制信号108可以是第一控制信号106的反相信号,从而可以在任何给定时间选

择第一信号路径101或第二信号路径103中的一个。换言之,移相器电路100可以被配置为在输出节点104处提供经由第一信号路径101的第一输出信号或经由第二信号路径103的第二输出信号,其中第一输出信号和第二输出信号可以具有不同的相位(例如,相差180度)。

51.虽然移相器电路100可以被配置为提供180度的相移,但可能难以在宽带宽上同时提供低插入损耗和相位平坦度。虽然可以向移相器电路100添加附加组件(例如,电感器)以在整个操作带宽上提供更好的相位平坦度,但添加更多组件会增加管芯尺寸。因此,本公开提供使用开关变压器拓扑来实现180度移相器的技术,以克服开关滤波器拓扑的插入损耗和相位平坦度问题。

52.基于开关变压器的移相器示例

53.图2a是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路200的示意图。移相器电路200可以是集成电路器件的一部分。在一些情况下,移相器电路200可以是多位移相器(例如,图9的多位移相器电路900)的一部分。在一些情况下,移相器电路200可以是rf设备(例如,图10的相控阵系统1000)的一部分。移相器电路200可以利用开关变压器拓扑来提供具有大约180度的相位差的两个输出相位状态。

54.如图所示,移相器电路200可以包括输入节点202、输出节点204、布置在输入节点202和输出节点204之间的第一信号路径201以及布置在输入节点202和输出节点204之间的第二信号路径203。第一信号路径201可以包括正耦合变压器212、耦合在正耦合变压器212和输入节点202之间的开关214a(显示为n1),以及耦合在正耦合变压器212和输入节点204之间的另一个开关214b(显示为n2)。正耦合变压器212可以包括初级线圈l1和次级线圈l2,每一个都连接到地电位。初级线圈l1可以以耦合因子k1(例如,理想地为1.0,但可以在大约0.7至大约0.8之间)正耦合到次级线圈l2。正耦合由位于初级线圈l1顶部的点和位于次级线圈l2顶部的点表示。输入信号连接到初级线圈l1的虚线端,输出信号连接到次级线圈l2的虚线端。更具体地,如电流i1和电流i2所示,电流可以从初级线圈l1上的虚线端进入初级线圈l1,并且可以从次级线圈l2上的虚线端离开次级线圈l2。

55.第二信号路径203可包括负耦合变压器222、耦合在负耦合变压器222和输入节点202之间的开关224a(示为n3)、以及耦合在正耦合变压器212和输出节点204之间的另一开关214b(示为n4)。负耦合变压器222可以包括初级线圈l3和次级线圈l4,每个线圈连接到地电位。初级线圈l3可以以耦合因子k2(例如,理想地为1.0,但可以在大约0.7到大约0.8之间)负耦合到次级线圈l4。在一些情况下,正耦合变压器212的耦合因子k1可以与负耦合变压器222的耦合因子k2大致相同。负耦合由位于初级线圈l3顶部的点和位于次级线圈l4底部的点表示。输入信号连接到初级线圈l3的点状端子,而输出信号连接到次级线圈l4的非点状端子。更具体地,如电流i3和电流i4所示,电流可以从初级线圈l3上的虚线端进入初级线圈l3,并且可以从次级线圈l4上的虚线端离开次级线圈l4。虽然图2a图示了正耦合变压器212的初级线圈l1和次级线圈l2的电流方向以及负耦合变压器222的初级线圈l3和次级线圈l4的电流方向,但它可能不直接转换为正耦合变压器212和负耦合变压器222的布局或迹线中的电流方向,如下面将参考图2b更充分地讨论的。

56.基于第一信号路径201上的正耦合变压器212和第二信号路径203上的负耦合变压器222的配置,在输出节点204处,第一信号路径201可以与第二信号路径203异相。因此,移相器电路200可以提供相对相位差约180度的两个输出相位状态(来自第一信号路径201的

第一输出相位状态和来自第二信号路径203的第二输出相位状态)。

57.类似于移相器电路100,开关214和224可以实现为fet。如图所示,fet 214a的漏极端子可以耦合到输入节点202并且fet 214a的源极端子可以耦合到正耦合变压器212。fet 214b的漏极端子可以耦合到正耦合变压器212并且fet 214b的源极端子可以耦合到输出节点204。fet 214a和214b的栅极端子可以由(或响应于)第一控制信号206(示为vctrl)来控制。例如,当相应的栅极端子接收到逻辑高(例如,vctrl是逻辑高)时,开关214可以被接通,并且当相应的栅极端子接收到逻辑低(例如,vctrl是逻辑低)时,可以关闭开关214。以类似的方式,fet 224a的漏极端子可以耦合到输入节点202并且fet 224a的源极端子可以耦合到负耦合变压器222。fet 224b的漏极端子可以耦合到负耦合变压器222并且fet 224b的源极端子可以耦合到输出节点204。fet 224a和224b的栅极端子可由(或响应于)第二控制信号208(示为vctrl_bar)控制。第二控制信号208可以是第一控制信号206的反相信号,从而可以在任何给定时间选择第一信号路径201或第二信号路径203中的一个。换言之,移相器电路200可以被配置为经由第一信号路径201传导输入信号以在输出节点204处提供第一输出信号,或者备选地经由第二信号路径203在输出节点204处提供第二输出信号,其中经由第一信号路径201的第一输出信号与经由第二信号路径203的第二输出信号异相(相移180度)。

58.如上所述,因为第一信号路径201上使用的正耦合(来自正耦合变压器212)和第二信号路径203上使用的负耦合(来自负耦合变压器222)可以在第一信号路径201和第二信号路径203之间提供大约180度的相对相位差,所以没有滤波器响应限制和/或操纵或组件选择来权衡插入损耗与相位平坦度,就像在开关滤波器拓扑中一样。因此,移相器电路200使用的开关变压器拓扑可以在非常宽的带宽(例如无限带宽)上运行,并在宽带宽上(例如,在第一信号路径201和第二信号路径203之间)提供基本平坦的相位。此外,移相器电路200可以提供低插入损耗(例如,在ka和/或ku频带中的高频处,比基于开关滤波器的移相器小约0.5到1分贝(db)),这可能主要由控制fet 214和224的“导通”电阻贡献(例如,当开关打开时),变压器212或222的磁耦合损耗,以及变压器212或222处的线圈(电感器)的金属电阻。此外,因为移相器电路200可以提供相对平坦的相位,例如在带宽约为3ghz的ka频段或带宽约为2ghz的ku频段中相位误差或相位变化小于约0.5度,则不需要在移相器电路200中添加额外的电感器来提高相位平坦度,就像在开关滤波器拓扑中一样。因此,与开关滤波器拓扑结构相比,移相器电路200可以提供紧凑的管芯尺寸。此外,与开关滤波器拓扑中使用的电容器相比,正耦合变压器212和负耦合变压器222对过程变化的敏感度较低。

59.图2b是图示根据本公开的一些实施例的基于变压器的移相器电路200的更详细视图的示意图。具体地,图2b示出了正耦合变压器212和负耦合变压器222的内部布线结构。如图所示,正耦合变压器212的初级线圈l1和次级线圈l2缠绕在一起,例如围绕磁芯(未显示)。正耦合是通过将初级线圈l1的走线结构配置为与次级线圈l2的走线结构同向,例如将初级线圈l1的端子230和次级线圈l2的端子232连接到信号并将初级线圈l1的另一个端子231和次级线圈l2的另一个端子233连接到地电位。例如,端子230和端子232可以分别对应于图2a所示的初级线圈l1上的点状端子和次级线圈l2上的点状端子。因此,初级电流(例如,图2a中所示的i1)可以进入端子230,而次级电流(例如,图2a中所示的i2)可以离开端子232。即,在正耦合变压器212的布线结构中,初级电流可沿逆时针方向流动,而次级电流可

沿顺时针方向流动。

60.如图2b进一步所示,负耦合变压器222的初级线圈l3和次级线圈l4缠绕在一起,例如围绕磁芯(未示出)。负耦合是通过将初级线圈l3的走线结构配置为与次级线圈l4的走线结构方向相反,例如通过将初级线圈l3的端子234连接到信号并将初级线圈l4的另一个端子235连接到地电位,同时将次级线圈l4的端子236连接到地电位,将次级线圈l4的另一个端子237连接到信号。例如,端子234和端子236可以分别对应于图2a所示的初级线圈l3上的点状端子和次级线圈l4上的点状端子。因此,初级电流(例如,图2a中所示的i3)可以进入端子234,而次级电流(例如,图2a中所示的i4)可以离开端子236。即,初级电流可以逆时针流动,并且次级电流可以在负耦合变压器222的布线结构中以顺时针方向行进。

61.虽然图2b将正耦合变压器212和负耦合变压器222图示为大约相同的尺寸,但各方面不限于此。例如,正耦合变压器212(例如,初级线圈l1和次级线圈l2)可以具有比负耦合变压器222(例如,初级线圈l3和次级线圈l4)更大的尺寸以提供更好的相位精度。

62.基于开关变压器的移相器的各种示例性改进

63.图3a是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路300的示意图。移相器电路300可以是集成电路器件的一部分。在一些情况下,移相器电路300可以是多位移相器(例如,图9的多位移相器电路900)的一部分。在一些情况下,移相器电路300可以是rf设备(例如,图10的相控阵系统1000)的一部分。移相器电路300可以利用开关变压器拓扑来提供具有大约180度的相位差的两个输出相位状态。图3a的移相器电路300与图2的移相器电路200共享许多元件;为简洁起见,不再重复对这些元件的讨论,并且这些元件可以采用本文公开的任何实施例的形式。移相器电路300可以与移相器电路200基本相同地操作,但是可以在两个信号路径201和203之间提供更好的隔离。

64.如图3a所示,移相器电路300还可包括分流fet 314a、314b、324a和324b,分别示为n5、n6、n7和n8。分流fet 314a被布置在耦合到第一信号路径201的分流路径上,例如,在fet 214a和正耦合变压器212之间的节点处。分流fet 314b被布置在耦合到第一信号路径201的分流路径上,例如,在正耦合变压器212和fet 214b之间的节点处。以类似的方式,分流fet 324a被布置在耦合到第二信号路径203的分流路径上,例如,在fet 224a和负耦合变压器222之间的节点处,并且分流fet 324b布置在耦合到第二信号路径203的分流路径上,例如,在负耦合变压器222和fet 224b之间的节点处耦合到第二信号路径203的路径。

65.添加分流fet 314和324可以增加两个信号路径201和203之间的隔离。为此,分流fet 314a和314b的栅极端子可以由(或响应于)控制信号(例如,vctrl_bar)控制,其从控制选择第一信号路径201的主开关(例如fet 214a和214b)的第一控制信号206(例如,vctrl)反相。类似地,分流fet 324a和324b的栅极端子可以由(或响应于)控制信号(例如,vctrl)控制,该控制信号从控制选择第二信号路径203的主开关(例如fet 224a和224b)的第二控制信号208(例如,vctrol_bar)反相。也就是说,当fet 214a和214b导通以启用第一信号路径201时,分流fet 314a和314b(耦合到第一信号路径201)被关闭,并且分流fet 324a和324b(耦合到第二信号路径203)被打开以防止信号经由第二信号路径203从输入节点102泄漏到输出节点104。相反地,当fet 224a和224b导通以启用第二信号路径203时,分流fet 324a和324b(耦合到第二信号路径203)被关断,并且分流fet 314a和314b(耦合到第一信号路径201)被导通以防止信号从输入节点102经由第一信号路径201泄漏到输出节点104。

66.图3b是图示根据本公开的一些实施例的示例性开关电路330的示意图。在一些方面,移相器电路200和/或移相器电路300可以实现开关电路330所示的开关(例如,开关214、224、314、324)。如图所示,开关电路330包括堆叠fet 334a和334b。更具体地,fet 334a和334b串联连接,其中fet 334a的源极端子可以连接到fet 334b的漏极端子。堆叠的fet334a和334b的栅极端子可由相同的控制信号336(示为vctrl_s)控制。例如,移相器电路300中的开关214a可以由堆叠的fet 334a和334b代替。一般而言,移相器电路300中的其他开关214b、224a、224b、314a、314b、324a和324b中的一个或多个可以分别由堆叠的fet 334a和334b代替。在一些情况下,移相器电路300中的所有开关214b、224a、224b、314a、314b、324a和324b可以由堆叠的fet 334a和334b代替。使用堆叠fet代替单个fet进行开关可以提高移相器电路200和/或300的功率处理能力。

67.虽然图3b图示了串联连接的两个fet,但是方面不限于此。例如,移相器电路300中的开关214b、224a、224b、314a、314b、324a和324b中的任何一个或多个可以由多于两个堆叠的fet(例如,3、4个或更多个串联的fet)放置。

68.有多种因素可以导致正耦合变压器212和负耦合变压器222具有不同的信号特性,例如,在插入损耗和/或相位变化方面。一般而言,由于正耦合变压器212与负耦合变压器222的电压及电荷分布情况可能不同,因此输出节点204处的两个信号路径201和203(或两个输出状态)之间的插入损耗可以不同。此外,在输出节点204处的两个信号路径201和203(或两个输出状态)之间的频率上可能存在额外的相位变化。图4-8说明了各种机制(例如,添加调谐电容器)以提高图2a-2b的移相器电路200和/或图3的移相器电路300。

69.图4是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路400的示意图。移相器电路400可以是集成电路器件的一部分。在一些情况下,移相器电路400可以是多位移相器(例如,图9的多位移相器电路900)的一部分。在一些情况下,移相器电路400可以是rf设备(例如,图10的相控阵系统1000)的一部分。图4的移相器电路400与图2的移相器电路200共享许多元件;为简洁起见,不再重复对这些元件的讨论,并且这些元件可以采用本文公开的任何实施例的形式。移相器电路400可以以与移相器电路200基本相同的方式操作,但是可以提供改进的相位精度。

70.理想地,如果正耦合变压器212的初级线圈l1和次级线圈l2之间的耦合(例如,因子k1)与负耦合变压器222的初级线圈l3和次级线圈l4之间的耦合(例如,因子k2)是相同的,移相器电路200和/或300可以在非常大的带宽上提供180度的相移。然而,实际上,即使线圈l1、l2、l3和l4的尺寸相同(具有相同的电感),正耦合变压器212和负耦合变压器222的寄生分量也可能不同。可能对相位精度影响最大的寄生分量是正耦合变压器212和负耦合变压器222之间的寄生电容差。例如,正耦合变压器212的初级线圈l1和次级线圈l2之间的寄生电容可以小于负耦合变压器222处初级线圈l3和次级线圈l4之间的寄生电容。正耦合变压器212是由于流经初级线圈l1和次级线圈l2的电流方向相同,使得初级线圈l1和次级线圈l2处的电子电荷相互推动(例如,彼此离得更远)。另一方面,电流以相反方向流经负耦合变压器222的初级线圈l3与次级线圈l4,使初级线圈l3与次级线圈l4处的电子电荷相互靠近,从而产生较大的寄生电容。

71.如此,移相器电路400可进一步包括跨正耦合变压器212的初级线圈l1的端子和次级线圈l2的端子耦合的电容器412(示为c1)以补偿正耦合变压器212处较小的寄生电容。

72.图5是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路500的示意图。移相器电路200可以是集成电路器件的一部分。在一些情况下,移相器电路200可以是多位移相器(例如,图9的多位移相器电路900)的一部分。在一些情况下,移相器电路200可以是rf设备(例如,图10的相控阵系统1000)的一部分。图5的移相器电路500与图3a的移相器电路300共享许多元件;为简洁起见,不再重复对这些元件的讨论,并且这些元件可以采用本文公开的任何实施例的形式。移相器电路500可以以与移相器电路300基本相同的方式操作,但是可以提供改进的相位精度。

73.与移相器电路400类似,在移相器电路500中,正耦合变压器212可具有比负耦合变压器222更小的寄生电容。因此,移相器电路500可进一步包括电容器512(示为c1)耦合在正耦合变压器212的初级线圈l1的端子和次级线圈l2的端子之间以补偿正耦合变压器212处的较小寄生电容。

74.虽然图4和图5示出了可以跨正耦合变压器212的初级线圈l1和次级线圈l2添加附加电容器c1,但是在一些方面,还可以在负耦合变压器222的初级线圈l3和次级线圈l4两端添加电容器。一般而言,可以在正耦合变压器212的初级线圈l1和次级线圈l2两端添加电容器和/或还可以跨负耦合变压器222的初级线圈l3和次级线圈l4添加电容器,目的是在正耦合变压器212和负耦合变压器222处具有大约相同的电容。

75.图6是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路600的示意图。移相器电路200可以是集成电路器件的一部分。在一些情况下,移相器电路200可以是多位移相器(例如,图9的多位移相器电路900)的一部分。在一些情况下,移相器电路200可以是rf设备(例如,图10的相控阵系统1000)的一部分。图6的移相器电路600与图4的移相器电路400共享许多元件;为简洁起见,不再重复对这些元件的讨论,并且这些元件可以采用本文公开的任何实施例的形式。移相器电路600可以以与移相器电路400基本相同的方式操作,但是可以提供进一步的相位精度改进。

76.例如,为了进一步平衡正耦合变压器212和负耦合变压器222之间的电容,移相器电路600还可以包括与初级线圈l1并联的电容器612(示为c2)和与次级线圈l2并联的电容器614(示为c3)。

77.图7是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路700的示意图。移相器电路200可以是集成电路器件的一部分。在一些情况下,移相器电路200可以是多位移相器(例如,图9的多位移相器电路900)的一部分。在一些情况下,移相器电路200可以是rf设备(例如,图10的相控阵系统1000)的一部分。图7的移相器电路700与图6的移相器电路500共享许多元件;为简洁起见,不再重复对这些元件的讨论,并且这些元件可以采用本文公开的任何实施例的形式。移相器电路700可以与移相器电路500基本相同地操作,但是可以提供进一步的相位精度改进。

78.如图所示,类似于移相器电路600,移相器电路700还可以包括与初级线圈l1并联的电容器712(示为c2)和与次级线圈l2并联的电容器714(示为c3)。

79.图8是图示根据本公开的一些实施例的示例性基于开关变压器的移相器电路800的示意图。移相器电路200可以是集成电路器件的一部分。在一些情况下,移相器电路200可以是多位移相器(例如,图9的多位移相器电路900)的一部分。在一些情况下,移相器电路200可以是rf设备(例如,图10的相控阵系统1000)的一部分。图8的移相器电路800与图7的

移相器电路700共享许多元件;为简洁起见,不再重复对这些元件的讨论,并且这些元件可以采用本文公开的任何实施例的形式。移相器电路800可以以与移相器电路700基本相同的方式操作。

80.如图所示,移相器电路800还可以包括与负耦合变压器222的初级线圈l3并联的电容器822(示为c5)和与负耦合变压器222的次级线圈l4并联的电容器824、电容器824(示为c6)。然而,移相器电路800可以不包括如移相器电路700中那样跨越正耦合变压器212的初级线圈l1和第二线圈l2的电容器712c1。

81.通常,移相器电路(例如,移相器电路200、300、400、500、600、700和/或800)可以包括以各种配置布置的一个或多个电容器以平衡正耦合变压器212和负耦合变压器222之间的寄生电容差,使得移相器电路可以提供更好的移相精度。例如,第一电容可以跨过正耦合变压器212的初级线圈l1和次级线圈l2,第二电容可以与正耦合变压器212的初级线圈l1并联,第三电容器可与正耦合变压器212的次级线圈l2并联布置,可以在负耦合变压器222的初级线圈l3和次级线圈l4两端设置第四电容器,可以与负耦合变压器222的初级线圈l3并联设置第五电容器,和/或第六电容器可以与负耦合变压器222的次级线圈l4并联布置。

82.虽然移相器电路200、300、400、500、600、700和800中的开关214、224、314和/或324被示为负-正-负(npn)晶体管,但开关214、224、314和/或324可以使用任何合适的晶体管来实现,例如正负正(pnp)晶体管、金属氧化物半导体(mos)器件和/或互补金属氧化物半导体(cmos)设备。

83.多位移相器示例

84.图9是图示根据本公开的一些实施例的示例性多位移相器电路900的示意图。多位移相器电路900可以是集成电路装置的一部分。在一些情况下,多位移相器电路900可以是rf设备(例如,图10的相控阵系统1000)的一部分。

85.如图所示,多位移相器电路900可以包括输入节点902、输出节点904和多个可调节或可切换的移相器电路910、920、930、940、950和960,它们串联连接在输入节点902和输出节点904之间。移相器电路910、920、930、940、950和960中的每一个可以响应于相应的控制信号或控制位而提供不同的相移。例如,移相器电路910可以被配置为基于分别为逻辑高或逻辑低的控制信号915(示为vctrl5)或反之亦然提供0

°

或90

°

的相移。移相器电路920可以被配置为基于分别为逻辑高或逻辑低的控制信号911(显示为vctrl1)或反之亦然提供0

°

或5.6

°

的相移。移相器电路930可被配置为基于分别为逻辑高或逻辑低的控制信号916(示为vctrl6)或反之亦然提供0

°

或180

°

的相移。移相器电路940可被配置为基于分别为逻辑高或逻辑低的控制信号913(示为vctrl3)或反之亦然提供0

°

或22

°

的相移。移相器电路950可被配置为基于分别为逻辑高或逻辑低的控制信号912(示为vctrl2)或反之亦然提供0

°

或11

°

的相移。移相器电路960可被配置为基于分别为逻辑高或逻辑低的控制信号914(示为vctrl4)或反之亦然提供0

°

或45

°

的相移。在一些方面,180

°

移相器电路930可以使用上面参考图2a-2b、3a-3b和4-8讨论的任何一种开关变压器拓扑来实现。

86.在一些方面,控制信号911、912、913、914、915和916中的每一个可以根据控制字的单独控制位(例如,具有位b0、b1、b2、b3、b4和b5)用于配置多位移相器电路900。作为示例,控制信号911、912、913、914、915和916可以分别由b0、b1、b2、b3、b4和b5控制。控制信号911、912、913、914、915和/或916可在对应位为1时被设置为逻辑高,而当对应位为0时可被设置

为逻辑低,反之亦然。在一些方面,移相器电路910、920、930、940、950和960可以基于各个电路块的插入损耗和/或回波损耗按顺序排列。然而,通常,移相器电路910、920、930、940、950和960可以按任何合适的顺序排列,并且相应的控制信号915、911、916、913、912和914可以映射到任何合适的控制字的位。

87.在操作中,移相器电路900可以在输入节点902处接收输入信号。输入信号可以被移相器电路910、920、930、940、950和960中的一个或多个移相,取决于控制信号915、911、916、913、912和914中的每一个分别是逻辑高还是逻辑低。移相器电路900可以在输出节点904处输出输出信号,其中输出信号可以对应于输入信号的移相版本。

88.虽然图9将多位移相器电路900图示为包括由6位控制字控制的六个移相器电路910、920、930、940、950和960的6位移相器,但各方面不限于此。一般而言,基于切换变换的移相拓扑可用于实现多位移相器,该移相器包括较少数量的移相器电路(例如,1、2、3、4、5)或更多数量的移相器电路(例如,7、8或更多)。

89.相控阵系统示例

90.图10是图示根据本公开的一些实施例的示例性相控阵系统1000的框图。相控阵系统1000可以是rf系统的一部分。在一些情况下,移相器电路可以对应于无线通信设备的一部分。在其他情况下,相控阵系统1000可以对应于基站的一部分。相控阵系统1000可以在任何合适的频率范围内操作。在一些方面,相控阵系统1000可以在ku波段和/或ka波段上操作。

91.如图所示,系统1000可以包括发射机1040、接收机1050、模拟前端(afe)1060和天线阵列1024。发射机1040可以包括多输入多输出(mimo)编码器1002和数模转换器(dac)1004。接收器1050可以包括mimo解码器1032和模数转换器(adc)1034。afe 1060可以包括开关1010(示为sw)、乘法器1012、锁相环(pll)1006、另一个开关1008(示为sw)、多个数字步进衰减器(dsa)1014(示为1014a和1014b)、多个移相器1016(显示为1016a和1016b)、多个功率放大器(pa)1018、多个低噪声放大器(lna)1020和多个开关1022(显示为sw)。可以使用硬件和/或软件的组合来实现mimo编码器1002和mimo解码器1032。系统1000中的其余组件可以在硬件中实现并且至少一些组件可以由软件控制。

92.在发射方向上,mimo编码器1002可以生成多个数据流(例如,大约2、4、8、16或更多)。dac1004可以耦合到mimo编码器并且可以将数据流转换成用于传输的模拟信号。开关1010可以在发射器1040和接收器1050之间切换。乘法器1012可以将发射模拟信号与由pll 1006产生的pll信号相乘(或混合)。开关1008可以被选择将乘法器1012的输出信号耦合到dsa 1014a。dsa 1014a可以被编程为各种衰减步骤以衰减相应的信号。移相器1016a每个都可以耦合到dsa 1014a之一并且被控制以将相应信号的相位移动某个相移(例如,45

°

、90

°

、180

°

等)。在一些方面,每个移相器1016a可以是类似于以上参考图9讨论的多移相器电路900的多位移相器。在一些方面,每个移相器1016a可以提供各种相移,包括使用上面参考图2a-2b、3a-3b和/或4-8讨论的基于开关变压器的拓扑来实现的180

°

相移。pa1018可各自耦合到移相器1016a之一以放大对应的移相信号以供传输。在一些方面,dsa 1014a、移相器1016a和pa1018可以一起配置以在特定空间方向上形成波束以用于传输。可以选择开关1022来将相移信号耦合到天线阵列1024以进行传输。天线阵列1024可以包括多个天线元件1025(例如,如图所示布置成多行和多列)。天线阵列1024可以包括任何合适数量的天线元

件(例如,4、8、16、64、128、1024或更多)。每个天线元件1025可以被配置为发射具有不同相移的信号(例如,来自移相器1016a)以在特定空间方向上实现波束成形。例如,天线阵列1024可以发射在波束1026中的任何一个中承载的信号。

93.在接收方向上,天线阵列1024可以经由天线元件1025接收信号。可以选择开关1022以将各种天线元件1025耦合到lna 1020。lna 1020可以放大接收到的信号。移相器1016b可以基本上类似于移相器1016a并且可以将各种相移(例如,45

°

、90

°

、180

°

等)应用于接收信号。类似地,dsa 1014b可以基本上类似于dsa 1014a并且可以各自耦合到移相器1016b之一以提供信号衰减。在一些方面,dsa 1014b、移相器1016b和lna 1020可以一起配置为在特定空间方向上形成波束以用于接收,例如,使用波束1026中的任何一个接收信号。可以选择开关1008将接收到的信号耦合到乘法器1012以与由pll 1006生成的pll信号混合。可以选择sw1010将接收到的信号耦合到接收器1050。在接收器1050处,adc 1034可以转换从模拟域到数字域的接收信号。mimo解码器1032可以耦合到adc 1034并且可以从接收的数字信号(例如,大约2、4、8、16或更多)解码信息。

94.在一些方面,dsa 1014a和1014b、移相器1016a和1016b、pa1018和lna 1020可以集成到单个集成电路设备上,例如,用于发射波束成形和/或接收波束成形。

95.尽管图10图示了系统1000中的四个发射路径(例如,每个都包括一个dsa 1014a、一个移相器1016a和一个pa1018)和四个接收路径(例如,每个都包括dsa 1014b、移相器1016b和lna 1020),相控阵系统可以包括任何合适数量的路径。在一些示例中,相控阵系统可以包括2、8、16或更多条用于传输的路径和2、8、16条或更多条用于接收的路径。由于每条发射路径或每条接收路径可以包括移相器,所以这里公开的基于开关变压器的移相器电路可以有利地减小相控阵系统或波束成形集成设备的尺寸。

96.示例移相方法

97.图11是图示根据本公开的一些实施例的用于执行相移的示例性方法1100的流程图。方法1100可以分别由类似于上面参考图2a-2b、3a、4、5、6、7和8讨论的移相器电路200、300、400、500、600、700和800的移相电路、类似于上面参考图9讨论的多位移相器电路900的多移相器电路,和/或类似于上面参考图10讨论的相控阵系统1000的相控阵系统,和/或任何合适的无线设备来实现。尽管可以参考本文公开的移相器电路的特定实施例来说明方法1100的操作,但是可以使用任何合适的硬件组件和/或软件组件来执行方法1100。操作在图11中以特定顺序示出一次,但是操作可以根据需要并行、重新排序和/或重复执行。

98.在1102,在第一时间间隔期间在第一节点处接收第一信号。

99.在1104,响应于第一控制信号,经由第一节点和第二节点之间的第一信号路径传输第一信号,并且包括正耦合变压器以生成第二信号。在一些方面,第一信号路径可以对应于第一信号路径201并且正耦合变压器可以对应于上面参考图2a、2b、3a和4-8讨论的正耦合变压器212。在一些方面,正耦合变压器的初级线圈(例如,l1)在第一方向上具有布线结构,正耦合变压器的次级线圈(例如,l3)在相同的第一方向上具有布线结构,例如,如图2b所示。

100.在1106,在第二时间间隔期间在第一节点处接收第三信号。第二时间间隔可以是与第一时间间隔不同的时间间隔。在一些方面,第一时间间隔和第二时间间隔可以对应于不同的无线电帧、不同的子帧或不同的时隙(例如,在lte或5g的上下文中)。例如,第一信号

可以在第一时间间隔内携带第一数据信息(例如,第一编码数据位),而第二信号可以在第二时间间隔内携带第二数据信息(例如,第二编码数据位)。在一些情况下,第一数据信息可以不同于第二数据信息。在其他一些情况下,第一数据信息可以与第二数据信息相同,其中第二信号是第一数据信息的重传。

101.在1108,响应于第二控制信号,经由第一节点和第二节点之间的第二信号路径传输第二信号,并包括负耦合变压器以生成具有第三信号的第四信号。在一些方面,第二信号路径可以对应于第二信号路径203并且负耦合变压器可以对应于上面参考图2a、2b、3a和4-8讨论的负耦合变压器222。在一些方面,负耦合变压器的初级线圈(例如,l3)在第二方向上具有布线结构,而负耦合变压器的次级线圈(例如,l4)在与第一方向相反的第三方向上具有布线结构。

102.在一些方面,方法1100还可以包括闭合耦合在第一节点和正耦合变压器之间的第一开关并且在1104打开耦合在第一节点和负耦合变压器之间的第二开关以响应于第一控制信号选择用于传输第一信号的第一信号路径。在一些方面,第一开关可以对应于开关214a或开关214b,而第二开关可以对应于开关224a或开关224b。在一些方面,第一和第二开关可以是fet。在一些方面,方法1100可以进一步包括打开耦合在第一信号路径和地电位之间的第三开关(例如,分流fet 314a或314b)并且闭合耦合在第二信号路径和地电位之间的第四开关(例如,分流fet 324a或324b)。

103.在一些方面,方法1100还可以包括打开耦合在第一节点和正耦合变压器之间的第一开关并且在1108关闭耦合在第一节点和负耦合变压器之间的第二开关以响应于第二控制信号来选择用于传输第二信号的第二信号路径。在一些方面,第一开关可以对应于开关214a或开关214b,并且第二开关可以对应于开关224a或开关224b。在一些方面,第一和第二开关可以是fet。在一些方面,方法1100可以进一步包括关闭耦合在第一信号路径和地电位之间的第三开关(例如,分流fet 314a或314b)并且打开耦合在第二信号路径和地电位之间的第四开关(例如,分流fet 324a或324b)。

104.在一些方面,第一控制信号和第二控制信号是反相信号。例如,第一控制信号可以对应于控制信号206(例如,vctrl),而第二控制信号可以对应于控制信号208(例如,vctrl_bar)。

105.例子

106.例子1包括移相器电路,包括:第一节点;第二节点;耦合在所述第一节点和所述第二节点之间的第一信号路径,所述第一信号路径包括正耦合变压器;在所述第一节点和所述第二节点之间的第二信号路径,所述第二信号路径包括负耦合变压器;和多个开关,用于选择所述第一信号路径或所述第二信号路径。

107.例子2包括例子1的移相器电路,其中:所述正耦合变压器的初级线圈两端的电压和所述正耦合变压器的次级线圈两端的电压同相;和所述负耦合变压器的初级线圈两端的电压和所述负耦合变压器的次级线圈两端的电压不同相。

108.例子3包括例子1-2中任一个的移相器电路,其中所述多个开关的第一开关耦合在所述第一节点和所述正耦合变压器之间,并响应于第一控制信号;和所述多个开关的第二开关耦合在所述第一节点和所述负耦合变压器之间,并响应于第二控制信号。

109.例子4包括例子1-3中任一个的移相器电路,其中多个开关的第三开关耦合在正耦

合变压器和第二节点之间,并响应于第一控制信号;多个开关的第四开关耦合在负耦合变压器和第二节点之间,并响应于第二控制信号。

110.例子5包括例子1-4中任一个的移相器电路,其中与所述第一信号路径相关联的第一控制信号和与所述第二信号路径相关联的第二控制信号具有相反的相位。

111.例子6包括例子1-5中任一个的移相器电路,还包括耦合到所述第一信号路径的分流路径,其中所述多个开关的第三开关设置在所述分流路径上,并响应于所述第二控制信号。

112.例子7包括例子1-5中任一个的移相器电路,还包括耦合到所述第二信号路径的分流路径,其中,所述多个开关的第三开关设置在所述分流路径上,并响应于所述第一控制信号。

113.例子8包括例子1-7中任一个的移相器电路,其中第一开关或第二开关中的至少一个包括场效应晶体管(fet)。

114.例子9包括例子1-7中任一个的移相器电路,其中第一开关或第二开关中的至少一个包括叠层场效应晶体管(fet)。

115.例子10包括例子1-9中任一个的移相器电路,其中所述正耦合变压器和所述负耦合变压器具有不同的尺寸。

116.例子11包括例子1-10中任一个的移相器电路,其中正耦合变压器的尺寸大于负耦合变压器。

117.例子12包括例子1-11中任一个的移相器电路,还包括耦合在所述正耦合变压器的初级线圈和次级线圈两端的电容器。

118.例子13包括例子1-12中任一个的移相器电路,还包括耦合在负耦合变压器的初级线圈和次级线圈之间的电容器。

119.例子14包括例子1-13中任一个的移相器电路,还包括与所述正耦合变压器的初级线圈或次级线圈并联的电容器。

120.例子15包括例子1-14中任一个的移相器电路,还包括与所述负耦合变压器的初级线圈或次级线圈并联的电容器.

121.例子16包括例子1-15中任一个的移相器电路,其中所述移相器电路是180度移相器电路。

122.例子17包括例子1-16中任一个的移相器电路,其中所述移相器电路是多位移相器电路。

123.例子18包括装置,包括:第一移相器,包括:第一节点,用于接收输入信号;第二节点;耦合在所述第一节点和所述第二节点之间的第一信号路径,所述第一信号路径包括正耦合变压器;耦合在所述第一节点和所述第二节点之间的第二信号路径,所述第二信号路径包括负耦合变压器,其中所述第二信号路径与所述第二节点处的所述第一信号路径不同相;和多个开关,用于选择所述第一信号路径或所述第二信号路径。

124.例子19包括例子18的装置,其中所述第一移相器还包括以下至少一个:耦合在所述正耦合变压器的初级线圈两端的第一电容器;耦合在所述正耦合变压器的次级线圈两端的第二电容器;耦合在所述负耦合变压器的初级线圈两端的第三电容器;或耦合在所述负耦合变压器的次级线圈两端的第四电容器。

125.例子20包括例子18-19中任一个的装置,还包括与所述第一移相器串联的第二移相器。

126.例子21包括例子18-20中任一个的装置,其中所述第一移相器响应于第一控制位;和所述第二移相器响应于与所述第一控制位分离的第二控制位。

127.例子22包括例子18-21中任一个的装置,其中该装置为相控阵系统;和该装置还包括:天线阵列;和耦合到所述天线阵列的多个移相器,所述多个移相器包括所述第一移相器。

128.例子23包括一种用于执行相移的方法,该方法包括:在第一时间间隔期间在第一节点处接收第一信号;响应于第一控制信号,经由所述第一节点和第二节点之间的第一信号路径发送第一信号,并且包括正耦合变压器以产生第二信号;在第二时间间隔期间在所述第一节点处接收第三信号;和响应于第二控制信号,经由所述第一节点和所述第二节点之间的第二信号路径发送第三信号,并且包括负耦合变压器以生成第四信号。

129.例子24包括例子23的方法,其中所述正耦合变压器的初级线圈在第一方向上具有布线结构;所述正耦合变压器的次级线圈在所述第一方向上具有布线结构;所述负耦合变压器的初级线圈在所述第二方向上具有布线结构;和所述负耦合变压器的次级线圈在与所述第一方向相反的第三方向上具有布线结构。

130.例子25包括例子23-24中任一个的方法,还包括闭合耦合在第一节点和正耦合变压器之间的第一开关,以及打开耦合在第一节点和负耦合变压器之间的第二开关,以选择用于响应于第一控制信号发送第一信号的第一信号路径。

131.例子26包括例子23-25中任一个的方法,还包括打开耦合在第一节点和正耦合变压器之间的第一开关,关闭耦合在第一节点和负耦合变压器之间的第二开关,以选择用于响应于第二控制信号发送第三信号的第二信号路径。

132.例子27包括例子23-26中任一个的方法,其中所述第一控制信号和所述第二控制信号是反向信号。

133.例子28包括装置,包括用于执行根据例子23-27中任一个的方法的构件。

134.例子29包括一种用于执行相移的方法,该方法包括:在第一时间间隔期间在第一节点处接收第一信号;响应于第一控制信号,经由所述第一节点和第二节点之间的第一信号路径发送第一信号,并且包括正耦合变压器以产生第二信号;在第二时间间隔期间在所述第一节点处接收第三信号;和响应于第二控制信号,经由所述第一节点和所述第二节点之间的第二信号路径发送第三信号,并且包括负耦合变压器以生成第四信号。

135.例子30包括例子29所述的方法,其中:所述正耦合变压器的初级线圈在第一方向上具有布线结构;所述正耦合变压器的次级线圈在所述第一方向上具有布线结构;所述负耦合变压器的初级线圈在所述第二方向上具有布线结构;和所述负耦合变压器的次级线圈在与所述第一方向相反的第三方向上具有布线结构。

136.例子31包括例子29所述的方法,还包括:关闭耦合在所述第一节点和所述正耦合变压器之间的第一开关,并打开耦合在所述第一节点和所述负耦合变压器之间的第二开关,以选择用于响应于所述第一控制信号发送所述第一信号的第一信号路径。

137.例子32包括例子29所述的方法,其中所述第一控制信号和所述第二控制信号是反向信号。

138.变化和实现

139.虽然以上参照图1、2a-2b、3a-3b、4-10中所示的示例性实施方式描述了本公开的实施例,但是本领域技术人员将认识到,上述各种教导适用于各种其他实现。

140.在某些情况下,此处讨论的功能可适用于汽车系统、安全关键型工业应用、医疗系统、科学仪器、无线和有线通信、无线电、雷达、工业过程控制、音频和视频设备、电流传感、仪器仪表(它可以是高度精确的)和其他基于数字处理的系统。

141.在上述实施例的讨论中,可以容易地更换、替换或以其他方式修改系统的组件,例如开关、fet、正耦合变压器、负耦合变压器222、adc、dac、dsa、移相器、pa、lna和/或其他组件,以适应特定的电路需要。此外,应当注意,互补电子设备、硬件、软件等的使用为在各种通信系统中实现与180度移相器相关的本公开的教导提供了同样可行的选择。

142.用于实现本文提出的180度移相器的各种系统的部分可包括电子电路以执行本文所述的功能。在一些情况下,系统的一个或多个部分可以由专门配置用于执行这里描述的功能的处理器来提供。例如,处理器可以包括一个或多个专用组件,或者可以包括被配置为执行这里描述的功能的可编程逻辑门。该电路可以在模拟域、数字域或混合信号域中运行。在一些情况下,处理器可以被配置为通过执行存储在非暂时性计算机可读存储介质上的一个或多个指令来执行这里描述的功能。

143.在一个示例实施例中,可以在相关联的电子设备的板上实现本图中的任意数量的电路。该板可以是通用电路板,可以容纳电子设备内部电子系统的各种部件,并且进一步为其他外围设备提供连接器。更具体地,板可以提供电连接,系统的其他部件可以通过该电连接进行电通信。任何合适的处理器(包括dsp、微处理器、支持芯片组等)、计算机可读的非暂时性存储元件等都可以根据特定的配置需求、处理需求、计算机设计等适当地耦合到板。其他组件,例如外部存储器、附加传感器、音频/视频显示控制器和外围设备,可以作为插件卡、通过电缆连接到板上,或集成到板本身中。在各种实施例中,本文描述的功能可以以仿真形式实现为在一个或多个可配置(例如,可编程)元件内运行的软件或固件,这些元件以支持这些功能的结构布置。提供仿真的软件或固件可以在非暂时性计算机可读存储介质上提供,该存储介质包括允许处理器执行那些功能的指令。

144.在另一示例实施例中,本图中的电路可以被实现为独立模块(例如,具有配置为执行特定应用程序或功能的相关组件和电路的设备)或被实现为插入到电子设备的专用硬件中的模块。注意,本公开的特定实施例可以容易地部分地或全部地包括在片上系统(soc)封装中。soc代表将计算机或其他电子系统的组件集成到单个芯片中的ic。它可能包含数字、模拟、混合信号以及通常的rf功能:所有这些功能都可以在单个芯片基板上提供。其他实施例可以包括多芯片模块(mcm),其中多个单独的ic位于单个电子封装内并且被配置为通过电子封装彼此紧密交互。

145.还必须注意,此处概述的所有规格、尺寸和关系(例如,图2a-2b、3a、4-9中所示的移相器电路和/或图10中所示的相控阵系统的组件数量)仅用于示例和教学目的。在不脱离本公开的精神或所附权利要求的范围的情况下,此类信息可以有相当大的变化。应当理解,可以以任何合适的方式合并系统。沿着类似的设计备选方案,本图中所示的电路、组件、模块和元件中的任何一个可以以各种可能的配置进行组合,所有这些显然都在本说明书的广泛范围内。在前面的描述中,已经参考特定的处理器和/或组件布置描述了示例实施例。在

不脱离所附权利要求的范围的情况下,可以对这些实施例进行各种修改和改变。因此,描述和附图被认为是说明性的而不是限制性的。

146.注意,通过这里提供的众多示例,可以根据两个、三个、四个或更多个电气组件来描述交互。然而,这样做只是为了清楚和举例。应当理解,可以以任何合适的方式合并系统。沿着类似的设计备选方案,图中所示的任何部件、模块和元件可以以各种可能的配置组合,所有这些显然都在本说明书的广泛范围内。在某些情况下,通过仅参考有限数量的电气元件来描述给定的一组流程的一个或多个功能可能更容易。应当理解,附图及其教导的电路易于扩展并且可以容纳大量部件以及更复杂/精密的布置和配置。因此,所提供的示例不应限制范围或抑制可能应用于无数其他架构的电路的广泛教导。

147.注意,在本说明书中,对包括在“一个实施例”、“示例实施例”、“一个实施例”、“另一实施例”、“一些实施例”、“各种实施例”、“其他实施例”、“替代实施例”等中的各种特征(例如,元素、结构、模块、组件、步骤、操作、特性等)的引用旨在表示任何这样的特征包括在本公开的一个或多个实施例中,但是可以或可以不必组合在相同的实施例中。此外,如本文所用,包括在权利要求中,“或”用于项目列表(例如,以诸如“至少一个”或“一个或多个”之类的短语开头的项目列表)表示包含列表,例如,[a、b或c中的至少一个]的列表表示a或b或c或ab或ac或bc或abc(即,a和b和c)。

[0148]

使用本领域技术人员通常使用的术语来描述说明性实施例的各个方面以将他们的工作的实质传达给本领域的其他技术人员。例如,术语“连接”是指被连接的事物之间的直接电气连接,没有任何中间设备/组件,而术语“耦合”是指被连接的事物之间的直接电气连接,或间接连接通过一个或多个被动或主动中间设备/组件。在另一示例中,术语“电路”表示一个或多个无源和/或有源组件,它们被布置为彼此协作以提供期望的功能。此外,如本文所用,术语“基本上”、“大约”、“大概”等基于如本文所述或本领域已知的特定值的上下文可用于一般指在目标值的+/-20%内,例如在目标值的+/-10%内。

[0149]

本领域技术人员可以确定许多其他变化、替换、变更和修改,并且本公开旨在包括落入实施例范围内的所有此类变化、替换、变更和修改和附加的权利要求。注意,上述装置的所有可选特征也可以相对于这里描述的方法或过程实施,并且示例中的细节可以在一个或多个实施例中的任何地方使用。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1