一种功率开关器件并联测试的PCB版图的制作方法

一种功率开关器件并联测试的pcb版图

技术领域

1.本实用新型属于功率开关器件测试技术领域,具体涉及一种功率开关器件并联测试的pcb版图。

背景技术:

2.图1为简化的双脉冲测试电路:图中带箭头的椭圆圈出的部分为驱动回路,lg为驱动回路中等效的寄生电感。寄生电感是指这个电感不是设计时故意设计出来的,是附加在某些东西上产生的。简单来讲,有导线的地方就有寄生电感。根据电磁感应定律,穿过线圈的磁通量发生变化时,线圈中会产生感应电势,电感越大,在磁通量变化时,产生的感应电压就越强。

3.在pcb布线中,每一条布线都会携带一定的寄生电感,其产生的感应电压会影响驱动电路对被测器件的驱动效果,导致被测器件开通的结果受影响。

4.pcb走线电感:其中w为走线宽度,l为走线长度。从以上公式可以看出,寄生电感l与走线的关系很大。

5.当进行器件并联测试时,各驱动回路杂散电感的一致性是非常重要的,非对称的栅极杂散电感可能导致igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)动态均流性能变差,影响整个系统的性能。所以要保证每一个并联被测器件的驱动回路电感一样。

6.现有进行器件并联测试时,忽略了驱动回路寄生电感的影响,基本是将被测器件一字排开,而一字排开的布局没有做到使驱动回路寄生电感保持一致,如图2所示,导致pcb布线的长度和整个回路的面积都有差别,从而产生不同的寄生电感,影响了动态测试的均流性,对测试结果和结论产生较大的影响。

7.如何提供一种使驱动回路寄生电感保持一致的pcb版图设计,是一个急需解决的问题。

技术实现要素:

8.本实用新型的主要目的在于提供一种功率开关器件并联测试的pcb版图,从而克服现有技术的不足。

9.为实现前述实用新型目的,本实用新型采用的技术方案包括:本实用新型实施例提供了一种功率开关器件并联测试的pcb版图,包括驱动及与所述驱动相连的多个被测器件,每个所述被测器件与驱动之间连接的驱动走线的面积相等。

10.在一优选实施例中,每个所述被测器件与驱动之间连接的驱动走线的线长和线宽相等。

11.在一优选实施例中,所述多个被测器件沿着以驱动为圆心的圆环上周向分布。

12.在一优选实施例中,所述多个被测器件沿着以驱动为圆心的圆环上周向均匀分

布。

13.在一优选实施例中,所述多个被测器件相并联。

14.在一优选实施例中,所述被测器件为碳化硅金氧半场效晶体管sic mosfet。

15.在一优选实施例中,所述驱动、被测器件和驱动走线均位于pcb板上。

16.与现有技术相比较,本实用新型的有益效果至少在于:本实用新型在功率开关器件的并联测试电路中,为保证各路驱动回路的一致性,设计以驱动为圆心,各被测器件放置于圆环上的一种版图,该方案能最大限度的保持各驱动回路的寄生大小相同,使得测试电路更加的一致,为分析并联器件的均流一致性排除更多的干扰。

附图说明

17.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型中记载的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

18.图1是现有简化的双脉冲测试电路的结构示意图;

19.图2是现有并联测试的pcb版图示意图;

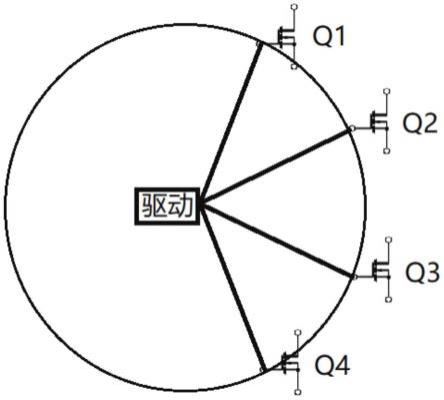

20.图3是本实用新型一实施方式中功率开关器件并联测试的pcb版图示意图。

具体实施方式

21.通过应连同所附图式一起阅读的以下具体实施方式将更完整地理解本实用新型。本文中揭示本实用新型的详细实施例;然而,应理解,所揭示的实施例仅具本实用新型的示范性,本实用新型可以各种形式来体现。因此,本文中所揭示的特定功能细节不应解释为具有限制性,而是仅解释为权利要求书的基础且解释为用于教示所属领域的技术人员在事实上任何适当详细实施例中以不同方式采用本实用新型的代表性基础。

22.如图3所示,本实用新型实施例所揭示的一种功率开关器件并联测试的pcb版图,其包括位于一pcb板上的驱动和多个被测器件,其中,每个被测器件均通过各自对应的驱动走线与驱动相连,且驱动走线也均布线于pcb上。多个被测器件之间相并联。

23.在一具体实施例中,多个被测器件沿着以驱动为圆心的圆环上周向分布,也就是说,驱动位于圆环的圆心上,多个被测器件则位于圆环的圆边上,沿着圆边周向分布。这样可以保证,每个被测器件与驱动之间的驱动走线大小是相同的,如驱动走线的驱动面积是相同的,具体如驱动走线的线宽和线长是相同的,这样,可以使得驱动回路的寄生电感保持一致,由上述pcb走线电感的公式可知,这样可以保证每一个并联被测器件的驱动回路电感一样,从而能最大限度的保持各驱动回路的寄生大小相同,使得测试电路更加的一致,为分析并联器件的均流一致性排除更多的干扰。

24.在圆环的圆边上,多个被测器件之间可以间隔均匀分布,也可以不间隔均匀分布,可以根据实际需要排布。如图3中,有4个被测器件,分别标识为q1、q2、q3和q4,每个被测器件与驱动之间的驱动走线分别标识为走线1、走线2、走线3和走线4,本实施例中,走线1~走线4的长度、线宽和驱动面积完全相同。

25.被测器件为功率开关器件,在一具体实施例中,具体可以是碳化硅金氧半场效晶

体管sic mosfet。

26.经过测试验证,本实用新型测试的结果与专业设备测出来的数据误差不超过5%,且数据本身并没有唯一值,所以误差几乎可忽略。

27.本实用新型具有以下优点:本实用新型在功率开关器件的并联测试电路中,为保证各路驱动回路的一致性,设计以驱动为圆心,各被测器件放置于圆环上的一种版图,该方案能最大限度的保持各驱动回路的寄生大小相同,使得测试电路更加的一致,为分析并联器件的均流一致性排除更多的干扰。

28.本实用新型的各方面、实施例、特征及实例应视为在所有方面为说明性的且不打算限制本实用新型,本实用新型的范围仅由权利要求书界定。在不背离所主张的本实用新型的精神及范围的情况下,所属领域的技术人员将明了其它实施例、修改及使用。

29.在本实用新型案中标题及章节的使用不意味着限制本实用新型;每一章节可应用于本实用新型的任何方面、实施例或特征。

技术特征:

1.一种功率开关器件并联测试的pcb版图,其特征在于:所述pcb版图包括驱动及与所述驱动相连的多个被测器件,每个所述被测器件与驱动之间连接的驱动走线的面积相等。2.根据权利要求1所述的一种功率开关器件并联测试的pcb版图,其特征在于:每个所述被测器件与驱动之间连接的驱动走线的线长和线宽相等。3.根据权利要求1所述的一种功率开关器件并联测试的pcb版图,其特征在于:所述多个被测器件沿着以驱动为圆心的圆环上周向分布。4.根据权利要求3所述的一种功率开关器件并联测试的pcb版图,其特征在于:所述多个被测器件沿着以驱动为圆心的圆环上周向均匀分布。5.根据权利要求1所述的一种功率开关器件并联测试的pcb版图,其特征在于:所述多个被测器件相并联。6.根据权利要求1所述的一种功率开关器件并联测试的pcb版图,其特征在于:所述被测器件为碳化硅金氧半场效晶体管sic mosfet。7.根据权利要求1所述的一种功率开关器件并联测试的pcb版图,其特征在于:所述驱动、被测器件和驱动走线均位于pcb板上。

技术总结

本实用新型公开了一种功率开关器件并联测试的PCB版图,包括驱动及与驱动相连的多个被测器件,每个被测器件与驱动之间连接的驱动走线的面积相等。本实用新型能最大限度的保持各驱动回路的寄生大小相同,使得测试电路更加的一致,为分析并联器件的均流一致性排除更多的干扰。的干扰。的干扰。

技术研发人员:刘大勇

受保护的技术使用者:苏州华太电子技术有限公司

技术研发日:2022.04.21

技术公布日:2022/8/15

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1