晶振控制电路的制作方法

本技术属于电子电路,涉及一种控制电路,尤其涉及一种晶振控制电路。

背景技术:

1、晶体振荡器(简称晶振)广泛应用于通信、导航、雷达等系统中,它由于体积小、功耗低,具有很好的频率稳定度,因此常被用作时钟基准源。近年来随着消费类电子设备的高速发展,手机、智能手环、蓝牙耳机等便携式设备的功耗及待机时长成为消费者迫切关注的性能指标,这就对便携式设备和芯片的设计者们提出了低功耗的设计要求。晶振作为大多数芯片尤其是消费类芯片的时钟基准源,它的起振时间和工作电流对整颗芯片的功耗都会有比较大的影响,低功耗快速起振晶振成为消费类芯片尤其是便携式设备领域不断优化的重要性能指标。

2、晶振的起振时间是晶振的重要性能指标,它不仅影响到晶振本身的功耗,也会影响整个芯片不同工作模式的切换时间,例如ble(蓝牙)协议中,不采取任何措施的情况下晶振起振时间会达到毫秒级别,而数据包传输时间为百微秒级别,因此晶振起振时间不仅影响了传输效率,而且在起振过程的空窗期浪费了更多的时间和功耗。

3、为缩短晶振的起振时间,目前主要有两种改进方式;一种是通过调整有源电路的负阻,使其达到最优的起振条件,但是负阻大小受限于偏置电流,同时最优起振条件也受晶振负载电容和晶体本身参数的影响,导致这种方案效果比较有限。另一种方式是通过外部同频时钟信号注入晶振两端加速起振,该方式要求外部时钟频率非常接近晶振本身频率,由于工艺、温度、电压的偏差很难保证外部时钟具有稳定不变的频率,这不仅增加了额外的外部时钟的功耗,而且加速起振的效果也无法得到保证。

4、文献[1](bramverhoef,janprummel,wimkruiskamp,rein,“a32mhzcrystaloscillatorwithfaststart-upusingsynchronizedsignalinjection”,isscc2019)中采用一个与晶振谐振频率接近的rc(电阻电容)振荡器间歇性的对晶振进行注入,直至晶振快速起振到设定的振荡幅度,每次注入开启前都需要校准rc振荡器的频率和相位与晶振时钟对齐,然而,这样的校准需要一个精确而复杂的反馈回路,包括温度传感器和电压传感器,否则随着工艺、电压和温度的偏差注入效果会差很多,这不仅增加了控制电路的复杂度也额外增加了系统功耗。

5、文献[2](shuntaiguchi,hiroshifuketa,takayasusakurai,makototakamiya,“variation-tolerantquick-start-upcmoscrystaloscillatorwithchirpinjectionandnegativeresistancebooster”,ieeejournalofsolid-statecircuits,vol.51,no.2,february2016)中采用了ci(chripinjector)注入加速晶振起振的方式,该方案核心为chrip信号发生器,由一个vco(压控振荡器)和扫描电路组成,即通过电阻电容(rc)组成的放电电路来调整vco的控制电压来实现扫频,该方案只要设计vco谐振频率范围足够大(0.5fosc~2fosc)就可以克服工艺、温度、电压的影响而覆盖到晶振谐振频率。但是该方案需要一个预充放电电路和一个宽带vco,而且由于同频注入的时间窗口不可控,从最终的实测结果来看在功耗和性能上的优势都不显著。

6、有鉴于此,如今迫切需要设计一种新的晶振控制电路,以便克服现有晶振控制电路存在的上述至少部分缺陷。

技术实现思路

1、本实用新型提供一种晶振控制电路,可有效缩短起振时间,且不受温度、工艺和电压偏差影响,性能稳定。

2、为解决上述技术问题,根据本实用新型的一个方面,采用如下技术方案:

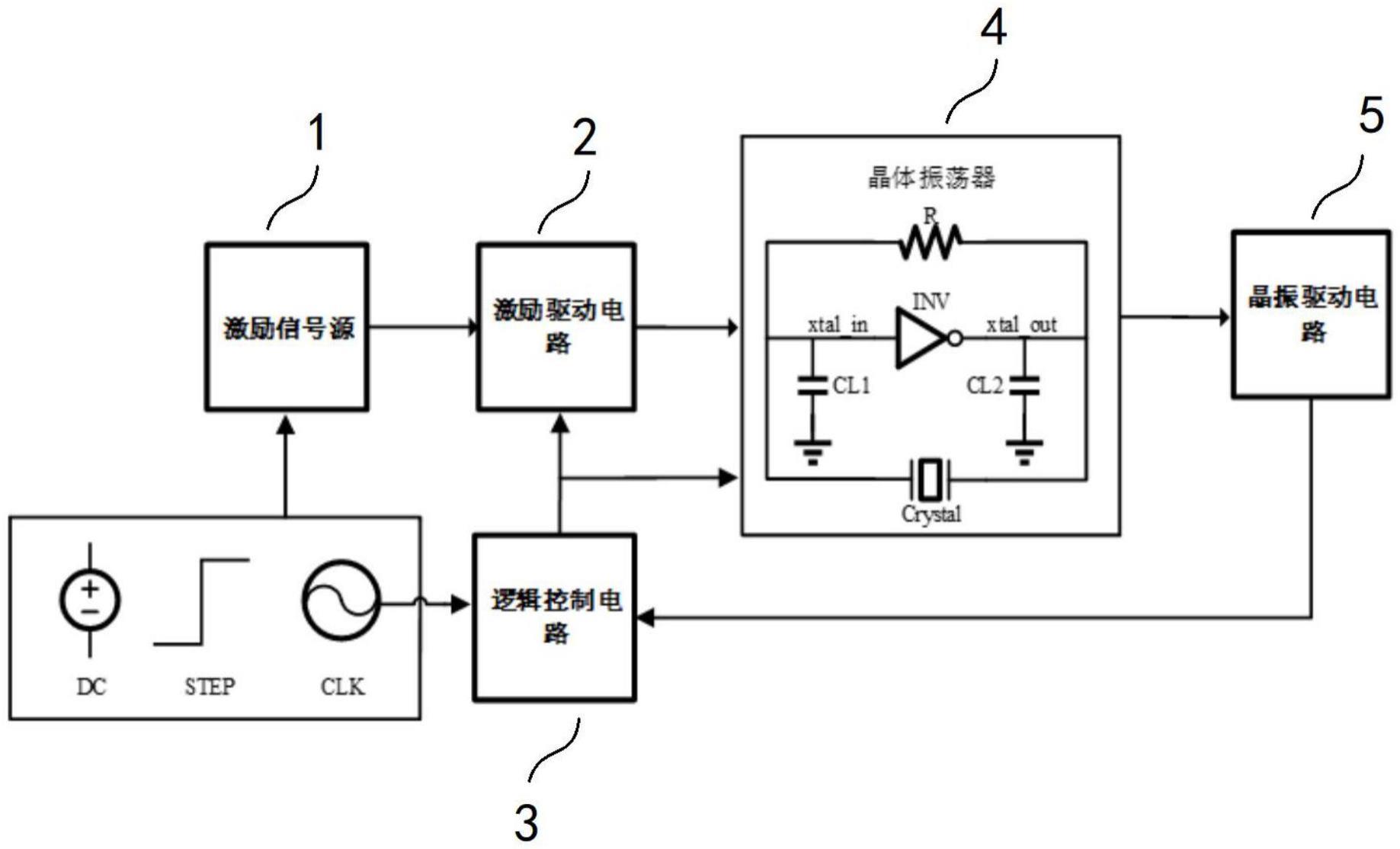

3、一种晶振控制电路,所述晶振控制电路包括:激励信号源、激励驱动电路、逻辑控制电路、晶体振荡器和晶振驱动电路;

4、所述激励信号源用于产生激励信号;

5、所述激励驱动电路分别连接激励信号源及逻辑控制电路,用以将所述激励信号源产生的激励信号注入到晶体振荡器的输入节点xtal_in或者输出节点xtal_out,激励信号注入过程的导通与关断受所述逻辑控制电路控制;

6、所述晶体振荡器用以将产生的时钟信号输出到晶振驱动电路并通过晶振驱动电路进一步输送给芯片其他模块提供基准时钟,同时晶振驱动电路也会将时钟输送给逻辑控制电路用于做后续逻辑控制。

7、作为本实用新型的一种实施方式,所述晶体振荡器包括反馈电阻r、反相器inv、外部晶体crystal、第一负载电容cl1、第二负载电容cl2;

8、所述反相器inv的第一端分别连接反馈电阻r的第一端、第一负载电容cl1的第一端、外部晶体crystal的第一端;第一负载电容cl1的第二端接地;

9、所述反相器inv的第二端分别连接反馈电阻r的第二端、第二负载电容cl2的第一端、外部晶体crystal的第二端;第二负载电容cl2的第二端接地。

10、作为本实用新型的一种实施方式,所述激励信号包括直流电压信号dc、阶跃信号step、时钟信号clk中的至少一个。

11、作为本实用新型的一种实施方式,所述逻辑控制电路包括第一计数器、第二计数器、d触发器dff、异或门xor、选通器mux;

12、所述第一计数器的第一输入端连接振荡器输出的第一振荡信号clk_a,第一计数器的第二输入端连接配置第一计数器记录第一振荡信号clk_a的时钟周期数信号;所述第一计数器的输出端连接异或门xor的第一输入端;

13、所述d触发器dff的第一输入端连接振荡器输出的第一振荡信号clk_a,d触发器dff的输出端连接异或门xor的第二输入端;异或门xor的输出端连接激励驱动电路;

14、所述第二计数器的第一输入端连接晶振驱动电路输出的晶振时钟信号clk_b,第二计数器的第二输入端连接配置第二计数器记录晶振时钟信号clk_b的时钟周期数信号;所述第二计数器的输出端连接选通器mux的输入端,控制选通器mux的工作。

15、本实用新型的有益效果在于:本实用新型提出的晶振控制电路,可有效缩短起振时间,且不受温度、工艺和电压偏差影响,性能稳定。

16、本实用新型的方案简单可行,可复用系统内部其他时钟(频率选择范围大,无需晶振同频时钟)来计数,而不需要单独提供时钟,降低了功耗。

17、本实用新型中,激励信号可选择范围大,既可以是直流电压信号、阶跃信号等,也可以是时钟信号(同频或者不同频均可)等等,降低了模块设计复杂度,在功耗和面积上优势明显。

18、同时,本实用新型方案的负阻调整控制逻辑方案可用于跟晶振有源负阻相关的各种参数(如负载电容、有效跨导、偏置电流等)自检测分段式调控,具有极强的适应性和可拓展性。

19、此外,本实用新型的逻辑控制模式清晰明了,可以在模拟域实现快速起振所需的所有逻辑控制,省略了与数字域在功能上的交互(如时钟频率、时钟相位同步等),方案实现更加独立。

- 还没有人留言评论。精彩留言会获得点赞!