基于帧交错处理的LDPC译码方法和LDPC译码器

本发明涉及信道编码,尤其涉及一种基于帧交错处理的ldpc译码方法和ldpc译码器。

背景技术:

1、为了满足对第五代移动通信技术(5g)告诉通信的不同需求,研究人员开发出了多种不同编译码技术,其中,低密度奇偶校验(ldpc)码被确定为数据信道的纠错编码方案。5g标准给定的校验矩阵校验节点度分布非常不均匀,连续行之间正交性很差,导致在读取节点时容易发生内存访问冲突,一旦发生内存访问冲突,将直接影响译码性能,严重导致译码失败。

2、现有的为了避免发生内存访问冲突的技术是插入空闲周期技术。在迭代译码中,节点根据校验矩阵的行序号分为若干层,并逐层进行节点更新。插入空闲周期技术是指在向内存读取某一层某一个节点前,判断该节点在上一层的更新是否已经完成并写入内存,若还未更新完成,则插入空闲周期,直到该节点在上一层的更新过程结束才开始读取该节点。然而,插入空闲周期会增加迭代译码需要的时间,大幅度降低译码器吞吐率以及硬件资源利用率。因此,有必要提供一种新的ldpc译码方法,用来在解决内存访问冲突时,减少插入空闲周期,提高译码器吞吐率以及硬件资源利用率。

技术实现思路

1、本发明提供了一种基于帧交错处理的ldpc译码方法和ldpc译码器,用于解决使用插入空闲周期来避免发生内存访问冲突带来的增加迭代译码需要的时间,大幅度降低译码器吞吐率和硬件资源利用率的技术问题。

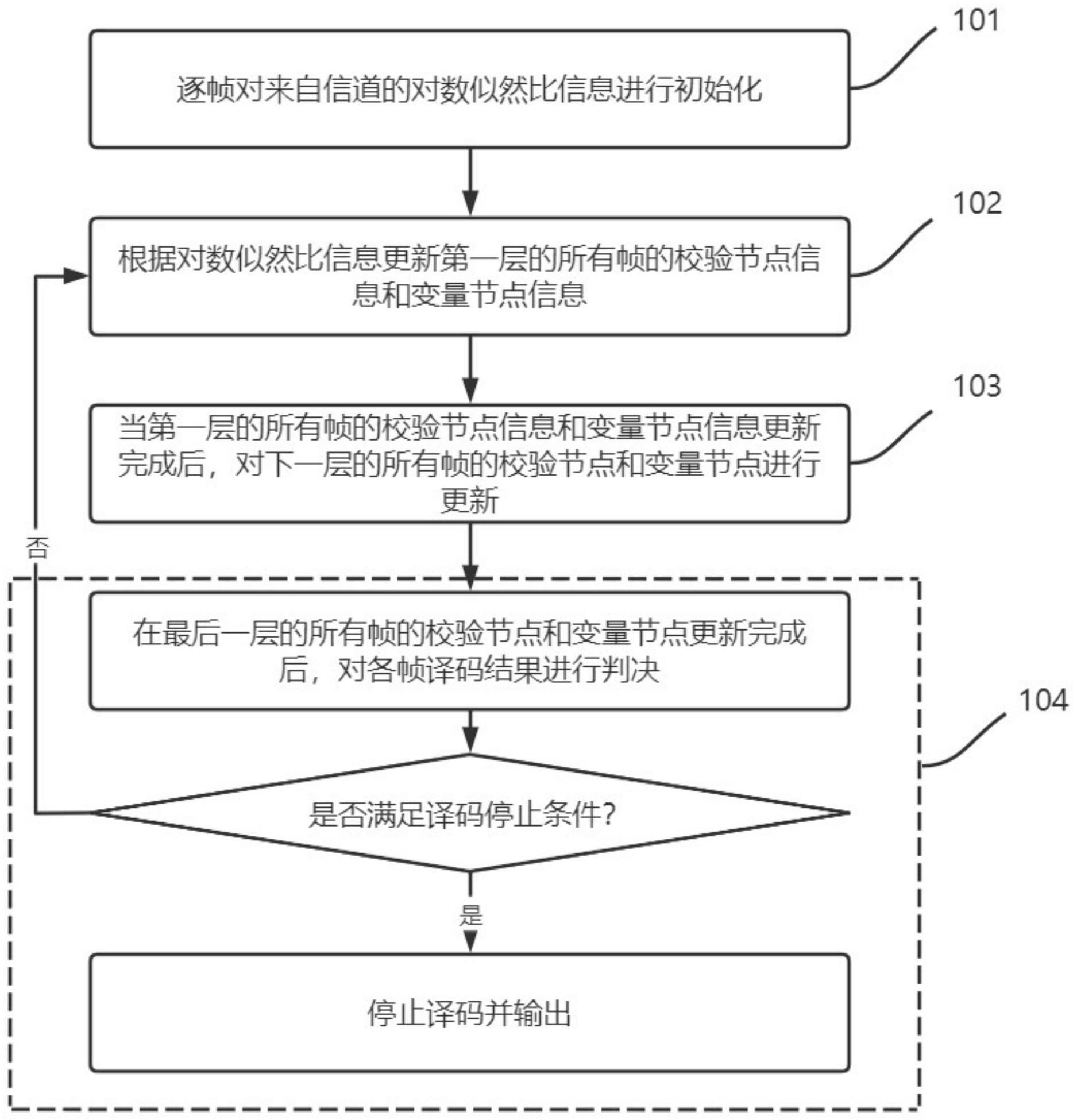

2、有鉴于此,本发明第一方面提供了一种基于帧交错处理的ldpc译码方法,包括:

3、s1、逐帧对来自信道的对数似然比信息进行初始化;

4、s2、根据对数似然比信息更新第一层的所有帧的校验节点信息和变量节点信息;

5、s3、当第一层的所有帧的校验节点信息和变量节点信息更新完成后,对下一层的所有帧的校验节点和变量节点进行更新;

6、s4、在最后一层的所有帧的校验节点和变量节点更新完成后,对各帧译码结果进行判决,并判断是否满足译码停止条件,若是,则停止译码并输出,若否,则返回步骤s2继续进行译码迭代。

7、可选地,步骤s4中,译码停止条件为或达到最大迭代次数,其中,h为校验矩阵,为译码后的码字序列的转置。

8、可选地,采用最小和译码算法更新校验节点信息和变量节点信息。

9、本发明第二方面提供了一种基于帧交错处理的ldpc译码器,包括:

10、检测模块,用于当出现异常片时,检测贴胶缓存的当前位置;

11、帧控制模块,用于控制当前译码的帧序号;

12、节点地址存储模块,用于根据给定的校验节点生成节点的地址值和对应的移位系数;

13、llr存储模块,用于存储变量节点信息;

14、校验信息存储模块,用于存储校验节点信息;

15、循环移位模块,用于对读取的对数似然比信息进行循环移位操作;

16、反循环移位模块,用于对写入的对数似然比信息进行反循环移位操作;

17、节点更新模块,用于对校验节点信息和变量节点信息进行更新;

18、译码判决模块,用于存储译码结果和判断是否满足译码停止条件,若是,则停止译码并输出,若否,则继续进行译码迭代。

19、可选地,译码停止条件为或达到最大迭代次数,其中,h为校验矩阵,为译码后的码字序列的转置。

20、可选地,节点更新模块采用最小和译码算法更新校验节点信息和变量节点信息。

21、从以上技术方案可以看出,本发明提供的基于帧交错处理的ldpc译码方法和装置具有以下优点:

22、本发明提供的基于帧交错处理的ldpc译码方法,将现有的单帧译码扩展为多帧交错译码,在读取完某一帧某一层节点后,继续读取下一帧该层的节点,直到全部帧在该层的节点读取完成之后再读取下一层节点,如此,该层的节点有足够的时间完成更新,避免了内存访问冲突,在读取下一层时减少了插入空闲周期,甚至不需要插入空闲周期,提高了译码吞吐量和硬件资源利用率,解决了使用插入空闲周期来避免发生内存访问冲突带来的增加迭代译码需要的时间,大幅度降低译码器吞吐率和硬件资源利用率的技术问题。

23、本发明提供的基于帧交错处理的ldpc译码装置,用于执行本发明提供的基于帧交错处理的ldpc译码方法,其原理和所取得的技术效果与本发明提供的基于帧交错处理的ldpc译码方法相同,在此不再赘述。

技术特征:

1.一种基于帧交错处理的ldpc译码方法,其特征在于,包括:

2.根据权利要求1所述的基于帧交错处理的ldpc译码方法,其特征在于,步骤s4中,译码停止条件为或达到最大迭代次数,其中,h为校验矩阵,为译码后的码字序列的转置。

3.根据权利要求1所述的基于帧交错处理的ldpc译码方法,其特征在于,采用最小和译码算法更新校验节点信息和变量节点信息。

4.一种基于帧交错处理的ldpc译码器,其特征在于,包括:

5.根据权利要求4所述的基于帧交错处理的ldpc译码器,其特征在于,译码停止条件为或达到最大迭代次数,其中,h为校验矩阵,为译码后的码字序列的转置。

6.根据权利要求4所述的基于帧交错处理的ldpc译码器,其特征在于,节点更新模块采用最小和译码算法更新校验节点信息和变量节点信息。

技术总结

本发明公开了一种基于帧交错处理的LDPC译码方法和LDPC译码器,将现有的单帧译码扩展为多帧交错译码,在读取完某一帧某一层节点后,继续读取下一帧该层的节点,直到全部帧在该层的节点读取完成之后再读取下一层节点,如此,该层的节点有足够的时间完成更新,避免了内存访问冲突,在读取下一层时减少了插入空闲周期,甚至不需要插入空闲周期,提高了译码吞吐量和硬件资源利用率,解决了使用插入空闲周期来避免发生内存访问冲突带来的增加迭代译码需要的时间,大幅度降低译码器吞吐率和硬件资源利用率的技术问题。

技术研发人员:韩国军,杨伟泽,翟雄飞

受保护的技术使用者:广东工业大学

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!