一种多路子ADC采样电路、半导体器件及信号处理装置的制作方法

本发明涉及模拟集成电路,尤其涉及一种多路子adc采样电路、半导体器件及信号处理装置。

背景技术:

1、随着科技的发展,半导体工艺下生产的单路adc(模数转换器)的采样率和精度通常非常接近其制造工艺的极限,提高采样率的同时势必要牺牲采样精度,因此,可以通过更换更先进的半导体制造工艺,在保持这个adc原有精度的基础上继续提高采样率,也可以采样时域交织技术,在不牺牲太多精度的条件下继续提升adc的采样率。

2、时域交织adc采样可以在不牺牲太多精度条件下提升采样率,时域交织adc采样是采用多个子adc交替采样,并且把多个子adc的数字输出按照采样顺序进行拼接的采样过程。由于子路adc失配造成adc整体输出频谱产生额外杂散,因此需要消除杂散。

3、目前,时域交织adc采样消除杂散通常采用通道间的校准算法来降低杂散,然而现有技术中的方法很难完全消除杂散。

技术实现思路

1、本发明提供了一种多路子adc采样电路、半导体器件及信号处理装置,以解决现有技术中很难完全消除时域交织adc采样出现的杂散的问题。

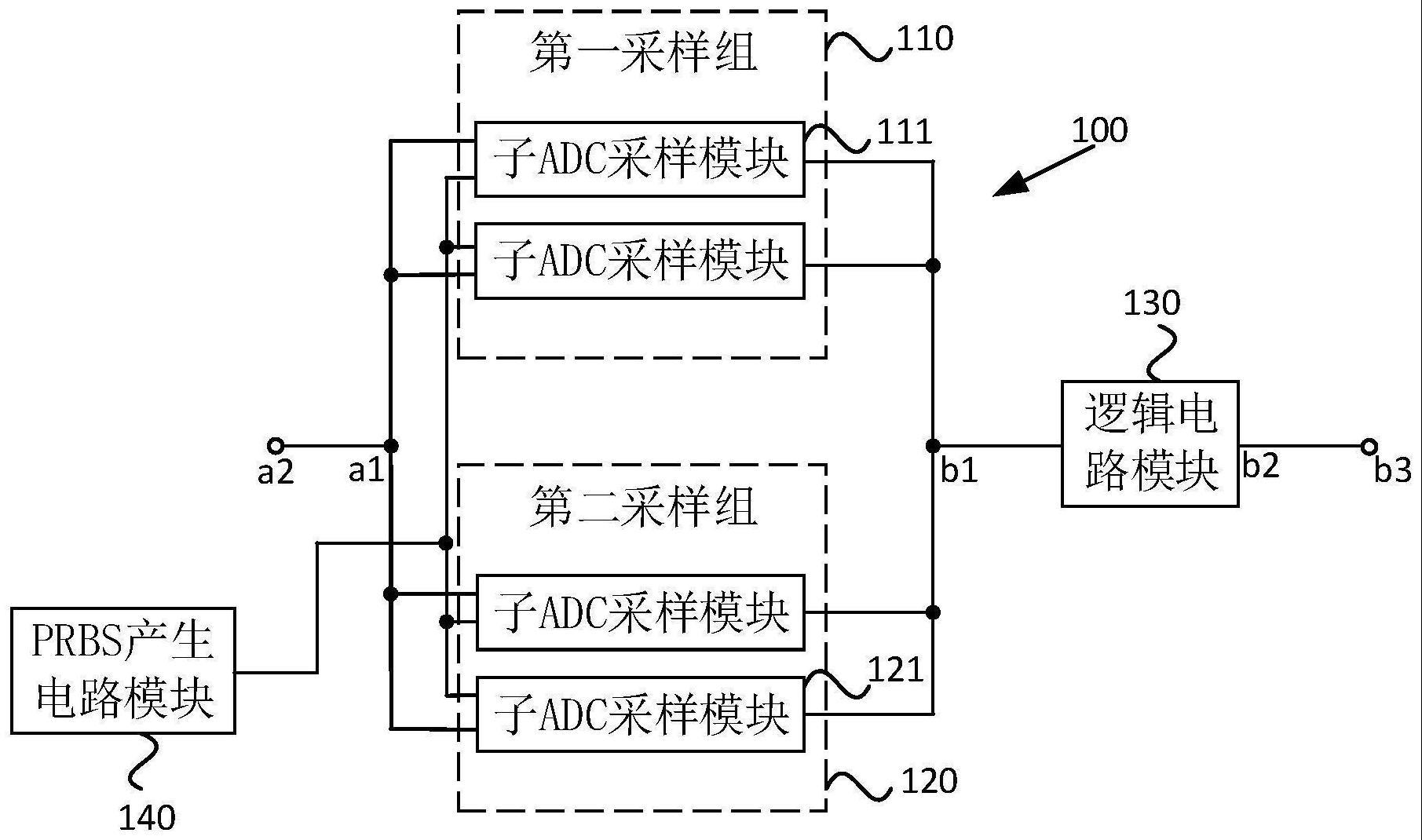

2、根据本发明的一方面,提供了一种多路子adc采样电路,该电路包括:

3、第一采样组,包括两个或以上数量的子adc采样模块;所述第一采样组接入第一采样时钟;

4、第二采样组,包括一个子adc采样模块;所述第二采样组接入第二采样时钟;所述第一采样时钟与所述第二采样时钟交替输出;

5、各所述子adc采样模块的输入端均与所述多路子adc采样电路的输入端电连接;

6、逻辑电路模块,各所述子adc采样模块的输出端均与所述逻辑电路模块电连接,所述逻辑电路模块的输出端与所述多路子adc采样电路的输出端电连接;所述逻辑电路模块用于将各所述子adc采样模块输出的采样信号进行拼接后输出;

7、prbs产生电路模块,与各所述子adc采样模块电连接;所述prbs产生电路模块用于随机选择所述第一采样组中的一个用于采样的所述子adc采样模块,以及选择所述第二采样组中用于采样的所述子adc采样模块。

8、可选的,所述第一采样时钟对应于所述第一采样组中包括的所述子adc采样模块,所述子adc采样模块对应的第一采样时钟固定,所述子adc采样模块的工作时序相同。

9、可选的,当所述第一采样时钟进行到采样进程,所述ppbs产生电路模块会随机选出所述第一采样组中的一个子adc采样模块进行采样,所述第一采样组中其余没有选中进行采样的子adc采样模块继续完成其内部数据处理工作。

10、可选的,所述第二采样组包括两个或以上数量的子adc采样模块,所述第二采样时钟对应于所述第二采样组中包括的所述子adc采样模块,所述adc采样模块所对应的第二采样时钟固定,所述adc采样模块的工作时序相同。

11、可选的,当所述第二采样时钟进行到采样进程,所述ppbs产生电路模块会随机选出所述第二采样组中的一个子adc采样模块进行采样,所述第二采样组中其余没有选中进行采样的子adc采样模块则继续完成其内部数据处理工作。

12、可选的,所述多路子adc采样电路还包括第三采样组,所述第三采样组包括一个子adc采样模块;所述第三采样组接入第三采样时钟,第三采样组与所述第一采样组并联连接;所述第一采样时钟、所述第二采样时钟和所述第三采样时钟随机交替输出;所述prbs产生电路模块还用于选择所述第三采样组中用于采样的所述子adc采样模块。

13、可选的,所述第三采样组包括两个或以上数量的子adc采样模块,所述第三采样时钟对应于所述第三采样组中包括的所述子adc采样模块,所述adc采样模块所对应的第三采样时钟固定,所述adc采样模块的工作时序相同。

14、可选的,当所述第三采样时钟进行到采样进程,所述ppbs产生电路模块随机选出所述第三采样时间所对应的所述第三采样组中的一个子adc采样模块进行采样,所述第三采样组中其余没有采样的子adc采样模块则继续完成其内部数据处理工作。

15、可选的,所述多路子adc采样电路输出的交织采样的种类等于各所述采样组包括的子adc采样模块的个数之间的乘积。

16、例如,当所述多路子adc采样电路包括两个采样组时,所述多路子adc采样电路输出的交织采样的种类等于所述第一采样组中子adc采样模块的个数和所述第二采样组中子adc采样模块的个数的乘积;当所述多路子adc采样电路包括3个采样组时,所述多路子adc采样电路输出的交织采样的种类等于所述3个采样组中子adc采样模块个数之间的乘积。

17、在一实施例中,所述第一采样组和所述第二采样组均包括两个子adc采样模块;所述多路子adc采样电路随机输出四种交织采样。

18、在又一实施例中,所述第一采样组包括两个子adc采样模块;所述第二采样组包括三个子adc采样模块;所述多路子adc采样电路随机输出六种交织采样。

19、在又一实施例中,所述第一采样组、所述第二采样组以及第三采样组均包括两个子adc采样模块;所述多路子adc采样电路随机输出八种交织采样。

20、可选的,所述子adc采样模块包括开关和子adc采样电路;所述开关和所述子adc采样电路串联于所述多路子adc采样电路的输入端和输出端之间;所述prbs产生电路模块与各所述开关电连接,所述prbs产生电路模块通过控制所述开关的导通来选择所述子adc采样电路。

21、可选的,所述多路子adc采样电路还包括输入缓冲模块,串联于所述多路子adc采样电路的输入端和各所述子adc采样模块的输入端之间。

22、可选的,所述多路子adc采样电路还包括时钟模块,所述时钟模块的输出端连接各所述子adc采样模块的输入端,所述时钟模块用于产生不同子adc采样模块所需的时钟脉冲,并将产生的时钟脉冲发送到对应的子adc采样模块。

23、根据本发明的另一方面,提供了一种半导体器件,所述半导体器件包括所述多路子adc采样电路。

24、可选的,所述半导体器件包括但不限于模数转换器。

25、根据本发明的另一方面,提供了一种信号处理装置,其包括本发明涉及的所述半导体器件。

26、可选的,所述信号处理装置包括示波器,例如,示波器包括但不限于数字示波器。

27、根据本发明的另一方面,提供了一种多路子adc采样电路的控制方法,该控制方法包括:

28、在第一采样时钟内,随机选择所述第一采样组中的一个所述子adc采样模块进行采样;

29、在第二采样时钟内,随机选择所述第二采样组中的一个所述子adc采样模块进行采样;

30、将所述第一采样组输出的采样信号和所述第二采样组输出的采样信号进行拼接。

31、本发明实施例的技术方案,提供了一种多路子adc采样电路,该电路包括第一采样组,第一采样组包括两个或以上数量的子adc采样模块,第一采样组接入第一采样时钟;多路子adc采样电路包括第二采样组,第二采样组包括一个或以上数量的子adc采样模块,第二采样组接入第二采样时钟;第一采样时钟与第二采样时钟交替输出,每个采样组采用相同的时钟减少了每个子adc采样模块的内部干扰。多路子adc采样电路包括prbs产生电路模块,prbs产生电路模块与各子adc采样模块电连接,ppbs产生电路模块用于随机选择第一采样组中用于采样的子adc采样模块,以及随机选择第二采样组中用于采样的子adc采样模块,多路子adc采样电路通过逻辑电路模块将各子adc采样模块输出的采样数据进行拼接后输出,多路子adc采样电路输出多种组合的交织采样,且每种组合的交织采样是随机的,本发明实现了多路子adc采样电路的随机采样,通过随机化技术可以使杂散平均到整个频带内使其表现为噪声,解决了现有技术中很难完全消除时域交织adc采样出现的杂散的问题。

32、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!