半导体存储装置及半导体存储装置的制造方法、与半导体晶圆与流程

本发明的实施方式涉及一种半导体存储装置及半导体存储装置的制造方法、与半导体晶圆。

背景技术:

1、已知一种由存储单元三维积层而得的贴合构造的nand(not and,与非)闪速存储器。

技术实现思路

1、本发明所欲解决的问题在于提供一种简化了贴合步骤的积层型半导体存储装置及半导体存储装置的制造方法、与半导体晶圆。

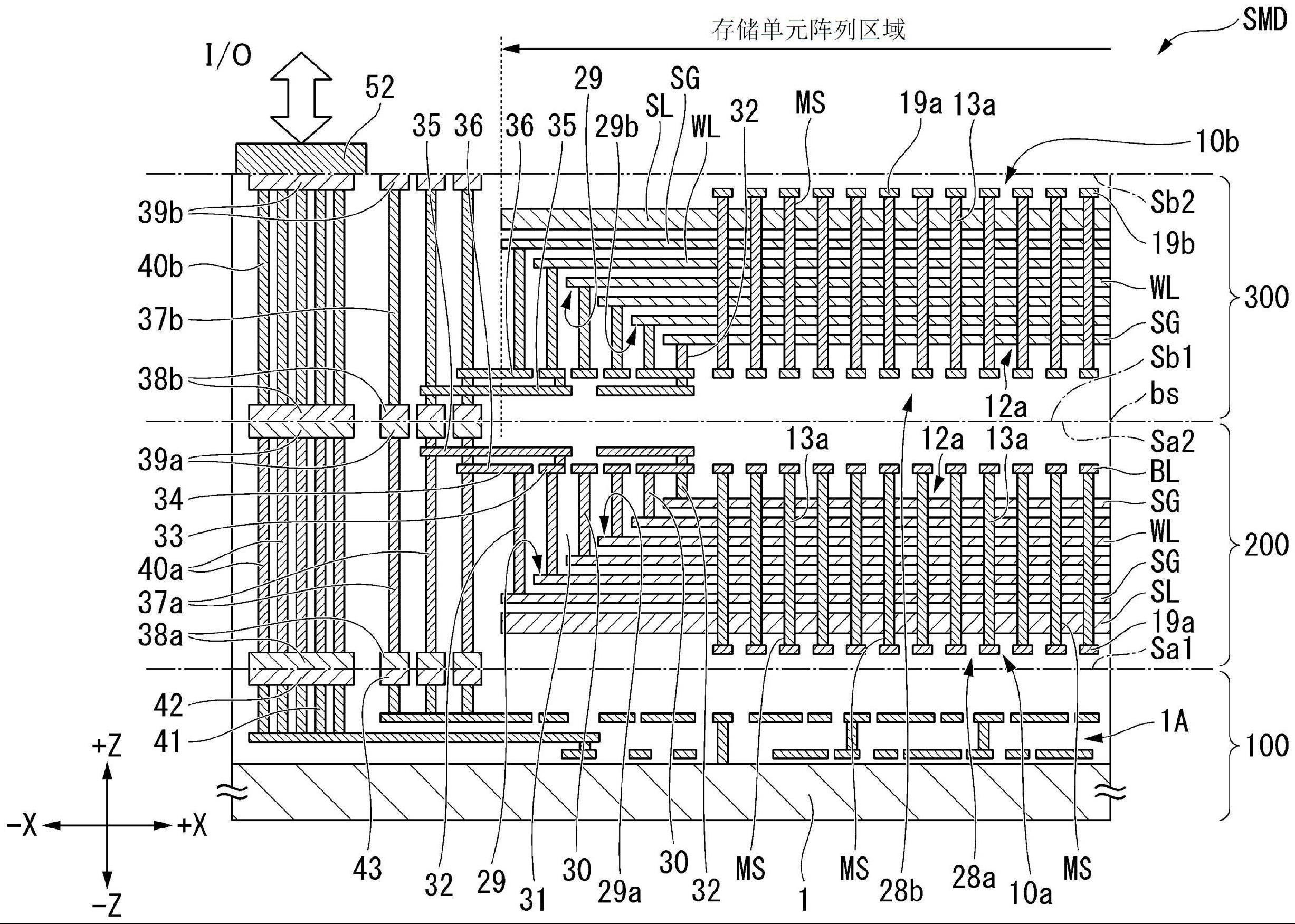

2、实施方式的半导体存储装置具有多个存储单元阵列层,所述多个存储单元阵列层具有第1面及与第1面为相反侧的第2面,且不包含衬底,并且具有三维配置在存储单元阵列区域的多个存储单元。所述多个存储单元阵列层具有嵌埋在所述第1面及所述第2面的表面配线层。所述存储单元具有隔着多个绝缘层将多个电极层积层而得的积层体,所述积层体具有使多个所述电极层的端部位置逐一积层位置地偏移后所得的阶梯构造部。多个所述存储单元阵列层以将形成在所述第1面或所述第2面的表面配线层连接的方式积层,在所述积层体的积层方向上相邻的所述存储单元阵列层是以使彼此的阶梯构造部的倾斜部朝向在所述积层方向上相邻的存储单元阵列层之间的积层交界面的方式积层,从而构成半导体存储装置。

技术特征:

1.一种半导体存储装置,

2.根据权利要求1所述的半导体存储装置,其中

3.根据权利要求1所述的半导体存储装置,其中

4.根据权利要求1所述的半导体存储装置,其中所述存储单元阵列层的积层交界面为贴合面。

5.根据权利要求1所述的半导体存储装置,其中

6.一种半导体存储装置的制造方法,其是将第1衬底、第2衬底及第3衬底贴合而制造半导体存储装置的方法,

7.根据权利要求6所述的半导体存储装置的制造方法,其中

8.根据权利要求6所述的半导体存储装置的制造方法,其中

9.根据权利要求6所述的半导体存储装置的制造方法,其中

10.一种半导体晶圆,具有:

11.根据权利要求10所述的半导体晶圆,其

12.根据权利要求10所述的半导体晶圆,其中

技术总结

本发明的实施方式提供一种半导体存储装置及半导体存储装置的制造方法、与半导体晶圆。实施方式的半导体存储装置具有多个存储单元阵列层,所述多个存储单元阵列层具有第1面及与第1面为相反侧的第2面,且不包含衬底,并且具有三维配置在存储单元阵列区域的多个存储单元。所述存储单元阵列层具有嵌埋在第1面及第2面的表面配线层。存储单元具有隔着多个绝缘层将多个电极层积层而得的积层体,积层体具有使所述多个电极层的端部位置逐一积层位置地位置偏移后所得的阶梯构造部。多个存储单元阵列层以将形成在第1面或第2面的表面配线层连接的方式积层,在积层体的积层方向上相邻的存储单元阵列层是以使彼此的阶梯构造部朝向积层交界面的方式积层。

技术研发人员:蘆立浩明,竹石知之

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!