一种基于电压回补的SAR型ADC及其校准方法

本发明属于模数转换,具体涉及一种基于电压回补的sar型adc及其校准方法。

背景技术:

1、adc作为模拟信号量化的关键芯片,受到研究人员和工程师的关注与研究,而得益于先进工艺的发展,如今工艺已经步入纳米级别,sar adc作为一种传统的adc架构,更能从工艺进步中受益,相对于其他结构的adc,sar adc具备更小的面积和更低的功耗。

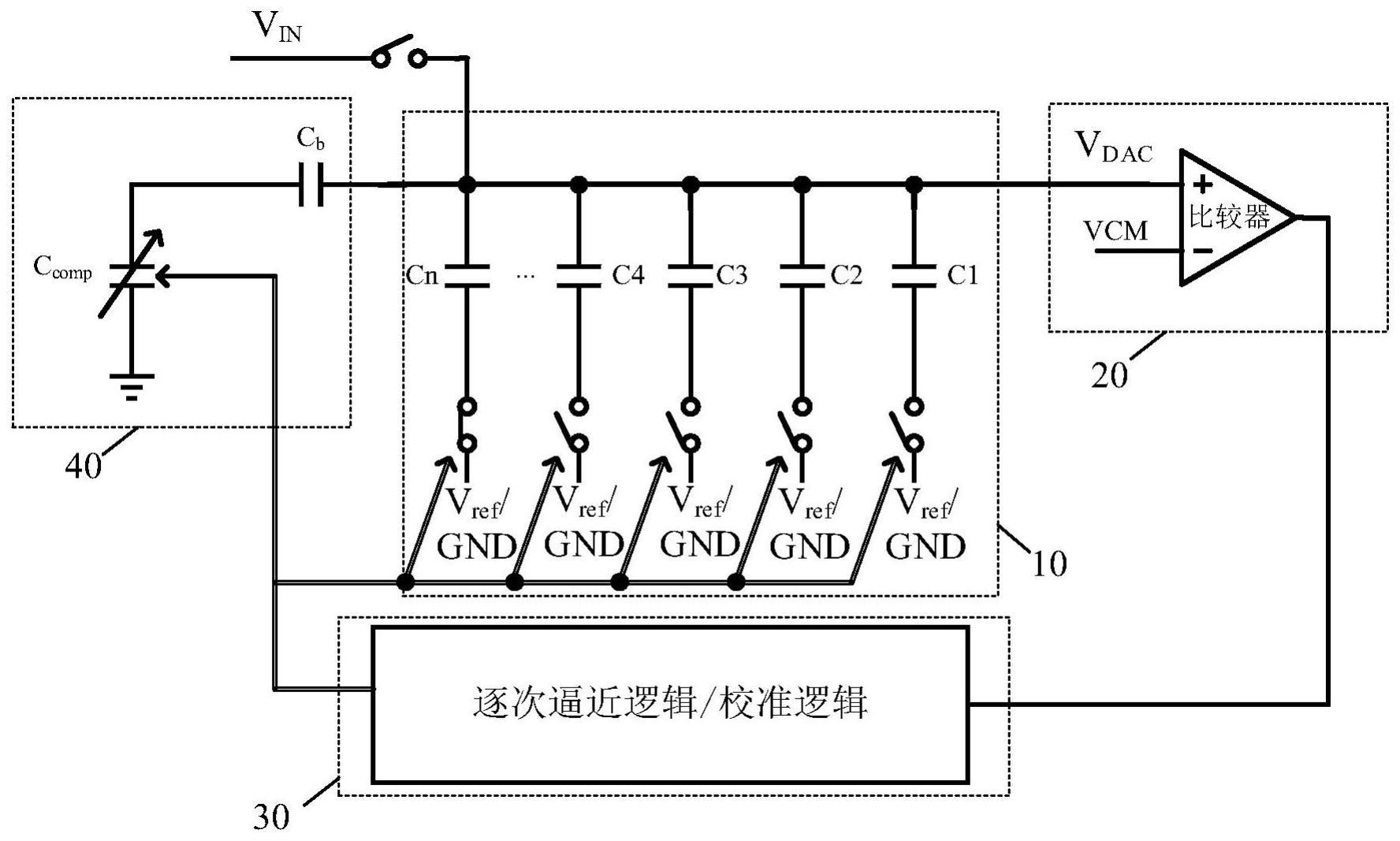

2、如图1所示为sar adc的框图,其主要包括cdac电路,比较器和逐次逼近逻辑,其中cdac电路嵌入了采样电路。逐次逼近是利用二分法对输入电压进行量化,采样输入电压完成后,利用cdac电路中的电容阵列从高位电容到低位电容依次产生二进制电压与输入电压信号进行比较,经过n次比较后,完成一次电压量化。

3、受限于制造工艺的水平,电容阵列中的电容产生的二进制电压并不严格服从二倍关系,而是存在误差电压,因此需要使用校准对这部分误差电压进行补偿,提高电容之间的匹配性。除此以外,为了应对特殊的应用场景,比如高低温、高低压以及抗辐射等特殊场合,sar adc的线性度会随着环境的变化而恶化,所以需要采用自校准技术,当系统感知到环境发生变化时,可以对sar adc进行一次自校准,保持芯片性能一致性。

技术实现思路

1、针对以上的技术问题,本发明提出了一种基于电压回补的sar型adc及其校准方法。

2、本发明的技术方案是:

3、一种基于电压回补的sar型adc,包括cadc电路模块、比较器、逐次逼近逻辑和校准逻辑模块、校准补偿电路模块;所述cadc电路模块包括n条支路,每条支路都由一个电容和一个开关串联构成,所有电容的一端连接构成cadc电路模块的分压端口,该端口与电源连接,并且该端口还分别与校准补偿电路模块和比较器的正输入端连接;cadc电路模块中每一支路的开关在使能端控制下连接基准电压或者地;比较器的负输入端接adc的共模电压,比较器的输出端接逐次逼近逻辑和校准逻辑模块的输入端;校准补偿电路模块包括桥接电容和补偿电容阵列,其中桥接电容的一端连接cadc电路模块的一个端口,桥接电容的另一端接补偿电容阵列的一端,补偿电容阵列的另一端接地;所述逐次逼近逻辑和校准逻辑模块的输出端接cadc电路模块中所有开关的使能端、以及补偿电容阵列的开关;逐次逼近逻辑和校准逻辑模块用于控制校准补偿电路模块提取误差电压。

4、上述方案中,采样电路嵌入到cdac电路中,逐次逼近与校准逻辑产生n条和m条控制线,分别与cdac电路的电容阵列的开关和校准补偿电路的电容补偿阵列开关连接,校准补偿电路主要由桥接电容cb以及补偿电容阵列ccomp,桥接电容cb用来做系数缩减,这种分段式电容结构可以减少电容阵列的面积,同时提高补偿电容阵列的回补精度。补偿电容阵列ccomp是用来在测量状态提取cdac电路中每个电容的误差电压,同时在正常工作状态的时候,提供回补电压。

5、一种基于电压回补的sar型adc的校准方法,包括:

6、提取cadc电路模块中全部n个电容的误差电压,具体为:先控制adc进入采样状态,同时将当前校准电容ci接基准电压,小于当前电容ci容值的c1~ci-1接地,大于当前电容ci容值的电容ci+1~cn接地;然后使adc进入转换状态,同时将当前校准电容ci接地,小于当前电容ci容值的电容c1~ci-1接基准电压,大于当前电容ci容值的电容ci+1~cn仍然接地;如果当前电容ci与低段电容c1~ci-1的和存在失配容值δc,切换过后出现在分压端口的电压则代表失配容值δc所代表的电压,从而提取当前电容ci的误差电压vres,i,遍历c1~cn获得全部误差电压为vres,1~vres,n;

7、将获得的误差电压存储在寄存器中;

8、在正常工作状态,采样输入电压,利用补偿电容阵列进行电压比较,当比较器输出为高电平时,将存储在寄存器中的误差电压码字利用校准补偿电容阵列回补当前使用电容的负误差电压-vres,i,当比较器输出为低电平时,将存储在寄存器中的误差电压码字利用校准补偿电容阵列回补当前使用电容的正误差电压vres,i。

9、本发明有益效果为:本发明提供了一种基于电压回补的sar型adc结构与校准方法,这种属于自校准方法,无需任何的外部信号,在任意时刻都可以开启校准状态,进行adc自校准,适用于任何环境,提升鲁棒性。该方法是利用电容切换得到电容阵列中单个电容的误差大小,从而在正常使用状态,回补由不匹配导致的误差电压,提高adc的线性度,同时利用桥接电容对补偿电路的电容阵列进行缩放,可以降低校准电路的面积,同时增大校准的范围。

技术特征:

1.一种基于电压回补的sar型adc,其特征在于,包括cadc电路模块、比较器、逐次逼近逻辑和校准逻辑模块、校准补偿电路模块;所述cadc电路模块包括n条支路,每条支路都由一个电容和一个开关串联构成,所有电容的一端连接构成cadc电路模块的分压端口,该端口与电源连接,并且该端口还分别与校准补偿电路模块和比较器的正输入端连接;cadc电路模块中每一支路的开关在使能端控制下连接基准电压或者地;比较器的负输入端接adc的共模电压,比较器的输出端接逐次逼近逻辑和校准逻辑模块的输入端;校准补偿电路模块包括桥接电容和补偿电容阵列,其中桥接电容的一端连接cadc电路模块的一个端口,桥接电容的另一端接补偿电容阵列的一端,补偿电容阵列的另一端接地;所述逐次逼近逻辑和校准逻辑模块的输出端接cadc电路模块中所有开关的使能端、以及补偿电容阵列的开关;逐次逼近逻辑和校准逻辑模块用于控制校准补偿电路模块提取误差电压。

2.用于如权利要求1所述的一种基于电压回补的sar型adc的校准方法,其特征在于,包括:

技术总结

本发明属于模数转换技术领域,具体涉及一种基于电压回补的SAR型ADC及其校准方法。本发明的方法属于自校准方法,无需任何的外部信号,在任意时刻都可以开启校准状态,进行ADC自校准,适用于任何环境,提升鲁棒性。该方法是利用电容切换得到电容阵列中单个电容的误差大小,从而在正常使用状态,回补由不匹配导致的误差电压,提高ADC的线性度,同时利用桥接电容对补偿电路的电容阵列进行缩放,可以降低校准电路的面积,同时增大校准的范围。

技术研发人员:李兆江,唐鹤,陈素明

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!