一种基于超导量子比特3D晶格的超导量子处理器的制作方法

本技术涉及超导量子计算领域,尤其涉及一种基于超导量子比特3d晶格的超导量子处理器。

背景技术:

1、超导量子比特是光刻定义的超导量子电路,近年来,超导量子比特由于其操作速度快、保真度高、受材料缺陷影响较小、结构简单、可扩展性好等优势,超导量子比特芯片成为全球主要国家争相布局的前沿科技领域。

2、在相关技术中,通过单层拓扑连接的方式连接多块超导量子比特芯片,从而模块化扩展超导量子比特的数目。

3、但是,单层拓扑连接的超导量子比特只是2d平面内的超导量子比特晶格,则该量子哈密顿量也只能是一个2d晶格哈密顿量,只能模拟1d和2d量子性质,不能精确表征真实物理体系中的3d模型。

技术实现思路

1、本技术实施例提供了一种基于超导量子比特3d晶格的超导量子处理器,一是可以实现超导量子处理器中超导量子比特的3d拓展,增加超导量子比特的拓扑连接性;二是可以突破硬件对于执行量子计算的局限性,可用于执行更准确、更接近真实物理体系的量子动力学模拟。

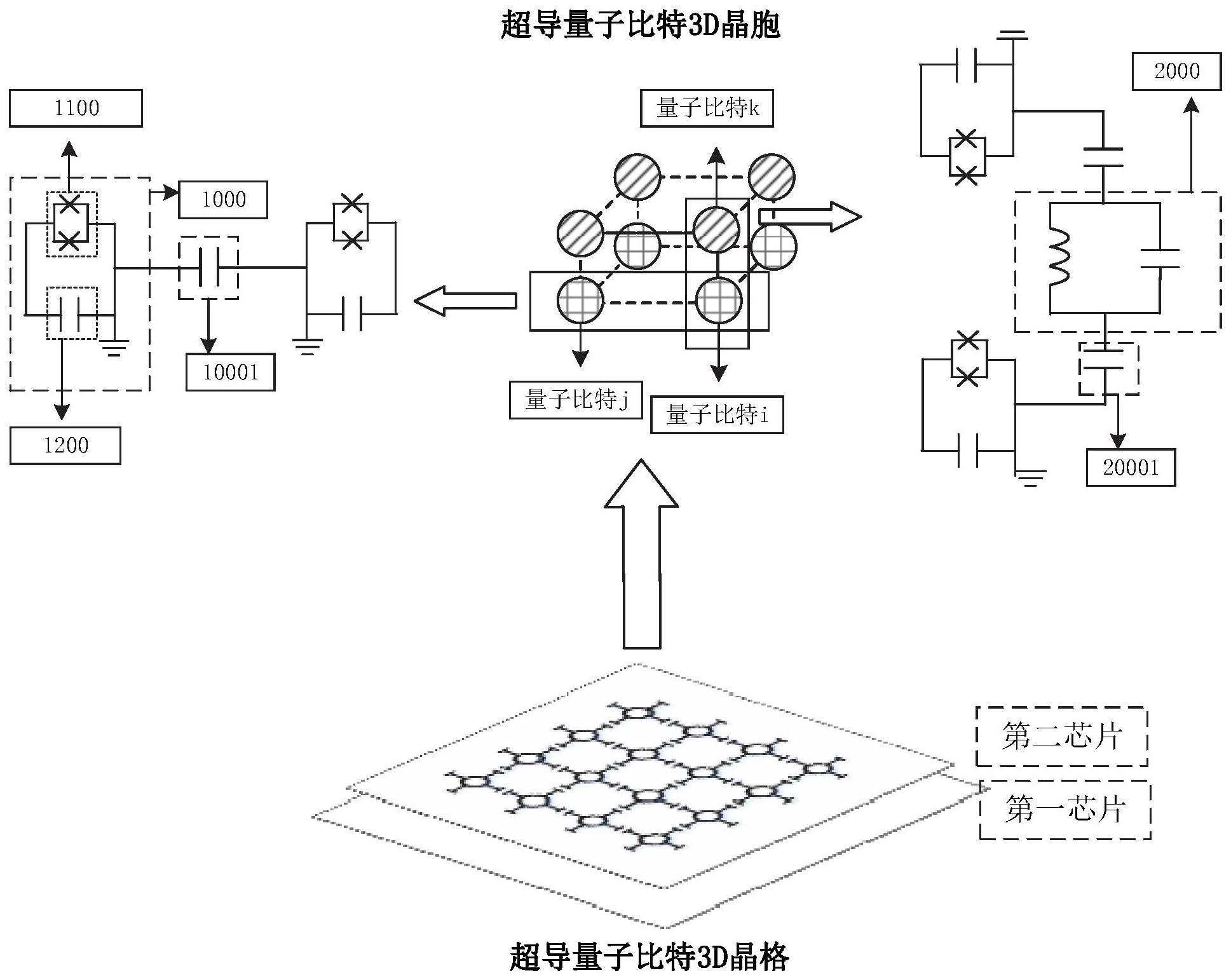

2、第一方面本技术提供了一种基于超导量子比特3d晶格的超导量子处理器,所述超导量子处理器包括两块芯片,所述两块芯片包括第一芯片和第二芯片;所述超导量子处理器中的超导量子比特具有3d晶格结构;

3、针对每一块芯片,所述芯片具有双面金属化表面,所述芯片的第一表面上图案化有超导量子比特2d晶格、铟柱阵列和寻址引线,第二表面上图案化有辅助引线,所述辅助引线与所述寻址引线通过硅通孔互联;

4、所述超导量子比特包括约瑟夫森结回路和旁路电容器,每个超导量子比特通过所述旁路电容器与近邻的超导量子比特电容耦合,在所述第一表面上,四个近邻的超导量子比特构成一个超导量子比特2d晶胞,所述超导量子比特2d晶胞沿所述第一表面扩展为所述超导量子比特2d晶格;

5、所述第一芯片的第一表面和所述第二芯片的第一表面相对,所述第一芯片上的超导量子比特2d晶格的布局与所述第二芯片上的超导量子比特2d晶格的布局相匹配,所述第一芯片上的铟柱阵列的布局与所述第二芯片上的铟柱阵列的布局相匹配,所述第一芯片和第二芯片利用倒装键合技术封装;

6、所述铟柱阵列中的铟柱用于连接所述第一芯片中的旁路电容器和所述第二芯片中的旁路电容器,所述第一芯片中的超导量子比特通过所述铟柱与所述第二芯片中的超导量子比特耦合,所述第一芯片中的超导量子比特、所述第二芯片中的超导量子比特与所述铟柱共同构成所述3d晶格结构。

7、可选地,所述旁路电容器具有共面波导结构,包括中心导体和两侧导体;

8、所述中心导体包括环形导体和四个t型导体,所述四个t型导体为沿所述环形导体的圆心向圆环外的四个角度延伸出的电容臂;所述两侧导体包括内侧导体和外侧导体,所述内侧导体为圆形导体;所述环形导体环绕所述内侧导体;

9、针对同一块芯片,所述外侧导体为接地面,是所述芯片的第一表面上的所有旁路电容器的共有结构。

10、可选地,所述内侧导体上创建有铟柱,所述铟柱与所述金属化表面之间用氮化钛焊盘隔离,所述第一芯片上的铟柱通过倒装键合与所述第二芯片上的铟柱建立电气连接。

11、可选地,经过倒装键合之后,所述铟柱的尺寸变化量符合预设的压缩率,所述压缩率的取值为40%~60%。

12、可选地,经过所述倒装键合之后,所述铟柱用于介导所述第一芯片的超导量子比特和所述第二芯片的超导量子比特之间的耦合,所述铟柱的基模频率与所述超导量子比特的工作频率之差大于所述铟柱与所述超导量子比特的耦合强度。

13、可选地,所述环形导体的宽度与第一间隙槽线宽度的比例符合预设的阻抗匹配要求,所述第一间隙槽线宽度用于表示构成所述环形导体内环和外环的间隙槽线的宽度;所述t型导体的臂长与环绕所述t型导体的间隙槽线的宽度的比例符合所述阻抗匹配要求。

14、可选地,在所述芯片的第一表面上,每个超导量子比特分别对应有三个硅通孔,所述硅通孔用于连接第一表面上的寻址引线和第二表面上的辅助引线,所述寻址引线包括z线、xy线和readout线,所述辅助引线为所述寻址引线在第二表面上的布线;

15、所述z线与超导量子比特的约瑟夫森结回路电感耦合,用于调谐超导量子比特的频率;所述xy线与超导量子比特的旁路电容器电容耦合,用于控制超导量子比特的状态旋转;所述readout线与超导量子比特的旁路电容器电容耦合,并在第二表面上与传输线电容耦合,用于测量超导量子比特的状态。

16、可选地,在以四个相邻的超导量子比特为顶点构成的矩形区域内,布设有四个硅通孔,所述四个硅通孔分别对应于所述四个相邻的超导量子比特,所述四个硅通孔均用于连接xy线或所述四个硅通孔均用于连接z线;

17、在所述矩形区域的四条边的外侧,每一侧均布设有两个硅通孔,所述两个硅通孔分别对应于距离最近的两个超导量子比特,用于连接相同功能的辅助引线;

18、针对所述矩形区域的同一外侧,若所述两个硅通孔均用于连接readout线,则所述两个硅通孔所连接的readout线一端与旁路电容器电容耦合,另一端均构成谐振器在第二表面上与同一个传输线电容耦合。

19、可选地,所述两个硅通孔所连接的readout线与所述传输线之间还设置有玻赛耳滤波器。

20、第二方面,本技术提供了一种超导量子处理器的制备方法,所述方法包括:

21、对两块相同的硅晶圆进行硅通孔制造和金属膜蒸镀,得到两块初始芯片,所述初始芯片的第一表面上覆盖有第一厚度的超导金属膜,所述初始芯片的第二表面上覆盖有第二厚度的超导金属膜,并且图案化有辅助引线;

22、利用光刻和剥离技术,图案化所述初始芯片的第一表面上的旁路电容器和寻址引线,并且利用采用双角度电子束蒸发技术,创建所述初始芯片的第一表面上的约瑟夫森结回路,得到两个独立芯片,所述两个独立芯片上的超导量子比特2d晶格的布局相匹配;

23、利用物理溅射技术,在所述两个独立芯片的第一表面上生长布局相互匹配的铟柱阵列;

24、将两块生长有所述铟柱的独立芯片的第一表面相对,结合倒装键合技术,基于所述铟柱阵列将两块独立芯片键合在一起,并进行封装得到超导量子处理器。

25、本技术实施例包括以下优点:

26、本技术实施例提供了一种基于超导量子比特3d晶格的超导量子处理器。基于超导量子比特3d晶格的超导量子处理器。所述超导量子处理器包括两块芯片;所述超导量子处理器中的超导量子比特具有3d晶格结构;针对每一块芯片,所述芯片具有双面金属化表面,所述芯片的第一表面上图案化有超导量子比特2d晶格、铟柱阵列和寻址引线;所述超导量子比特包括约瑟夫森结回路和旁路电容器,每个超导量子比特通过所述旁路电容器与近邻的超导量子比特电容耦合;两个芯片的第一表面相对设置,两个芯片中的超导量子比特2d晶格,两个芯片中的铟柱阵列的布局相匹配,所述第一芯片和第二芯片利用倒装键合技术封装;铟柱用于连接两个芯片中的旁路电容器,两个芯片中的超导量子比特通过铟柱耦合,两个芯片中的超导量子比特与铟柱构成3d晶格结构。通过上述结构,一是将多芯片架构由横向扩展到了纵向扩展,实现了超导量子比特的准3d晶格,即双层2d晶格,增加了超导量子比特的拓扑连续性;二是突破了硬件对于执行量子计算的局限性,比如使用hubbard模型模拟量子相变,本技术提出的超导量子比特3d结构接近真实的强关联体系,可能观测到奇异的量子临界行为,可用于执行更接近真实物理体系的量子动力学模拟。

- 还没有人留言评论。精彩留言会获得点赞!