一种抗辐照三模冗余锁存器

本发明涉及一种抗辐照三模冗余锁存器,属于专用集成电路抗辐照设计领域。

背景技术:

1、在恶劣的空间环境中使用电子元件会带来许多可靠性挑战,空间cmos集成电路故障的主要原因之一是辐射感应效应,可分为总剂量效应(total ionizing dose)和单粒子效应(single event effect)。先进的纳米级工艺技术对总剂量效应的耐受性更强,但随着工艺技术的提升,系统复杂性不断增加,单粒子效应导致的错误率随之增加。单粒子效应主要包括单粒子脉冲set(single event transient)与单粒子翻转seu(single eventupset)。单粒子脉冲set是当入射粒子在栅极敏感区域沉积足够电荷时,在组合栅极输出处产生的电压毛刺。这些集合可能会传播到顺序单元,并最终导致存储逻辑值的翻转,称为单粒子翻转seu。单粒子翻转seu可被分为单点翻转snu(single node upset)、双点翻转dnu(double node upset)、clk信号翻转。由于任何工艺中标准单元的设计都不能抵抗软错误,因此进行抗辐照设计,以减小单粒子效应对于集成电路的影响。

2、三模冗余技术作为常见辐照保护技术广泛的应用于工业检测、空间探测、航空航天等领域。三模冗余的原理为将需冗余保护的数据复制三份并存储到锁存器中,再将三组相同的数据送入多数表决电路进行表决输出。三模冗余以增加电路面积来换取系统稳定性。三模冗余技术常用于对于稳定性要求较高的场合下,传统三模冗余结构对于单粒子效应抵抗性较差,仅对部分snu有抵抗作用,对于dnu、以及clk信号翻转并无抵抗作用。因此有必要对三模冗余锁存器进行研究设计。

3、三模冗余锁存器可分为主级锁存器以及次级表决电路,传统三模冗余锁存器主级锁存器采用标准d锁存器,优势在于面积较小,但对单粒子效应并无抵抗作用,仅通过表决电路对锁存器进行加固。传统的表决电路为组合逻辑电路组成,组合逻辑电路极易受到set的影响。若set发生在表决电路,则直接导致三模冗余系统输出翻转出错从而使电路系统功能紊乱。若为增加表决电路的抗辐照能力,表决电路也复制三份(即全三模冗余锁存器)则至少需要82个mos管。在对面积指标要求严格的情况下根本不能接受。在原有的设计中,传统的三模冗余表决电路无抗辐照能力且极易受到set的影响,而全三模冗余表决电路则占用了大量的面积指标。因此有必要对三模冗余锁存器进行加固,提高三模冗余锁存器的可靠性。

技术实现思路

1、为了在减少面积的同时增加三模冗余表决电路的抗辐照能力,从而增加三模冗余系统可靠性,本发明提供了一种抗辐照三模冗余锁存器,所述技术方案如下:

2、本发明的第一个目的在于提供一种锁存器,包括:第一传输门101、第二传输门102、delay延时单元103、第一反相器104、第二反相器105、第三反相器106和增加泄放通路的c单元107;

3、第一传输门101的输入端为锁存器输入端,输出端与第二传输门102的输入端、delay延时单元103的输入端及增加泄放通路的c单元107相连;第一传输门101的p管控制极与n管控制极分别接时钟反信号clkn与时钟信号clk;

4、第二传输门102的输入端与第一传输门101的输出端、delay延时单元103的输入端及增加泄放通路的c单元107其中一个输入端相连;第二传输门102的输出端与第一反相器104的输出端相连;第二传输门102的p管控制极与n管控制极分别接时钟信号clk与时钟反信号clkn;

5、delay延时单元103的输入端与第一传输门101的输出端、第二传输门102的输入端相连,delay延时单元103的输出端与增加泄放通路的c单元107的另一输入端相连;

6、增加泄放通路的c单元107的输出端与第一反相器104的输入端、第二反相器105的输入端及第三反相器106的输出端相连,并作为锁存器的输出端;

7、第二反相器105的输出端与第三反相器106的输入端相连,其输入输出互连,组成保持电路。

8、可选的,增加泄放通路的c单元107的内部包括:两个pmos管和两个nmos管;在两个pmos管源漏连接处再接一个泄放pmos管漏端作为泄放通路,在两个nmos管的源漏连接处再接一个泄放nmos管漏端作为泄放通路;泄放pmos管的源端接gnd,栅端与泄放通路nmos管的栅端相连,泄放nmos管的源端接vdd。

9、可选的,针对clk信号短时间发生翻转:

10、若在clk高电平、clkn低电平时,第一传输门101关闭,第二传输门102导通,数据锁存;若单粒子效应导致clk短时间翻转为透明状态,delay延时单元103与增加泄放通路的c单元107组合,错误数据脉冲不能通过;

11、若在clk低电平、clkn高电平时,第一传输门101导通,第二传输门102关闭,数据透明;若单粒子效应导致clk短时间翻转为锁存状态,数据被错误锁存,错误数据脉冲过短,增加泄放通路的c单元107两输入端不同,错误数据不能通过。

12、可选的,针对单点翻转snu,若单粒子脉冲发生在锁存器内部,电荷通过两个泄放通路泄放。

13、可选的,针对单点翻转snu,若单粒子脉冲发生在输入端,若输入正常数据信号不影响数据输出,若输入脉宽为400ps及以下的脉冲信号则增加泄放通路的c单元107输出呈高阻态,错误翻转信号不能通过锁存器,在锁存器中被过滤掉。

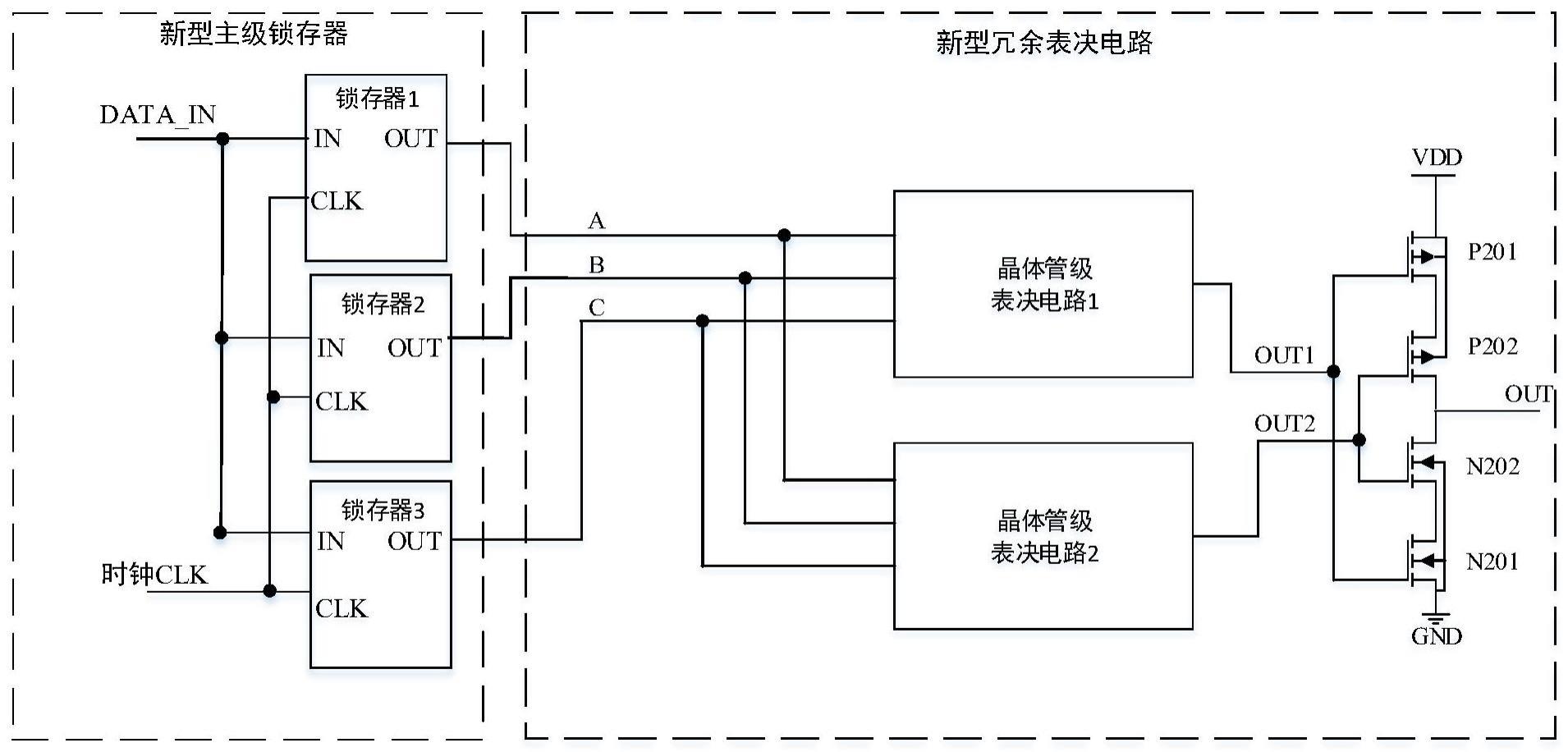

14、本发明的第二个目的在于提供一种冗余表决电路,包括:第一晶体管级表决电路、第二晶体管级表决电路和保护门电路;第一晶体管级表决电路和第二晶体管级表决电路的结构相同,两者并联,输入端接输入信号,输出端连接保护门电路;

15、第一晶体管级表决电路包括:第一pmos管201、第二pmos管202、第三pmos管203、第四pmos管204、第五pmos管205、第一nmos管206、第二nmos管207、第三nmos管208、第四nmos管209、第五nmos管210;

16、第一pmos管201、第二pmos管202、第三nmos管208与第四nmos管209的栅端作为冗余表决电路的输入端接输入信号a;第三pmos管203与第五nmos管210栅端作为冗余表决电路的输入端接输入信号b;第四pmos管204、第五pmos管205、第一nmos管206与第二nmos管207的栅端作为冗余表决电路的输入端接输入信号c;

17、第一pmos管201、第二pmos管202、第三pmos管203的源端互连至vdd,第三nmos管208、第四nmos管209、第五nmos管210的源端互连至gnd;

18、第一pmos管201源端与第四pmos管204漏端相连,第二pmos管202、第三pmos管203的源端与第五pmos管205的漏端相连,第一nmos管206源端与第三nmos管208漏端相连,第二nmos管207源端与第四nmos管209、第五nmos管210的漏端相连;

19、第四pmos管204、第五pmos管205的源端与第一nmos管206、第二nmos管207的漏端相连作为第一晶体管级表决电路的输出端out1。

20、可选的,保护门电路包括:第一mos管p201、第二mos管p202、第三mos管n201和第四mos管n202;

21、第一晶体管级表决电路的输出端out1连接至第一mos管p201和第三mos管n201栅极,第二晶体管级表决电路的输出端out2连接至第二mos管p202和第四mos管n202的栅极;

22、第二mos管p202的源极与第四mos管n202的漏端相连并作为冗余表决电路的输出out。

23、本发明的第三个目的在于提供一种抗辐照三模冗余锁存器,包括:上述任一项的锁存器,和/或上述任一项的冗余表决电路。

24、可选的,抗辐照三模冗余锁存器包括:主级锁存器和冗余表决电路;

25、主级锁存器包括:第一锁存器、第二锁存器和第三锁存器;第一锁存器、第二锁存器和第三锁存器为权利要求1-5任一项的锁存器;

26、第一锁存器、第二锁存器和第三锁存器并联,输入端均与数据输入连接,输出端与第一晶体管级表决电路、第二晶体管级表决电路连接。

27、可选的,第一锁存器的输出与第一晶体管级表决电路、第二晶体管级表决电路的第一输入端连接,第二锁存器的输出端与第一晶体管级表决电路、第二晶体管级表决电路的第二输入端连接,第三锁存器的输出端与第一晶体管级表决电路、第二晶体管级表决电路的第三输出端连接。

28、本发明有益效果是:

29、第一,本发明从电路结构对主级锁存器及表决电路进行抗辐照加固,增强主级锁存器对于snu以及dnu的抵抗性,减少表决电路自身snu对输出结果的影响,增强三模冗余系统稳定性。第二,本发明新型冗余表决电路mos管总数仅为全三模冗余表决电路mos管总数如图4所示的30%,有效的降低了三模冗余系统的面积开销,更适应于超大规模集成电路抗辐照设计。

- 还没有人留言评论。精彩留言会获得点赞!