多电源域无序开启防熔断熔丝电路的制作方法

本技术属于集成电路,尤其涉及一种多电源域无序开启防熔断熔丝电路。

背景技术:

1、随着集成电路的集成度越来越高,特征尺寸越来越小,其设计复杂性越来越高,生产改版成本也越来越高。熔丝修调技术为解决芯片生产工艺参数漂移、输出驱动变化等提供了修调方案,生产后无需改版,只要中测时实现对熔丝的一次烧录即可,节约了昂贵的mask(掩膜)改版成本,节省了改版带来的生产周期时间。

2、目前采用熔断熔丝电路实现对熔丝的一次烧录,其中熔断熔丝电路需要多电源域供电,在多电源域开启顺序随机时可能会误熔断熔丝,从而导致熔丝的熔断变得不可控。

技术实现思路

1、本技术实施例提供了一种多电源域无序开启防熔断熔丝电路,可以解决在多电源域开启顺序随机时可能会误熔断熔丝的问题。

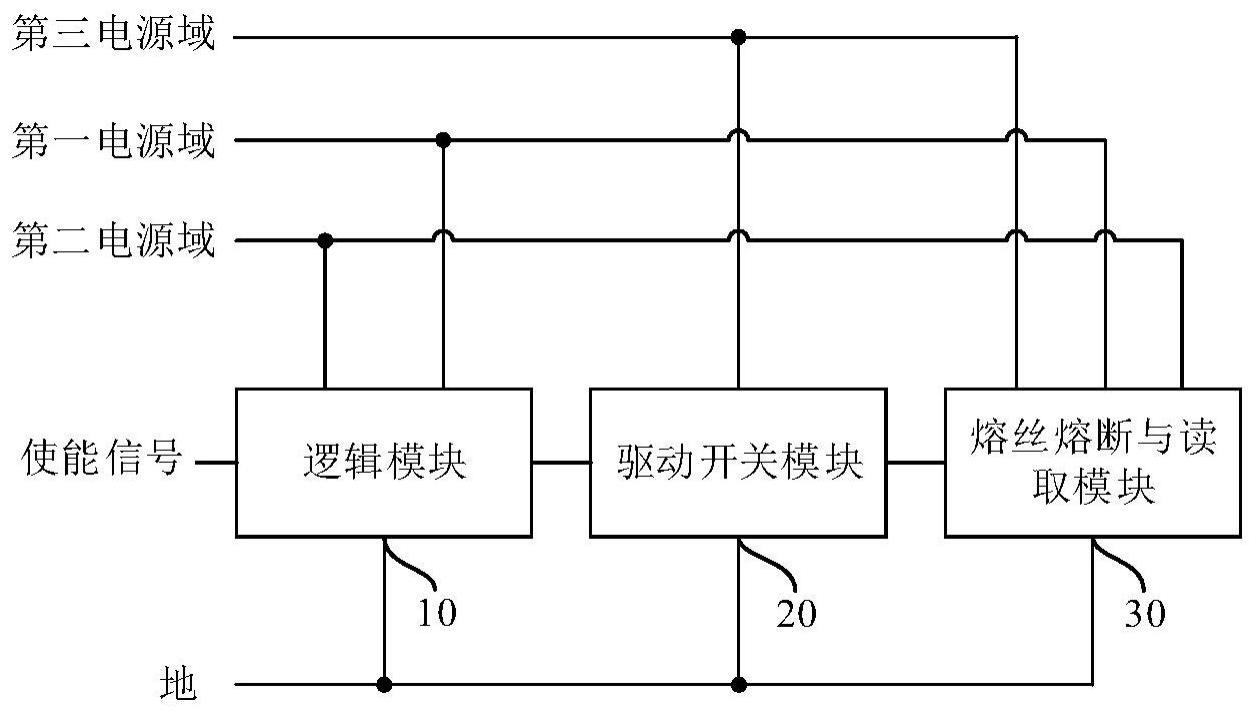

2、本技术实施例提供了一种多电源域无序开启防熔断熔丝电路,包括逻辑模块、驱动开关模块和熔丝熔断与读取模块;所述驱动开关模块分别与所述逻辑模块和所述熔丝熔断与读取模块电连接,所述逻辑模块用于与第一电源域和第二电源域电连接,所述驱动开关模块用于与第三电源域电连接,所述熔丝熔断与读取模块用于与所述第一电源域、所述第二电源域和所述第三电源域电连接,所述逻辑模块、所述驱动开关模块和所述熔丝熔断与读取模块均用于接地;

3、在所述第一电源域、所述第二电源域和所述第三电源域以任意顺序开启的过程中,所述逻辑模块用于向所述驱动开关模块输出第一逻辑信号;所述驱动开关模块用于根据所述第一逻辑信号禁止向所述熔丝熔断与读取模块发送熔断信号,其中,所述熔断信号用于指示所述熔丝熔断与读取模块熔断熔丝。

4、在一种可能的实现方式中,所述逻辑模块包括逻辑单元和下拉单元;所述下拉单元分别与所述逻辑单元和所述驱动开关模块电连接,所述逻辑单元用于与所述第一电源域和所述第二电源域电连接,所述逻辑单元和所述下拉单元均用于接地;

5、在所述第一电源域、所述第二电源域和所述第三电源域以任意顺序开启的过程中,所述逻辑单元用于在所述下拉单元的作用下输出所述第一逻辑信号。

6、在一种可能的实现方式中,所述逻辑单元包括第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第十七pmos管、第一nmos管、第二nmos管、第三nmos管、第五nmos管、第六nmos管和第五电阻;所述第一pmos管、所述第二pmos管、所述第三pmos管、所述第四pmos管和所述第五pmos管的源极和衬底均用于与所述第一电源域电连接,所述第一pmos管的栅极分别与所述第四pmos管的栅极、所述第五pmos管的漏极、所述第六nmos管的漏极和所述第二nmos管的栅极电连接,所述第一pmos管的漏极分别与所述第二pmos管的漏极、所述第三pmos管的栅极和所述第一nmos管的漏极电连接,所述第二pmos管的栅极用于接地,所述第三pmos管的漏极分别与所述第三nmos管的漏极、所述第四pmos管的漏极、所述第五pmos管的栅极、所述第六nmos管的栅极、所述下拉单元和所述驱动开关模块电连接,所述第六nmos管的源极和衬底均用于接地,所述第一nmos管的栅极分别与所述第五电阻的第一端、所述第十七pmos管的栅极和所述第五nmos管的栅极电连接,所述第一nmos管的源极与所述第二nmos管的漏极电连接,所述第三nmos管的栅极分别与所述第十七pmos管的漏极和所述第五nmos管的漏极电连接,所述第十七pmos管的源极和衬底均用于与所述第二电源域电连接,所述第五电阻的第二端、所述第一nmos管的衬底、所述第二nmos管的源极和衬底、所述第三nmos管的源极和衬底以及所述第五nmos管的源极和衬底均用于接地。

7、在一种可能的实现方式中,所述下拉单元包括第一电阻;所述第一电阻的第一端分别与所述逻辑单元和所述驱动开关模块电连接,所述第一电阻的第二端用于接地。

8、在一种可能的实现方式中,所述驱动开关模块包括第一反相器、第二反相器、第三反相器和第一开关单元;所述第二反相器分别与所述第一反相器和所述第三反相器电连接,所述第一反相器与所述逻辑模块电连接,所述第三反相器与所述第一开关单元电连接,所述第一开关单元与所述熔丝熔断与读取模块电连接,所述第一反相器、所述第二反相器、所述第三反相器和所述第一开关单元均用于与所述第三电源域电连接,所述第一反相器、所述第二反相器和所述第三反相器均用于接地;

9、在所述第一电源域、所述第二电源域和所述第三电源域以任意顺序开启的过程中,所述第一反相器、所述第二反相器和所述第三反相器依次对所述逻辑模块输出的第一逻辑信号进行反相,得到第二逻辑信号;所述第一开关单元用于根据所述第二逻辑信号禁止向所述熔丝熔断与读取模块发送熔断信号。

10、在一种可能的实现方式中,所述第一开关单元包括第九pmos管;所述第九pmos管的源极和衬底均用于与所述第三电源域电连接,所述第九pmos管的栅极与所述第三反相器电连接,所述第九pmos管的漏极与所述熔丝熔断与读取模块电连接。

11、在一种可能的实现方式中,所述熔丝熔断与读取模块包括第一滤波单元、第二滤波单元、上拉单元、第二开关单元、第三开关单元、熔丝熔断与读取单元和信号转换单元;所述第二开关单元分别与所述上拉单元、所述第三开关单元和所述第一滤波单元电连接,所述第二滤波单元与所述上拉单元电连接,所述熔丝熔断与读取单元分别与所述驱动开关模块、所述第三开关单元和所述信号转换单元电连接,所述第一滤波单元用于与所述第三电源域电连接,所述第二滤波单元和所述熔丝熔断与读取单元均用于与所述第一电源域电连接,所述信号转换单元用于与所述第二电源域电连接,所述第一滤波单元、所述第二滤波单元、所述第二开关单元、所述第三开关单元和所述信号转换单元均用于接地。

12、在一种可能的实现方式中,所述上拉单元包括第十pmos管、第十一pmos管、第十nmos管和第十一nmos管;所述第十pmos管和所述第十一pmos管的源极和衬底均与所述第二滤波单元电连接,所述第十pmos管的栅极分别与所述第十一pmos管的栅极、所述第十nmos管的漏极、所述第十一nmos管的栅极和所述第十一nmos管的漏极电连接,所述第十pmos管的漏极与所述第十nmos管的栅极电连接,所述第十nmos管和所述第十一nmos管的源极和衬底均用于接地,所述第十一pmos管的漏极分别与所述第二开关单元和所述第三开关单元电连接。

13、在一种可能的实现方式中,所述熔丝熔断与读取单元包括第十二pmos管、第十三pmos管、第十三nmos管、第十四nmos管、第四电阻、第一熔丝和第二熔丝;所述第十二pmos管和所述第十三pmos管的源极和衬底均用于与所述第一电源域电连接,所述第十二pmos管和所述第十三pmos管的栅极均用于接收偏置电压,所述第十二pmos管的漏极分别与所述第十三nmos管的漏极、所述第十三nmos管的栅极和所述第十四nmos管的栅极电连接,所述第十三pmos管的漏极分别与所述第四电阻的第一端和所述第十四nmos管的漏极电连接,所述第四电阻的第二端与所述信号转换单元电连接,所述第十三nmos的衬底和所述第十四nmos管的衬底均用于接地,所述第十三nmos管的源极与所述第一熔丝的第一端电连接,所述第十四nmos管的源极分别与所述驱动开关模块和所述第二熔丝的第一端电连接,所述第一熔丝的第二端和所述第二熔丝的第二端均与所述第三开关单元电连接。

14、在一种可能的实现方式中,所述信号转换单元包括第四反相器、第五反相器和第六反相器;所述第五反相器分别与所述第四反相器和所述第六反相器电连接,所述第四反相器与所述熔丝熔断与读取单元电连接,所述第四反相器、所述第五反相器和所述第六反相器均电连接于所述第二电源域与地之间。

15、本技术实施例与现有技术相比存在的有益效果是:

16、本技术实施例提供了一种多电源域无序开启防熔断熔丝电路,包括逻辑模块、驱动开关模块和熔丝熔断与读取模块。驱动开关模块分别与逻辑模块和熔丝熔断与读取模块电连接。其中逻辑模块用于与第一电源域和第二电源域电连接。驱动开关模块用于与第三电源域电连接。熔丝熔断与读取模块用于与第一电源域、第二电源域和第三电源域电连接。逻辑模块、驱动开关模块和熔丝熔断与读取模块均用于接地。

17、在第一电源域、第二电源域和第三电源域以任意顺序开启的过程中,逻辑模块用于向驱动开关模块输出第一逻辑信号。驱动开关模块用于根据第一逻辑信号禁止向熔丝熔断与读取模块发送熔断信号。其中,熔断信号用于指示熔丝熔断与读取模块熔断熔丝。

18、由上可知,在第一电源域、第二电源域和第三电源域以任意顺序开启的过程中,逻辑模块始终向驱动开关模块输出第一逻辑信号,驱动开关模块根据第一逻辑信号禁止向熔丝熔断与读取模块发送熔断信号,即关闭对熔丝的写操作,熔丝熔断与读取模块不会熔断熔丝。因此本技术实施例提供的多电源域无序开启防熔断熔丝电路解决了在多电源域开启顺序随机时可能会误熔断熔丝的问题,使熔丝的熔断变得可控。

- 还没有人留言评论。精彩留言会获得点赞!