一种全数字锁相环电路结构

本发明涉及一种全数字锁相环电路结构,属于半导体集成电路。

背景技术:

1、全数字锁相环因其功耗小、面积小已受到越来越多的关注,但在全数字锁相环的设计中,时间数字转换器是设计最复杂功耗最大的部分。而时间数字转换器在全数字锁相环中一般将时间/相位信号转换成数字信号并进行鉴频鉴相工作。传统的时间数字转换器基于延迟链实现,然而作为时间数字转换器的延迟单元,反相器本身提供的时间分辨率并不总能满足分辨率的要求。现有技术中提出游标型时间数字转换器,利用不同延迟链延迟单元之间的延迟差进行量化,可以将时间数字转换器的分辨率降低至最小门延迟以下,但是它受到延迟单元失配的影响更大,线性度难以保证,动态测量范围很小,由此导致全数字锁相环的锁相范围窄。而同时具有高分辨率和宽动态范围的时间数字转换器会大大增加全数字锁相环的设计复杂度和功耗。因此,寻求一种合适的全数字锁相环电路结构以降低系统功耗、提高锁相精度和扩大锁相范围是提高锁相环性能的关键。本发明拟采用一种新型环路架构,能够利用较低比特的模拟数字转换器将时间/相位信号转换成数字信号而无需高复杂度高功耗的时间数字转换器,同时有效兼顾环路的锁相范围和锁相精度。

技术实现思路

1、本发明正是针对现有技术中存在的问题,提出一种全数字锁相环电路结构,使全数字锁相环可以工作在两种模式下:当参考时钟clkref和反馈时钟clkfb的相位差较大时,时间数字转换模块的动态范围大,可变带宽数字环路滤波器的带宽变大;当参考时钟clkref和反馈时钟clkfb的相位差较小时,时间数字转换模块的分辨率高,可变带宽数字环路滤波器的带宽减小。该电路能够有效兼顾环路的锁相范围和锁相精度。

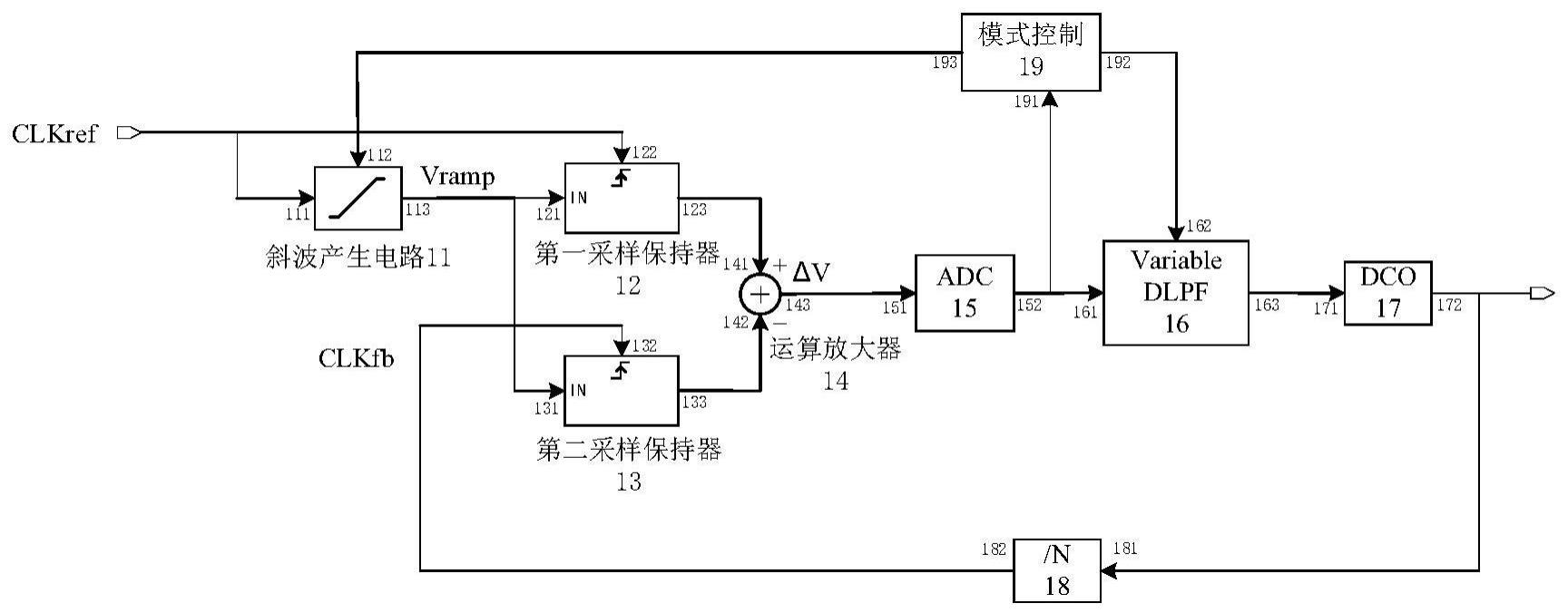

2、为了实现上述目的,本发明的技术方案如下,一种全数字锁相环电路结构,基于外部参考时钟信号clkref并根据反馈时钟信号clkfb对输出时钟的频率与相位进行控制,并为后续电路提供控制后的基准时钟信号。其特征在于:包括时间数字转换模块、模拟数字转换器adc(15))、可变带宽数字环路滤波器(16)、数控振荡器(17)、分频器(18)和模式控制模块(19)。其中时间数字转换模块同时连接可变带宽数字环路滤波器(16)和模式控制模块(19),可变带宽数字环路滤波器(16)依次连接数控振荡器(17)、分频器(18)。所述的时间数字转换模块、控制模块、数字环路滤波器、数控振荡器、分频器依次组成一个全数字锁相环;所述的时间数字转换模块对外部输入参考时钟信号和反馈时钟信号进行比较,得到两者的相位差并转换为数字量;所述控制模块根据时间数字转换模块的输出,对数字环路滤波器的带宽进行调整;所述数字环路滤波器输出控制信号,控制数控振荡器振荡频率;所述反馈时钟信号为所述全数字锁相环电路中的分频器对所述全数字锁相环电路中的数控振荡器输出的振荡信号进行分频后获得。

3、进一步的,所述时间数字转换模块包括斜波产生电路(11)、第一采样保持器(12)、第二采样保持器(13)、运算放大器(14)和模拟数字转换器adc(15)。所述参考时钟信号clkref连接斜波产生电路(11)的输入端(111)。所述斜波产生电路的输出端(113)连接第一采样保持器(12)的输入端(121)和第二采样保持器(13)的输入端(131)。所述参考时钟信号clkref和反馈时钟信号clkfb分别连接第一采样保持器(12)的上升沿采样端(122)和第二采样保持器(13)的上升沿采样端(132)。所述第一采样保持器的输出端(123)连接运算放大器的第一输入端(141)。所述第二采样保持器的输出端(133)连接运算放大器的第二输入端(142)。所述运算放大器的输出端(143)连接模拟数字转换器(15)的输入端(151)。所述模拟数字转换器的输出端(152)连接可变带宽数字环路滤波器(16)的输入端(161),同时连接模式控制模块(19)的输入端(191)。所述模式控制模块的第一输出端(192)连接可变带宽数字环路滤波器(16)的控制端(162),第二输出端(193)连接斜波产生电路(11)的控制端(112)。所述可变带宽数字环路滤波器的输出端(163)连接数控振荡器(17)的输入端(171)。所述数控振荡器的输出端(172)连接分频器(18)的输入端(181),同时作为锁相环电路的输出端,为后续电路提供基准时钟信号。所述分频器的输出端(182)作为反馈时钟信号clkfb。所述的时间数字转换模块、控制模块、数字环路滤波器、数控振荡器、分频器依次组成一个全数字锁相环,根据参考时钟clkref和反馈时钟clkfb的相位差大小工作在第一或第二锁定模式下,有利于提高锁定过程的速度和精度,降低功耗。

4、进一步的,所述斜波产生电路包括一个4倍频器、一个计数器、第一电流源i1、第二电流源i2、第三电流源i3、第四电流源i4、第一开关s1、第二开关s2、第三开关s3、第四开关s4。所述参考时钟clkref经过4倍频器后输入到计数器。所述第一电流源i1与第一开关s1相连,所述第二电流源i2与第二开关s2相连,所述第三电流源i3与第三开关s3相连,所述第四电流源i4与第四开关s4相连。所述计数器输出和模式控制模块输出一同控制四个开关s1、s2、s3、s4连接或关断,选择电流i1、i2、i3、i4中的一个或多个输出,生成斜波电压vramp。利用所述斜波电压vramp对输入外部输入参考时钟信号和反馈时钟信号进行采样,通过比较二者的电压差得到二者的相位差并转换为数字量,由此实现相位差到数字信号转换的功能,而无需高分辨率宽动态范围时间数字转换器。

5、进一步的,当参考时钟clkref和反馈时钟clkfb的相位差较大时,所述模式控制模块控制环路工作在第一锁定模式下;当参考时钟clkref和反馈时钟clkfb的相位差较小时,所述模式控制模块控制环路工作在第二锁定模式下。所述数字环路滤波器根据锁定模式自适应调整带宽,为数控振荡器提供调谐控制字,环路系统进入锁定状态。

6、进一步的,根据权利要求3所述的全数字锁相环电路结构,其特征在于,当参考时钟clkref和反馈时钟clkfb的相位差大于等于1/4个反馈时钟clkfb周期时,所述斜波电压vramp斜率由第二电流源i2控制;当参考时钟clkref和反馈时钟clkfb的相位差小于1/4个反馈时钟clkfb周期时,所述斜波电压vramp斜率由第一电流源i1和第三电流源i3同时控制。通过调节所述第一电流源i1、第二电流源i2、第三电流源i3电流的大小,可以改变所述斜波电压vramp的斜率。对输入外部输入参考时钟信号和反馈时钟信号采样后得到的电压差相同的情况下,斜波电压vramp的斜率越高,说明外部输入参考时钟信号和反馈时钟信号的相位差越小,由此可以改变所述参考时钟clkref和所述反馈时钟clkfb的相位差的测量精度。

7、相对于现有技术,本发明具有如下优点:

8、1、所述时间数字转换模块利用斜波电压对输入外部输入参考时钟信号和反馈时钟信号进行采样,通过比较二者的电压差得到二者的相位差并转换为数字量,只需低比特数的模拟数字转换器即可实现相位差到数字信号转换的功能,解决了传统的全数字锁相环电路中高分辨率宽动态范围时间数字转换器设计复杂、功耗高的问题。

9、2、所述模式控制模块根据参考时钟clkref和反馈时钟clkfb的相位差大小控制全数字锁相环的工作模式和数字环路滤波器的带宽,扩大了全数字锁相环电路的锁相范围,同时提高了全数字锁相环的锁定速度。

10、3、对全数字锁相环的电路结构进行改进与优化设计,通过调整电流源电流的大小即可调整环路相位差的测量精度。

- 还没有人留言评论。精彩留言会获得点赞!