半导体器件和包括该半导体器件的电子系统的制作方法

本公开涉及半导体器件和包括该半导体器件的电子系统,更具体地,涉及包括彼此交叠的位线的半导体器件和包括该半导体器件的电子系统。

背景技术:

1、半导体器件由于其尺寸小、多功能特性和/或制造成本低而被广泛地用在电子行业中。半导体器件可以被分类为以下中的任何一种:用于存储逻辑数据的半导体存储器件、用于处理逻辑数据的半导体逻辑器件、以及具有半导体存储器件的功能和半导体逻辑器件的功能两者的混合半导体器件。

2、由于一直要求高速度和/或低功率电子装置,因此也一直要求在其中使用的高速度和/或低电压半导体器件,并且已经需要高度集成的半导体器件来满足这些需求。然而,随着半导体器件的集成密度增加,半导体器件的电气特性和生产产量可能会劣化或降低。因此,已经不同地研究了用于提高半导体器件的电气特性和生产产量的技术。

技术实现思路

1、一个方面是提供一种具有提高的电气特性和可靠性的半导体器件和一种包括该半导体器件的电子系统。

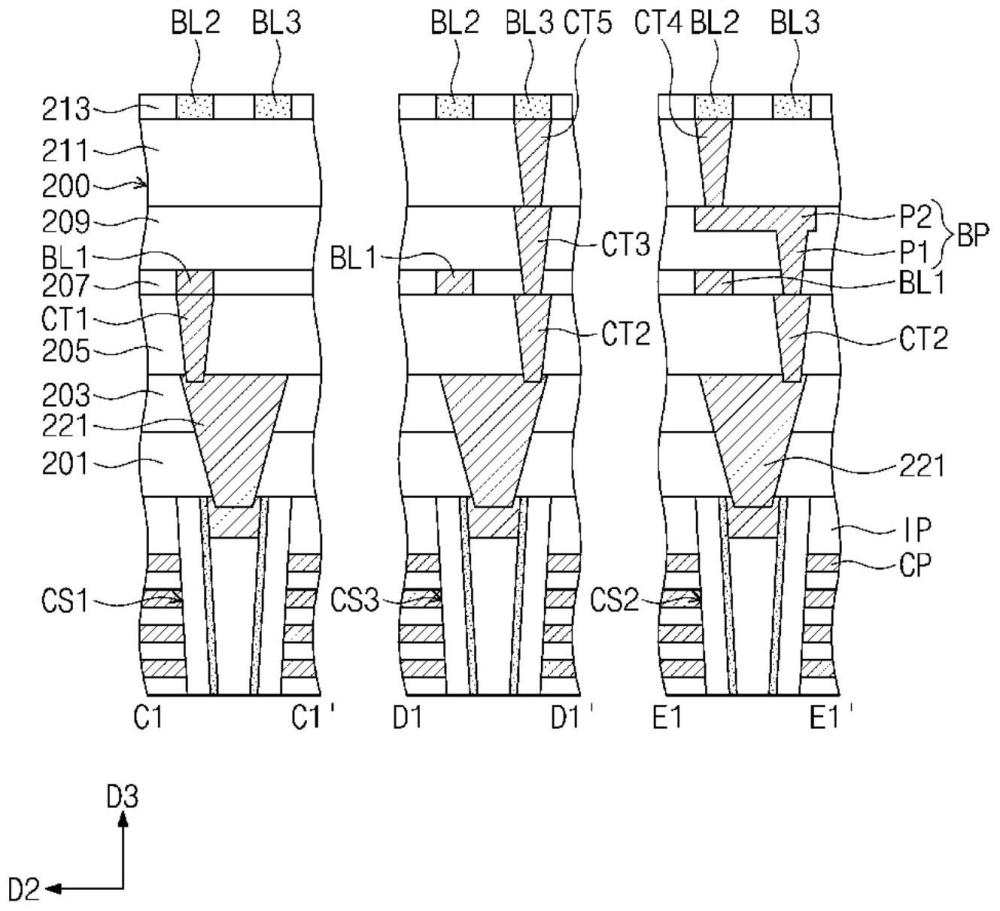

2、根据一个或更多个实施例的一个方面,一种半导体器件可以包括:栅极堆叠结构,所述栅极堆叠结构包括交替地堆叠的绝缘图案和导电图案;第一分离结构,所述第一分离结构穿透所述栅极堆叠结构;第二分离结构,所述第二分离结构穿透所述栅极堆叠结构并且与所述第一分离结构相邻;第一存储沟道结构和第二存储沟道结构,所述第一存储沟道结构和所述第二存储沟道结构穿透所述栅极堆叠结构并且设置在所述第一分离结构与所述第二分离结构之间;第一位线,所述第一位线在垂直方向上与所述第一存储沟道结构和所述第二存储沟道结构交叠并且电连接到所述第一存储沟道结构;以及第二位线,所述第二位线在所述垂直方向上与所述第一存储沟道结构、所述第二存储沟道结构和所述第一位线交叠并且电连接到所述第二存储沟道结构。

3、根据一个或更多个实施例的另一方面,一种半导体器件可以包括:栅极堆叠结构,所述栅极堆叠结构包括交替地堆叠的绝缘图案和导电图案;第一存储沟道结构和第二存储沟道结构,所述第一存储沟道结构和所述第二存储沟道结构穿透所述栅极堆叠结构;第一位线,所述第一位线在垂直方向上与所述第一存储沟道结构和所述第二存储沟道结构交叠并且电连接到所述第一存储沟道结构;第二位线,所述第二位线在所述垂直方向上与所述第一存储沟道结构和所述第二存储沟道结构交叠并且电连接到所述第二存储沟道结构;以及第一旁路结构(bypass structure),所述第一旁路结构将所述第二位线电连接到所述第二存储沟道结构。所述第一旁路结构可以包括第一部分和第二部分,所述第一部分具有第一宽度,所述第二部分具有大于所述第一宽度的第二宽度。所述第一旁路结构的所述第二部分可以在所述垂直方向上与所述第一位线交叠。

4、根据一个或更多个实施例的又一方面,一种电子系统可以包括:主板;半导体器件,所述半导体器件位于所述主板上;以及控制器,所述控制器电连接到位于所述主板上的所述半导体器件。所述半导体器件可以包括:栅极堆叠结构,所述栅极堆叠结构包括交替地堆叠的绝缘图案和导电图案;第一分离结构,所述第一分离结构穿透所述栅极堆叠结构;第二分离结构,所述第二分离结构穿透所述栅极堆叠结构并且与所述第一分离结构相邻;第一存储沟道结构、第二存储沟道结构和第三存储沟道结构,所述第一存储沟道结构、所述第二存储沟道结构和所述第三存储沟道结构穿透所述栅极堆叠结构并且设置在所述第一分离结构与所述第二分离结构之间;第一位线,所述第一位线在垂直方向上与所述第一存储沟道结构、所述第二存储沟道结构、所述第三存储沟道结构中的每一者交叠,并且电连接到所述第一存储沟道结构;第二位线,所述第二位线在所述垂直方向上与所述第一存储沟道结构、所述第二存储沟道结构、所述第三存储沟道结构和所述第一位线中的每一者交叠,并且电连接到所述第二存储沟道结构;第三位线,所述第三位线在所述垂直方向上与所述第一存储沟道结构、所述第二存储沟道结构和所述第三存储沟道结构中的每一者交叠,并且电连接到所述第三存储沟道结构;以及旁路结构,所述旁路结构将所述第二位线电连接到所述第二存储沟道结构。所述第三位线位于在与所述第二位线的水平高度相同的水平高度处。

技术特征:

1.一种半导体器件,所述半导体器件包括:

2.根据权利要求1所述的半导体器件,所述半导体器件还包括:

3.根据权利要求1所述的半导体器件,其中,所述第一位线的水平高度低于所述第二位线的水平高度。

4.根据权利要求1所述的半导体器件,所述半导体器件还包括:

5.根据权利要求4所述的半导体器件,其中,所述旁路结构的所述第二部分在所述垂直方向上与所述第一位线交叠。

6.根据权利要求4所述的半导体器件,其中,所述旁路结构的所述第一部分的至少一部分的水平高度位于与所述第一位线的水平高度相同的水平高度处。

7.根据权利要求4所述的半导体器件,其中,所述旁路结构的所述第二部分的水平高度高于所述第一位线的水平高度。

8.根据权利要求1所述的半导体器件,所述半导体器件还包括:

9.根据权利要求8所述的半导体器件,其中,所述第三位线的水平高度位于与所述第二位线的水平高度相同的水平高度处。

10.一种半导体器件,所述半导体器件包括:

11.根据权利要求10所述的半导体器件,其中,所述第一旁路结构的所述第二部分的底表面面向所述第一位线的顶表面。

12.根据权利要求10所述的半导体器件,其中,所述第一位线在所述垂直方向上与所述第二位线交叠。

13.根据权利要求10所述的半导体器件,所述半导体器件还包括:

14.根据权利要求13所述的半导体器件,所述半导体器件还包括:

15.根据权利要求14所述的半导体器件,其中,所述第二旁路结构的所述第二部分在所述垂直方向上与所述第一位线和所述第二位线交叠。

16.根据权利要求13所述的半导体器件,所述半导体器件还包括:

17.根据权利要求16所述的半导体器件,其中,所述第四位线的水平高度位于与所述第三位线的水平高度相同的水平高度处。

18.根据权利要求10所述的半导体器件,所述半导体器件还包括:

19.一种电子系统,所述电子系统包括:

20.根据权利要求19所述的电子系统,其中,所述旁路结构包括第一部分和位于所述第一部分上的第二部分,并且

技术总结

提供了一种半导体器件和包括该半导体器件的电子系统。所述半导体器件包括:栅极堆叠结构,其包括交替地堆叠的绝缘图案和导电图案;第一分离结构,其穿透所述栅极堆叠结构;第二分离结构,其穿透所述栅极堆叠结构并且与所述第一分离结构相邻;第一存储沟道结构和第二存储沟道结构,其穿透所述栅极堆叠结构并且设置在所述第一分离结构与所述第二分离结构之间;第一位线,其与所述第一存储沟道结构和所述第二存储沟道结构交叠并且电连接到所述第一存储沟道结构;以及第二位线,其与所述第一存储沟道结构、所述第二存储沟道结构以及所述第一位线交叠并且电连接到所述第二存储沟道结构。

技术研发人员:黄盛珉,李在薰,曹升铉,沈载株,李东植

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!