半导体元件及其制备方法与流程

本申请案主张美国第17/896,933号专利申请案的优先权(即优先权日为“2022年8月26日”),其内容以全文引用的方式并入本文中。本公开涉及一种半导体元件及其制备方法,尤其涉及一种包括键结结构的半导体元件。

背景技术:

1、随着电子工业的快速发展,集成电路(integrated circuits,ic)的发展已经实现了高性能化和小型化,ic材料和设计方面的技术进步产生了多代的ic,每一代都具有比上一代更小、更复杂的电路。

2、动态随机存取存储器(dynamic random access memory,dram)设备是一种随机存取存储器,它将每一位(bit)的数据存储在集成电路内的单独电容中。通常,dram以每个单元一个电容和晶体管的方形阵列排列。已经为4f2 dram单元开发了垂直晶体管,其中f代表微影的最小特征宽度或临界尺寸(critical dimension,cd)。然而,最近随着字元线间距的不断缩小,dram制造商面临着缩小存储器单元面积的巨大挑战。

3、上文的“先前技术”说明仅是提供背景技术,并未承认上文的“先前技术”说明揭示本公开的标的,不构成本公开的先前技术,且上文的“先前技术”的任何说明均不应作为本案的任一部分。

技术实现思路

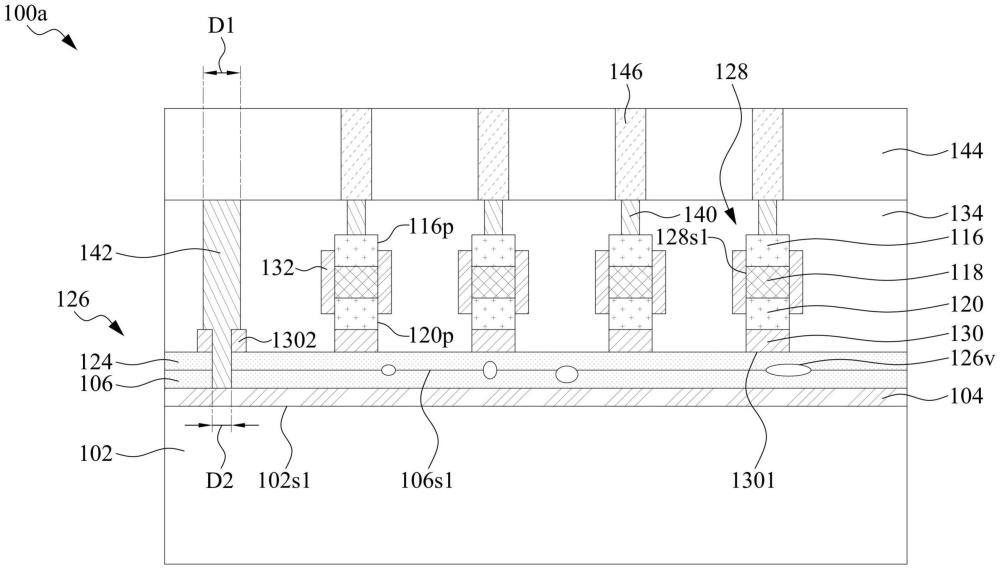

1、本公开的一个方面提供一种半导体元件,该半导体元件包括一基底、一键结结构、一位元线和一字元线。该键结结构设置于该基底上。该位元线设置于该键结结构上。该通道层设置于该位元线上。该字元线围绕该通道层。该键结结构包括一介电材料。

2、本公开的另一方面提供一种半导体元件的制备方法,该制备方法包括提供一第一基底和形成一第一介电层在该第一基底上。该制备方法还包括提供一第二基底,该第二基底包括在该第二基底上方的一金属化层。该制备方法还包括形成一第二介电层在该金属化层的上方。此外,该制备方法包括键结该第一介电层与该第二介电层以在该第一基底与该第二基底之间形成一键结结构。该制备方法还包括图案化该第二基底以在该键结结构的上方形成一堆叠结构。该制备方法还包括图案化该金属化层以在该键结结构的上方形成一位元线,以及在该堆叠结构的一侧面上形成一字元线。

3、本公开的另一方面提供一种半导体元件的制备方法。该制备方法包括提供一第一基底和形成一导电特征在该第一基底的上方。该制备方法还包括在该导电特征上形成一第一介电层。该制备方法进一步包括提供一第二基底。该第二基底包括一支撑部分和一移转部分。此外,该制备方法包括在该第二基底的该移转部分上形成一金属化层,以及在该金属化层上形成一第二介电层。该制备方法还包括键结该第一介电层和该第二介电层,以及去除该第二基底的该支撑部分。该制备方法还包括图案化该第二基底的该移转部分以形成一通道层。此外,该制备方法还包括图案化该金属化层以形成一位元线和形成围绕该通道层的一字元线。

4、本公开的实施例提供一种半导体元件及其制备方法。在两个基底的键结过程中,使用了熔接技术。熔接技术包括将形成在两个独立基底上的两个介电层进行键结。在一比较例中,两个基底通过金属与金属的键结而键结,导致在金属层之间的交界面处形成空洞,这种空洞可能使通过图案化金属层而形成的位元线不稳定,导致低产率。在本公开的实施例中,在键结的介电层之间的交界面处形成空洞,介电层中的空洞具有相对小的尺寸。此外,本公开的位元线没有空洞,与比较例相比,产率将得以获得提高。

5、上文已相当广泛地概述本公开的技术特征及优点,使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

技术特征:

1.一种半导体元件,包括:

2.如权利要求1所述的半导体元件,其中该通道层包括邻近该位元线的一第一掺杂区域与位于该第一掺杂区域上的一第二掺杂区域,其中该第一掺杂区域具有一第一导电类型,该第二掺杂区域具有不同于该第一导电类型的一第二导电类型。

3.如权利要求2所述的半导体元件,其中该通道层的该第一掺杂区域的一部分经由该字元线暴露。

4.如权利要求2所述的半导体元件,其中该通道层的该第二掺杂区域被该字元线完全覆盖。

5.如权利要求2所述的半导体元件,其中该通道层包括具有该第一导电类型的一第三掺杂区域,该第二掺杂区域设置于该第一掺杂区域与该第三掺杂区域之间。

6.如权利要求5所述的半导体元件,其中该通道层的该第三掺杂区域的一部分经由该字元线暴露。

7.如权利要求1所述的半导体元件,还包括:

8.如权利要求7所述的半导体元件,还包括:

9.如权利要求8所述的半导体元件,其中该导电插塞具有一第一孔径与不同于该第一孔径的一第二孔径。

10.如权利要求8所述的半导体元件,其中该导电插塞具有一第一高度的一第一部分与具有不同于该第一高度的一第二高度的一第二部分。

11.如权利要求10所述的半导体元件,其中该导电插塞的该第一部分通过该键结结构与该导电特征间隔开。

12.如权利要求11所述的半导体元件,其中该导电插塞的该第二部分穿透该键结结构。

13.如权利要求7所述的半导体元件,其中该位元线通过该键结结构与该导电特征间隔开。

14.如权利要求1所述的半导体元件,其中该键结结构包括一第一介电层和一第二介电层。

15.如权利要求14所述的半导体元件,其中该键结结构包括多个空洞,其位于该第一介电层与该第二介电层之间的交界面处。

16.一种半导体元件的制备方法,包括:

17.如权利要求16所述的半导体元件的制备方法,其中该第二基底包括一支撑部分和一移转部分,且该制备方法还包括在形成该键结结构之后从该移转部分移除该支撑部分。

18.如权利要求17所述的半导体元件的制备方法,其中该第二基底的该移转部分包括具有一第一导电类型的一第一掺杂区域与具有不同于该第一导电类型的一第二导电类型的一第二掺杂区域。

19.如权利要求18所述的半导体元件的制备方法,其中该第一掺杂区域的一部分经由该字元线暴露,且该第二掺杂区域被该字元线完全覆盖。

20.一种半导体元件的制备方法,包括:

技术总结

本公开提供一种半导体元件及其制备方法。该半导体元件包括一基底、一键结结构、一位元线和一字元线。该键结结构设置于该基底上。该位元线设置于该键结结构上。该通道层设置于该位元线上。该字元围绕该通道层。该键结结构包括一介电材料。

技术研发人员:罗翊仁,施江林,丘世仰

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!