高速电容隔离OOK信号调制解调电路

本发明涉及一种高速电容隔离ook信号调制解调电路,属于集成电路。

背景技术:

1、隔离传输是一种在两个相互独立的系统之间传输信号能量或者信号,同时在两个系统之间阻隔电压和电流的应用方案。实现隔离传输功能的电路叫做隔离器芯片,被广泛应用于现在的电子通信系统中。比如,隔离器可以使电气操作人员免于高压电冲击;保护在高压系统中工作的各种低压cpu或者fpga等昂贵的处理器;在工业、通信系统中断开高压和低压域之间的地环路、在电机驱动中控制高边器件等等。典型应用包括工业自动化控制、医疗电子、电机驱动、隔离总线、光伏逆变器、混合动力汽车等。

2、对于隔离器芯片的实现,长期来光耦隔离器一直被用作“默认”的信号隔离器件,但是该类隔离器具有信号延迟和非线性问题,限制了传输速度。随着近年来硅基隔离技术的发展,基于cmos工艺的数字隔离器在很多应用场合已经开始替换传统的光耦隔离器,因为尺寸更小、速度更快、功耗更低并且更加可靠。基于cmos工艺的数字隔离器主要有两种架构,电感隔离和电容隔离。电感隔离使用片上电感构成变压器进行隔离通讯,既可以传输数据也可以传输能量,但是片上电感占用的面积很大,直径一般大于200um,而且抗磁场干扰能力较弱。电容隔离使用片上电容进行隔离通讯,占用面积小,抗磁场干扰能力强,但是很难传输功率。由于隔离器芯片应用环境中的电子设备需要在强磁场、高浪涌、大噪声等非常严苛的环境中稳定的可靠的工作。在这种严苛的环境中保证要隔离器持续传输准确的数据,对隔离器电路的设计提出了很大的挑战。

3、当前市场对小面积、低功耗、高速的隔离芯片的需求日益严格。基于开关键控(ook)调制的电容隔离技术,由于具备高可靠性和小面积特性,具有非常广的应用前景。ook隔离技术中,发射机对输入信号的电平进行采样,若输入高电平则将载波传送过隔离屏障,若输入低电平则没有能量传递给接收机,接收机采用包络检波的方式对信号进行解调。这种调制方式的特点是动态功耗与信号脉宽成正相关而对信号频率不敏感;对信号电平敏感,不需要实时刷新电路;抗干扰能力较强。最新一代的ook隔离技术,其难点主要包括:用标准cmos工艺实现高达几千伏的瞬时耐压能力;输入高速信号状态下,保证信号正确的调制(编码)、解调(解码);纳秒级别的极低的传输时延;通道之间的传输时延匹配。而实现上述技术难点的关键在于ook信号调制和解调技术。

技术实现思路

1、本发明提出了一种具备低延时特性的高速电容隔离ook信号调制解调电路。

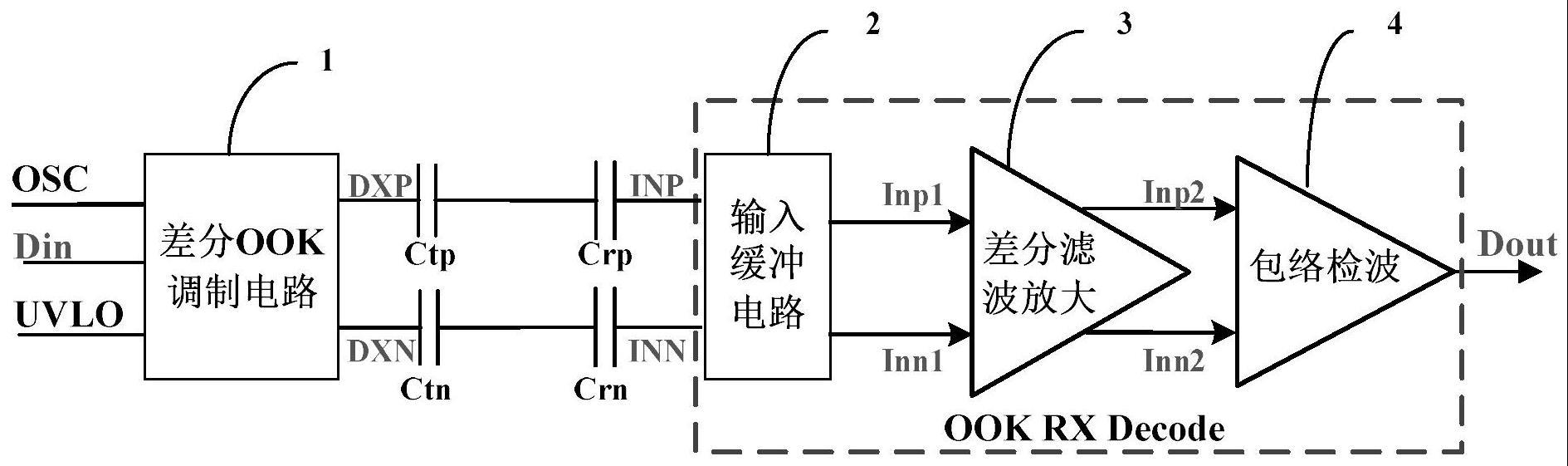

2、所述的高速电容隔离ook信号调制解调电路包括发射端的差分ook调制电路和接收端的ook接收电路,所述ook接收电路包括输入缓冲电路、差分滤波放大电路和包络检波电路,差分ook调制电路的输入端分别连接高频振荡信号osc、输入数据din、保护控制信号uvlo;差分ook调制电路输出两路信号dxp和dxn,信号dxp连接到发射端第一高压隔离电容左端,信号dxn连接到发射端第二高压隔离电容左端,发射端第一高压隔离电容右端连接接收端第一高压隔离电容左端,发射端第二高压隔离电容右端连接接收端第二高压隔离电容左端,接收端第一高压隔离电容右端连接输入缓冲电路的第一输入端inp,接收端第二高压隔离电容右端连接输入缓冲电路的第二输入端inn;inp和inn信号经过输入缓冲电路处理分别输出信号inp1和inn1,连接到差分滤波放大电路的两个输入端,差分滤波放大电路的第一输出端inp2和第二输出端inn2连接到包络检波电路的输入端,包络检波电路根据inp2和inn2信号处理得到ook输出信号dout;

3、当保护控制信号uvlo正常为高电平时,差分ook调制电路将输入数据din与高频振荡信号osc进行ook信号调制,输出信号dxp和dxn为差分高频脉冲信号,否则信号dxp和dxn输出均为低电平;在保护控制信号uvlo正常为高电平时,若输入数据din为高电平,则差分ook调制电路的输出的差分高频脉冲信号dxp和dxn将传送过高压电容隔离屏障产生inp和inn信号,若输入数据din为低电平,则差分ook调制电路输出的差分高频脉冲信号dxp和dxn均为低电平信号,无法通过高压电容隔离屏障传输信号给接收端。

4、所述发射端第一高压隔离电容、发射端第二高压隔离电容、接收端第一高压隔离电容、接收端第二高压隔离电容为耐压值及容值大小完全相同的电容。

5、具体的,所述差分ook调制电路包括:第一三输入与门、第二三输入与门,第一三输入与门的三个输入端分别连接输入数据din、保护控制信号uvlo、由nmos管m427和pmos管m428构成的传输门的输出端,nmos管m427漏极连接pmos管m428源极为传输门的输入端,连接高频振荡信号osc,nmos管m427源极连接pmos管m428漏极为传输门的输出端;第一三输入与门的输出端连接pmos管m419栅极和nmos管m420栅极,pmos管m419漏极和nmos管m420漏极相连,同时连接到pmos管m421栅极、nmos管m422栅极,pmos管m421漏极和nmos管m422漏极相连,作为信号dxp输出端;

6、第二三输入与门的三个输入端分别连接输入数据din、保护控制信号uvlo、由pmos管m409和nmos管m410构成的反相器的输出端,pmos管m409栅极连接nmos管m410栅极为反相器的输入端,连接高频振荡信号osc,pmos管m409漏极连接nmos管m410漏极为反相器的输出端;第二三输入与门的输出端连接pmos管m423栅极和nmos管m424栅极,pmos管m423漏极和nmos管m424漏极相连,同时连接到pmos管m425栅极和nmos管m426栅极,pmos管m425漏极和nmos管m426漏极相连,作为信号dxn输出端;

7、pmos管m409源极、pmos管m419源极、pmos管m421源极、pmos管m423源极、pmos管m425源极、nmos管m427栅极同时连接到电源电压vdd;nmos管m410源极、nmos管m420源极、nmos管m422源极、nmos管m424源极、nmos管m426源极、pmos管m428栅极同时连接到地电压。

8、具体的,所述第一三输入与门包括pmos管m401、pmos管m402、pmos管m403、pmos管m404、nmos管m405、nmos管m406、nmos管m407、nmos管m408,pmos管m403栅极连接nmos管m405栅极,为第一三输入与门的第一输入端,连接输入数据din;pmos管m402栅极连接nmos管m407栅极,为第一三输入与门的第二输入端,连接保护控制信号uvlo;pmos管m401栅极连接nmos管m408栅极,为第一三输入与门的第三输入端,连接传输门的输出端;pmos管m401漏极连接pmos管m402漏极、pmos管m403漏极、nmos管m405漏极、pmos管m404栅极、nmos管m406栅极,nmos管m405源极连接nmos管m407漏极,nmos管m407源极连接nmos管m408漏极,pmos管m404漏极连接nmos管m406漏极为第一三输入与门的输出端;

9、所述第二三输入与门包括pmos管m411、pmos管m412、pmos管m413、pmos管m414、nmos管m415、nmos管m416、nmos管m417、nmos管m418,pmos管m413栅极连接nmos管m415栅极,为第二三输入与门的第一输入端,连接输入数据din;pmos管m412栅极连接nmos管m417栅极,为第二三输入与门的第二输入端,连接保护控制信号uvlo;pmos管m411栅极连接nmos管m418栅极,为第二三输入与门的第三输入端,连接反相器的输出端;pmos管m411漏极连接pmos管m412漏极、pmos管m413漏极、nmos管m415漏极、pmos管m414栅极、nmos管m416栅极,nmos管m415源极连接nmos管m417漏极,nmos管m417源极连接nmos管m418漏极,pmos管m414漏极连接nmos管m416漏极为第二三输入与门的输出端;

10、pmos管m401源极、pmos管m402源极、pmos管m403源极、pmos管m404源极、pmos管m411源极、pmos管m412源极、pmos管m413源极、pmos管m414源极同时连接到电源电压vdd,nmos管m406源极、nmos管m408源极、nmos管m416源极、nmos管m418源极同时连接到地电压。

11、具体的,所述输入缓冲电路包括:pmos管m501、pmos管m502、pmos管m503、pmos管m504、pmos管m505、pmos管m506、pmos管m507、pmos管m508、pmos管m509、pmos管m510、pmos管m511、pmos管m512、pmos管m513、pmos管m514、电阻r51、电阻r52、电阻r53、电阻r54、电阻r55、电阻r56、电容c51和电容c52;

12、其中,pmos管m501栅极和pmos管m508栅极连接偏置电压vb51,pmos管m502栅极和pmos管m509栅极连接偏置电压vb52;pmos管m501漏极连接pmos管m502源极,pmos管m502漏极连接电阻r51上端、pmos管m503栅极和pmos管m514栅极;电阻r51下端连接pmos管m503源极、pmos管m504栅极、pmos管m505栅极、pmos管m513栅极;pmos管m503漏极连接pmos管m504源极,pmos管m504漏极连接pmos管m505源极;pmos管m505漏极连接电阻r53上端、pmos管m506漏极,作为输入缓冲电路的第一输入端inp;电阻r53下端连接电阻r54上端;pmos管m506源极连接pmos管m507漏极、电容c51上端;pmos管m507源极作为信号inp1的输出端;pmos管m508漏极连接pmos管m509源极,pmos管m509漏极连接电阻r52上端、pmos管m507栅极和pmos管m510栅极;电阻r52下端连接到pmos管m510源极、pmos管m511栅极、pmos管m512栅极和pmos管m506栅极;pmos管m510漏极连接pmos管m511源极,pmos管m511漏极连接pmos管m512源极,pmos管m512漏极连接到电阻r55上端、pmos管m513漏极,作为输入缓冲电路的第二输入端inn;pmos管m513源极连接pmos管m514漏极、电容c52上端;pmos管m514源极作为信号inn1的输出端;pmos管m501源极和pmos管m508源极连接电源电压vcc;电阻r54下端、电阻r56下端、电容c51下端、电容c52的下端连接地电压;

13、所述pmos管m508、pmos管m509、电阻r52、pmos管m510、pmos管m511、pmos管m512、电阻r55和电阻r56构成一个偏置信号产生电路,根据偏置电压vb51和偏置电压vb52信号及输入信号inn产生pmos管m507栅极和pmos管m506栅极各自需要的内部偏置信号;所述pmos管m501、pmos管m502、电阻r51、pmos管m503、pmos管m504、pmos管m505、电阻r53和电阻r53构成一个偏置信号产生电路,根据偏置电压vb51和偏置电压vb52信号及输入信号inp产生pmos管m513栅极和pmos管m514栅极各自需要的内部偏置信号。

14、具体的,所述差分滤波放大电路包括:pmos管m601、pmos管m602、pmos管m603、pmos管m604和nmos管m606、nmos管m607、nmos管m608,电容c61、电容c62、电容c63、电容c64、电容c65、电容c66、电容c67、电容c68,电阻r61、电阻r62、电阻r63、电阻r64、电阻r65、电阻r66、电阻r67、电阻r68、电阻r69、电阻r610、电阻r611、电阻r612和电流源ib61、电流源ib62;

15、其中,pmos管m601栅极连接c61下端和电阻r61上端,电阻r61下端连接pmos管m601漏极以及电阻r69上端;pmos管m602栅极连接c62下端和电阻r62上端,电阻r62下端连接pmos管m602漏极以及电阻r65上端;电阻r65下端连接电容c65右端、nmos管m605漏极、nmos管m606漏极;电容c65左端连接电阻r67左端,作为差分滤波放大电路的第二输出端inn2;电阻r67右端连接电容c67左端,电容c67右端连接nmos管m607栅极、nmos管m608栅极、电阻r610下端,作为信号inn1的输入端;pmos管m603栅极连接电容c63下端和电阻r63上端,电阻r63下端连接pmos管m603漏极和电阻r66上端;电阻r66下端连接电容c66左端、nmos管m607漏极、nmos管m608漏极;电容c66右端连接电阻r68右端,作为差分滤波放大电路的第一输出端inp2;电阻r68左端连接电容c68右端,电容c68左端连接nmos管m606栅极、nmos管m605栅极、电阻r69下端,作为信号inp1的输入端;pmos管m604栅极连接c64下端和电阻r64上端,电阻r64下端连接pmos管m604漏极和电阻r610上端;nmos管m605源极和nmos管m607源极共同连接电流源ib61的正极;nmos管m606源极接电阻r611上端,nmos管m608源极连接电阻r612上端,电阻r611下端和r612下端共同连接电流源ib62的正极,电流源ib61和电流源ib62的负极接地;电容c61上端、c62上端、c63上端、c64上端和pmos管m601源极、pmos管m602源极、pmos管m603源极、pmos管m604源极均连接电源电压vcc;

16、所述电流源ib61、nmos管m605、nmos管m607、nmos管pmos管m602、pmos管m603、电阻r62、电阻r63、电阻r65、电阻r66、电容c62和电容c63构成一个基本的差分运算放大器;电流源ib62、电阻r611、电阻r612、nmos管m606和nmos管m608构成上述基本的差分运算放大器的共模输出调整电路;pmos管m601、电容c61、电阻r61和电阻r69构成一个输入保护电路,pmos管m604、电容c64、电阻r64和电阻r610构成另一个输入保护电路;电容c65、电容c66、电容c67、电容c68、电阻r67和电阻r68构成一个交叉耦合的高频滤波网络。

17、具体的,所述包络检波电路包括:pmos管m701、pmos管m702、pmos管m703、pmos管m704、pmos管m708、pmos管m709、pmos管m712、pmos管m714、pmos管m716、pmos管m717、pmos管m720、pmos管m721、nmos管m705、nmos管m706、nmos管m707、nmos管m710、nmos管m711、nmos管m713、nmos管m715、nmos管m718、nmos管m719、nmos管m722、nmos管m723,以及电流源ib71、电阻r71、电容c71;

18、其中,m701栅极连接m702栅极、m703漏极、m705漏极和m706漏极,m705栅极作为信号inp2的输入端,m706栅极作为信号inn2的输入端,m705源极、m706源极和m707源极共同连接到电流源ib71的正极;m701漏极连接m703源极,m703栅极连接m704栅极,m702漏极连接m704源极,m704漏极连接m707漏极、m709栅极、m710栅极、电阻r71左端和电容c71左端;m707栅极连接参考阈值电压vdet1;m708栅极连接m711的栅极,同时作为控制信号ctr1的输入端;m709漏极连接m708漏极、m710漏极、电阻r71右端、电容c71右端、m712栅极和m713栅极;m710源极和m711漏极相连;m712漏极连接、m713漏极、m714栅极和m715栅极;m714漏极连接m715漏极、m717栅极和m719栅极;m716栅极连接m718栅极、m720栅极和m722栅极,并作为控制信号ctr2的输入端;m716漏极和m717源极相连;m717漏极连接m718漏极、m719漏极、m721栅极和m723栅极;m720漏极连接m721源极,m721漏极连接m722漏极、m723漏极,作为ook输出信号dout的输出端;pmos管m701源极、m702源极、m708源极、m709源极、m712源极、m714源极、m716源极和m720源极均连接到电源电压vcc;nmos管m711源极、m713源极、m715源极、m718源极、m719源极、m722源极、m723源极和电流源ib71负极均连接到地电压;

19、所述电流源ib71、pmos管m701、pmos管m702、pmos管m703、pmos管m704、pmos管m708、pmos管m709、nmos管m705、nmos管m706、nmos管m707、nmos管m710、nmos管m711、电阻r71和电容c71构成一个两级全波探测器,其中,电流源ib71、pmos管m701、pmos管m702、pmos管m703、pmos管m704、nmos管m705、nmos管m706、nmos管m707为第一级电路,pmos管m708、pmos管m709、nmos管m710、nmos管m711、电阻r71和电容c71为第二级电路;pmos管m712、pmos管m714、nmos管m713和nmos管m715构成一个数字整形电路;pmos管m716、pmos管m717、pmos管m720、pmos管m721、nmos管m718、nmos管m719、nmos管m722和nmos管m723构成一个带控制功能的输出缓冲器。

20、本发明的优点是:所述高速电容隔离ook信号调制解调电路中,ook接收电路采用了具有高频滤波功能的多级放大电路,一方面将高频干扰信号进行抑制,另外一方面实现ook高频信号的高增益,从而提高ook接收电路的识别速度。此外,为提高信号调制解调链路的抗共模干扰能力,差分ook调制电路和ook接收电路的高频信号通路设计全部采用全差分架构,以达到最佳的共模抑制能力。

- 还没有人留言评论。精彩留言会获得点赞!