约瑟夫森结的制造方法以及量子芯片与流程

本发明涉及量子芯片制造,特别是涉及一种约瑟夫森结的制造方法以及量子芯片。

背景技术:

1、约瑟夫森结是量子芯片的核心结构,其稳定性对量子芯片的性能至关重要。量子芯片在储存过程中,随着储存时间的增加,约瑟夫森结会出现电阻老化的现象,即电阻会逐渐变大,这会造成量子芯片的性能失效。

2、由于约瑟夫森结的势垒层是非晶alox,内部存在诸多缺陷,在吸附、结合除氧以外的元素后,如羟基等,导致化学组成改变,从而造成电阻老化。

3、为了改善约瑟夫森结电阻老化的问题,目前通常使用退火的方式来改善势垒层的特性。但该方式存在缺陷,退火后,由于量子芯片的基片与铝的热膨胀系数不匹配,铝膜表面会出现丘点,这会对量子芯片整体产生一定的负面影响,因此约瑟夫森结电阻老化改善效果不理想。

技术实现思路

1、本发明的目的是提供一种约瑟夫森结的制造方法以及量子芯片,以解决现有技术中约瑟夫森结电阻老化改善效果不理想的问题,能够避免约瑟夫森结电阻老化,且不影响量子芯片的性能。

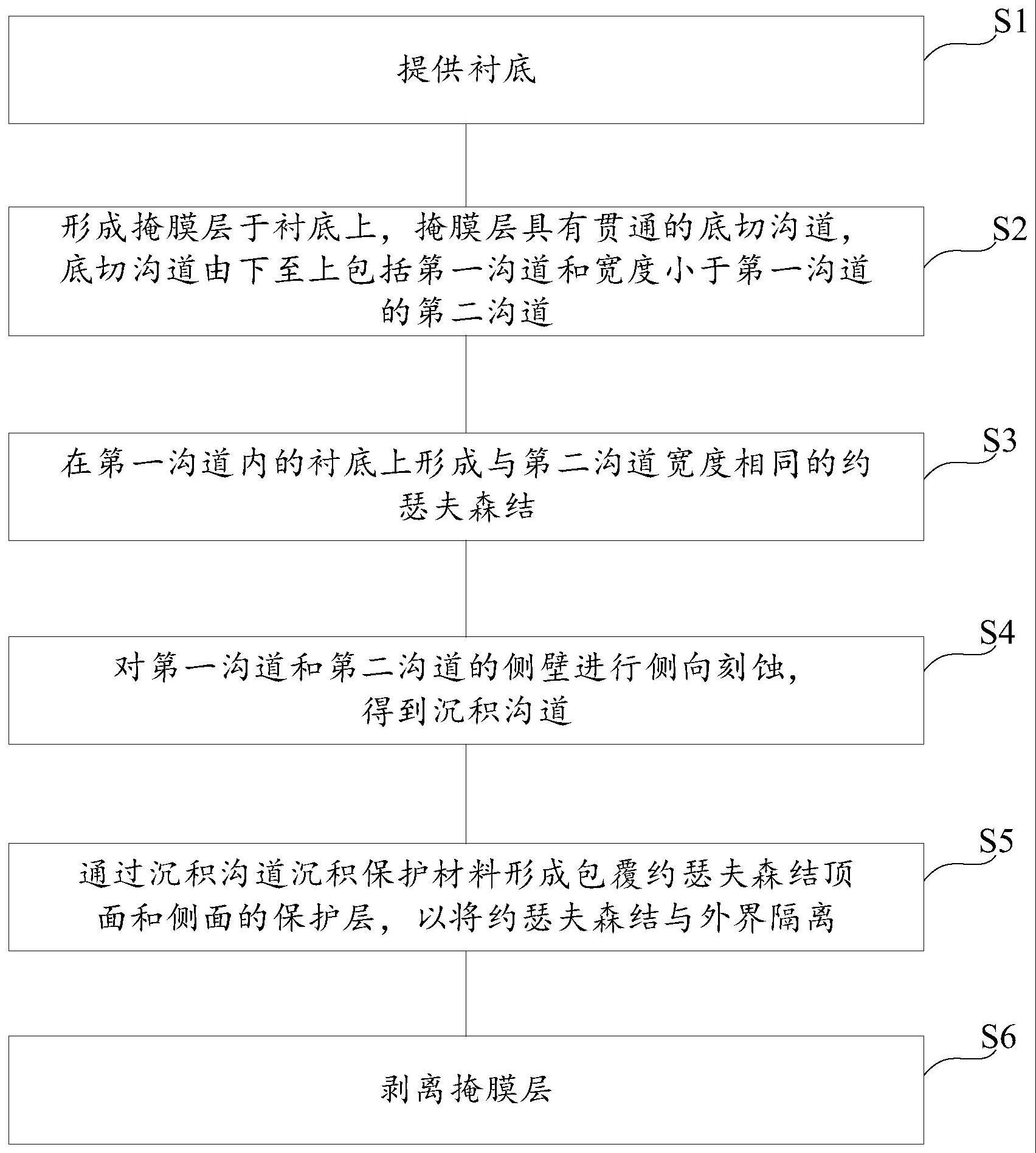

2、为解决上述技术问题,本发明提供一种约瑟夫森结的制造方法,包括:

3、提供衬底;

4、形成掩膜层于所述衬底上,所述掩膜层具有贯通的底切沟道,所述底切沟道由下至上包括第一沟道和宽度小于所述第一沟道的第二沟道;

5、在所述第一沟道内的衬底上形成与所述第二沟道宽度相同的约瑟夫森结;

6、对所述第一沟道和第二沟道的侧壁进行侧向刻蚀,得到沉积沟道;

7、通过所述沉积沟道沉积保护材料形成包覆所述约瑟夫森结顶面和侧面的保护层,以将所述约瑟夫森结与外界隔离。

8、优选的,所述掩膜层为两层光刻胶,所述第一沟道形成于下层的光刻胶,所述第二沟道形成于上层的光刻胶。

9、优选的,所述上层的光刻胶的厚度大于所述下层的光刻胶的厚度。

10、优选的,所述侧向刻蚀采用的刻蚀工艺为等离子体刻蚀工艺或反应性离子刻蚀工艺。

11、优选的,所述保护材料为α-si、sinx或bn。

12、优选的,所述保护材料为α-si时,所述保护层采用等离子体增强化学气相沉积工艺形成。

13、优选的,所述保护材料为sinx时,所述保护层采用化学气相沉积工艺形成。

14、优选的,所述保护材料为bn时,所述保护层采用磁控溅射工艺形成。

15、优选的,所述制造方法还包括:剥离所述掩膜层。

16、为解决上述技术问题,本发明还提供一种量子芯片,包括根据前述任一项所述的约瑟夫森结的制造方法得到的约瑟夫森结。

17、区别于现有技术的情况,本发明提供的约瑟夫森结的制造方法利用掩膜层中的底切沟道形成约瑟夫森结,再对底切沟道的侧壁进行侧向刻蚀,得到沉积沟道,通过沉积沟道沉积保护材料形成包覆约瑟夫森结顶面和侧面的保护层,由于保护层将约瑟夫森结完全包覆,使约瑟夫森结与外界隔离,无需对约瑟夫森结进行额外的工艺处理,例如退火工艺等,从而能够避免约瑟夫森结电阻老化,且不影响量子芯片的性能。

18、本发明提供的量子芯片包括根据前述约瑟夫森结的制造方法得到的约瑟夫森结,具有相同的技术效果,此处不再赘述。

技术特征:

1.一种约瑟夫森结的制造方法,其特征在于,包括:

2.根据权利要求1所述的制造方法,其特征在于,所述掩膜层为两层光刻胶,所述第一沟道形成于下层的光刻胶,所述第二沟道形成于上层的光刻胶。

3.根据权利要求2所述的制造方法,其特征在于,所述上层的光刻胶的厚度大于所述下层的光刻胶的厚度。

4.根据权利要求1所述的制造方法,其特征在于,所述侧向刻蚀采用的刻蚀工艺为等离子体刻蚀工艺或反应性离子刻蚀工艺。

5.根据权利要求1所述的制造方法,其特征在于,所述保护材料为α-si、sinx或bn。

6.根据权利要求5所述的制造方法,其特征在于,所述保护材料为α-si时,所述保护层采用等离子体增强化学气相沉积工艺形成。

7.根据权利要求5所述的制造方法,其特征在于,所述保护材料为sinx时,所述保护层采用化学气相沉积工艺形成。

8.根据权利要求5所述的制造方法,其特征在于,所述保护材料为bn时,所述保护层采用磁控溅射工艺形成。

9.根据权利要求1所述的制造方法,其特征在于,所述制造方法还包括:

10.一种量子芯片,其特征在于,包括根据权利要求1至9任一项所述的约瑟夫森结的制造方法得到的约瑟夫森结。

技术总结

本发明公开了一种约瑟夫森结的制造方法以及量子芯片。该制造方法包括:提供衬底;形成掩膜层于衬底上,掩膜层具有贯通的底切沟道,底切沟道由下至上包括第一沟道和宽度小于第一沟道的第二沟道;在第一沟道内的衬底上形成与第二沟道宽度相同的约瑟夫森结;对第一沟道和第二沟道的侧壁进行侧向刻蚀,得到沉积沟道;通过沉积沟道沉积保护材料形成包覆约瑟夫森结顶面和侧面的保护层,以将约瑟夫森结与外界隔离。通过上述方式,本发明能够避免约瑟夫森结电阻老化,且不影响量子芯片的性能。

技术研发人员:请求不公布姓名,请求不公布姓名,请求不公布姓名,张辉

受保护的技术使用者:本源量子计算科技(合肥)股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!