三维铁电存储器件的制作方法

本公开涉及三维(3d)铁电存储器件。

背景技术:

1、根据相关技术的硬盘已被固态驱动器(ssd)取代,因此,作为非易失性存储器件的nand闪速存储器件已商业化。近来,由于紧凑尺寸和高集成的趋势,已经开发了具有在垂直方向上堆叠在衬底上的多个存储单元的三维(3d)nand闪速存储器件。

2、此外,目前正在进行将具有低操作电压和高编程速率的铁电场效应晶体管(fefet)应用于三维nand闪速存储器件的研究。

技术实现思路

1、提供了三维(3d)铁电存储器件。

2、另外的方面将部分地在以下描述中阐述,并将部分地自该描述明显,或者可以通过实践本公开的呈现的实施方式而获知。

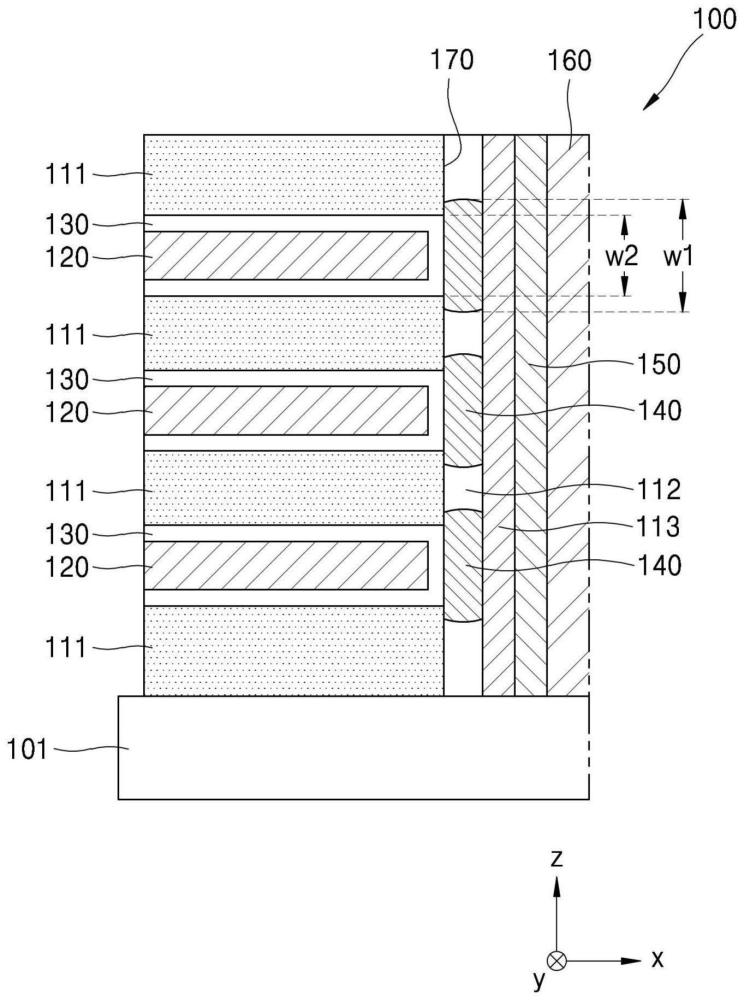

3、根据实施方式,一种3d铁电存储器件可以包括衬底、堆叠在衬底上的多个栅电极、与所述多个栅电极接触的多个铁电层、与所述多个铁电层接触的多个中间电极、与所述多个中间电极接触的栅极绝缘层、以及与栅极绝缘层接触的沟道层。所述多个中间电极中的每个的宽度可以大于所述多个铁电层中的每个与所述多个中间电极中的相应一个接触的宽度。

4、在一些实施方式中,所述多个栅电极可以在垂直于衬底的表面的方向上堆叠,所述多个栅电极中的每个可以在平行于衬底的表面的方向上延伸。

5、在一些实施方式中,所述多个铁电层可以分别在所述多个栅电极的上表面和所述多个栅电极的下表面上。所述多个栅电极的上表面和所述多个栅电极的下表面可以平行于衬底的表面。所述多个栅电极中的每个可以包括彼此不同的第一侧表面和第二侧表面。所述多个铁电层可以在所述多个栅电极的第一侧表面上,第一侧表面可以垂直于衬底的表面。

6、在一些实施方式中,所述多个铁电层中的每个与所述多个中间电极中的相应一个接触的面积可以小于所述栅极绝缘层与所述多个中间电极中的每个接触的面积。

7、在一些实施方式中,所述多个中间电极中的每个的宽度可以是所述多个铁电层中的每个与所述多个中间电极中的相应一个接触的宽度的约1.2倍至约5倍。

8、在一些实施方式中,所述多个中间电极中的每个的宽度可以是约15nm至约100nm。

9、在一些实施方式中,所述多个栅电极中的每个和所述多个中间电极中的每个可以独立地包括w、tin、tan、wn、nbn、mo、ru、ir、ruo、iro和多晶硅中的至少一种。

10、在一些实施方式中,3d铁电存储器件可以进一步包括在所述多个栅电极之间的多个第一绝缘层。

11、在一些实施方式中,所述多个第一绝缘层可以包括sio、sioc和sion中的至少一种。

12、在一些实施方式中,所述多个第一绝缘层中的每个可以具有约7nm至约100nm的厚度。

13、在一些实施方式中,所述多个铁电层可以包括基于萤石的材料、基于氮化物的材料或钙钛矿。

14、在一些实施方式中,所述多个铁电层中的每个可以具有约3nm至约20nm的厚度。

15、在一些实施方式中,3d铁电存储器件可以进一步包括在所述多个中间电极之间的多个第二绝缘层。

16、在一些实施方式中,所述多个第二绝缘层的绝缘材料和所述多个第一绝缘层的绝缘材料可以彼此不同。所述多个第二绝缘层可以包括sin。

17、在一些实施方式中,所述多个第二绝缘层中的每个的宽度可以是约5nm至约20nm。

18、在一些实施方式中,栅极绝缘层可以包括sio、sin、alo、hfo和zro中的至少一种。

19、在一些实施方式中,沟道层可以被公共地提供以对应于所述多个栅电极。

20、在一些实施方式中,沟道层可以在垂直于衬底的方向上延伸。

21、在一些实施方式中,沟道层可以包括iv族半导体、iii-v族半导体、氧化物半导体、氮化物半导体、氮氧化物半导体、二维(2d)半导体材料、量子点或有机半导体。

22、根据实施方式,可以提供一种包括上述3d铁电存储器件的电子器件。

23、根据实施方式,一种制造3d铁电存储器件的方法可以包括:在垂直于衬底的表面的方向上交替地堆叠多个第一绝缘层和多个牺牲层;垂直地形成沟道孔以穿过第一绝缘层和牺牲层;在沟道孔的内壁上依次沉积绝缘材料层、第二绝缘层、第三绝缘层和沟道层;去除所述多个牺牲层,然后通过蚀刻绝缘材料层而暴露第二绝缘层;通过蚀刻暴露的第二绝缘层,形成在垂直于衬底的表面的方向上延伸的多个凹陷;形成多个中间电极以填充所述多个凹陷;在通过去除所述多个牺牲层而获得的空间的内壁上沉积多个铁电层;以及在所述多个铁电层的内侧部分中形成多个栅电极。

24、在一些实施方式中,该方法可以进一步包括,在沟道孔的内壁上形成沟道层之后,形成氧化物层以填充沟道孔的内部。

25、在一些实施方式中,中间电极在垂直于衬底的方向上的宽度可以大于铁电层与中间电极接触的宽度。

26、在一些实施方式中,中间电极在垂直于衬底的方向上的宽度可以是铁电层与中间电极接触的宽度的约1.2倍至约5倍。

27、在一些实施方式中,第一绝缘层可以包括sio、sioc和sion中的至少一种。

28、在一些实施方式中,牺牲层可以包括sin。

29、在一些实施方式中,绝缘材料层可以包括sio、sioc和sion中的至少一种。

30、在一些实施方式中,第二绝缘层可以包括sin。

31、在一些实施方式中,第三绝缘层可以包括sio、sin、alo、hfo和zro中的至少一种。

32、在一些实施方式中,沟道层可以包括iv族半导体、iii-v族半导体、氧化物半导体、氮化物半导体、氮氧化物半导体、2d半导体材料、量子点或有机半导体。

33、在一些实施方式中,铁电层可以包括基于萤石的材料、基于氮化物的材料或钙钛矿。

34、在一些实施方式中,所述多个栅电极中的每个和所述多个中间电极中的每个可以独立地包括w、tin、tan、wn、nbn、mo、ru、ir、ruo、iro和多晶硅中的至少一种。

35、根据实施方式,一种3d铁电存储器件可以包括:衬底;多个栅电极,在衬底的表面上并在第一方向上彼此间隔开,第一方向垂直于衬底的表面;沟道层,在衬底的表面上并在第一方向上延伸;多个中间电极,在衬底的表面上彼此间隔开,所述多个中间电极在沟道层和所述多个栅电极之间;栅极绝缘层,在所述多个中间电极和沟道层之间;以及多个铁电层,分别在所述多个栅电极上并接触所述多个中间电极。所述多个铁电层可以在所述多个栅电极和所述多个中间电极之间。所述多个铁电层可以在第一方向上彼此间隔得比所述多个中间电极在第一方向上彼此间隔得远。

36、在一些实施方式中,所述多个栅电极中的每个和所述多个中间电极中的每个可以独立地包括w、tin、tan、wn、nbn、mo、ru、ir、ruo、iro和多晶硅中的至少一种。

37、在一些实施方式中,所述多个铁电层可以包括基于萤石的材料、基于氮化物的材料或钙钛矿。

38、在一些实施方式中,所述多个铁电层中的每个可以具有约3nm至约20nm的厚度。

39、在一些实施方式中,3d铁电存储器件可以进一步包括在所述多个中间电极之间的多个第二绝缘层。

- 还没有人留言评论。精彩留言会获得点赞!