一种具有抗瞬变干扰的隔离电路的制作方法

本发明涉及不同电压域之间进行信号传输系统中的隔离电路,尤其涉及一种具有抗瞬变干扰的隔离电路,属于集成电路。

背景技术:

1、隔离电路是应用在不同电压域之间进行信号传输的系统中,比如信号从低压域向高压域传输,或者信号从高压域向低压域传输。目前主要有光耦隔离、电感隔离、电容隔离等隔离方式,其中电容隔离由于具有传输延迟低、功耗小的优势,被广泛研究和应用。

2、一种传统电容隔离电路结构如图1所示,其工作波形如图3所示。信号从第一电压域(vdda/gnda)向第二电压域(vddb/gndb)传输,输入in信号被调制为一定频率的方波信号a,经过电容c1后变为脉冲型信号b,b经过信号解调电路后恢复为与in相同的信号波形,当两电压域之间的压差变化(瞬变干扰)时,b信号的中心值也会产生偏移,当gndb-gnda上升时,由于电容上的位移电流是从b流向a,因此b信号中心值向下偏移,当gndb-gnda下降时,位移电流从a流向b,b信号中心值向上偏移,且偏移量与gndb-gnda电压变化率(dv/dt)成正相关,因此当dv/dt绝对值较大时,b信号波形会接近电源vddb或地gndb。b信号中心值产生偏移时,会严重干扰信号解调电路的正常工作,从而导致输出出现逻辑紊乱。

3、为了提升电容隔离电路的抗dv/dt能力,信号调制和解调采用双通道传输方式,如图2所示,其工作波形如图4所示。调制信号a1和a2是反相的方波信号,b1和b2也是反相的脉冲信号,信号解调电路采用b1和b2的差值进行处理,这样会大大增强抗dv/dt能力。但是该结构的抗dv/dt能力会有一定的上限,因为随着dv/dt绝对值增大,b1和b2信号的中心会逐渐向电源或地偏移,直至b1和b2脉冲消失,二者差值为0,信号解调电路输出就会出现逻辑紊乱。

4、为了抑制两电压域电压差的瞬变干扰,专利cn114696771a所提供的电路结构中,第一级高通滤波电路可以为dv/dt提供电流泄放通道,减小dv/dt的干扰,同时共模检测电路能够检测共模瞬态信号并输出至解调电路,避免共模瞬态期间对输出进行干扰,从而改善抗共模瞬态干扰的能力。这种结构的缺点是抗dv/dt能力受到泄放电流大小的限制,泄放电流越大,抗dv/dt能力越大,但是电容接受端信号幅度就越小,信号传输效率就下降。

5、专利cn113271095a采用的电路结构,用过在发生共模瞬变时输出使能信号使解调电路停止工作,避免共模瞬变对输出信号造成影响。该结构的缺点是在共模瞬变期间,无法进行信号的传输。

6、专利cn113419595b采用的电路结构,通过电流镜电路来补偿共模电压,增强隔离器电路的抗干扰能力。该结构的缺点是电流镜电路不能够完全补偿共模电压,因此可能会对信号解调电路造成一定的影响。

技术实现思路

1、为了弥补现有技术的不足之处,本发明提供了一种具有抗瞬变干扰能力的隔离电路,该电路中的抗dv/dt电路可以检测出dv/dt(瞬变干扰)信号,同时吸收dv/dt信号在信号解调电路输入端口产生的位移电流,防止信号解调电路输入端电压产生偏移,使输入输出信号正常传输,有效抑制dv/dt噪声的影响。

2、为实现上述发明目的,本发明采用的技术方案如下:一种具有抗瞬变干扰的隔离电路,其特征在于:包括单通道信号隔离电路和双通道信号隔离电路两种情况;

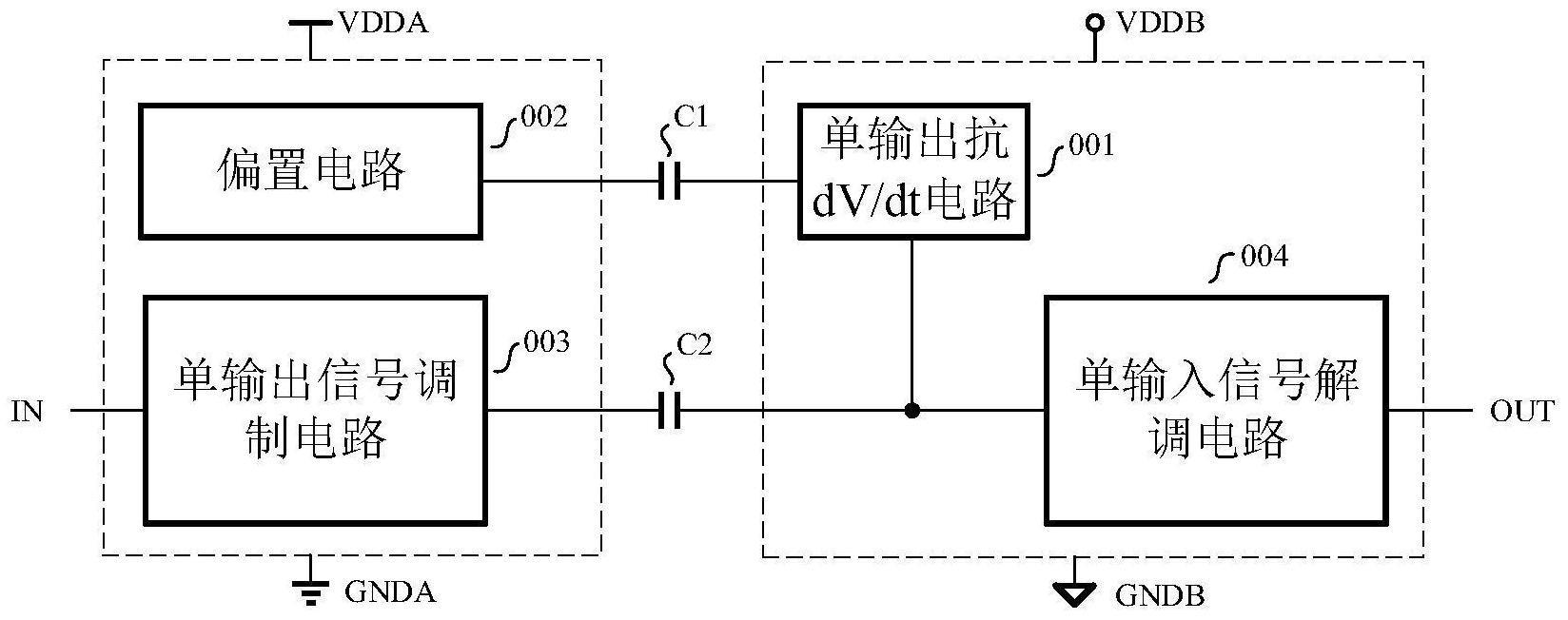

3、单通道信号隔离电路包括偏置电路002、单输出抗dv/dt电路001、单输出信号调制电路003、单输入信号解调电路004以及电容c1和电容c2,其中,偏置电路002和单输出信号调制电路003工作在第一电压域,电源和地分别为vdda和gnda;单输出抗dv/dt电路001和单输入信号解调电路004工作在第二电压域,电源和地分别为vddb和gndb;偏置电路002的输出通过电容c1连接单输出抗dv/dt电路001的输入端,单输出信号调制电路003的输入端作为具有抗瞬变干扰的单通道信号隔离电路的输入端in,单输出信号调制电路003的输出通过电容c2连接单输出抗dv/dt电路001的输出端和单输入信号解调电路004的输入端,单输入信号解调电路004的输出端作为具有抗瞬变干扰的单通道信号隔离电路的输出端out;

4、双通道信号隔离电路保留单通道信号隔离电路中的偏置电路002和电容c1,去除电容c2,,增设电容c3和c4,用双输出信号调制电路006替换单输出信号调制电路003、用双输出抗dv/dt电路005替换单输出抗dv/dt电路001以及用双输入信号解调电路007替换单输入信号解调电路004;其中,偏置电路002和双输出信号调制电路工作在第一电压域,电源和地分别为vdda和gnda,双输出抗dv/dt电路和双输入信号解调电路工作在第二电压域,电源和地分别为vddb和gndb;偏置电路002的输出通过电容c1连接双输出抗dv/dt电路005的输入端,双输出信号调制电路006的输入端作为具有抗瞬变干扰的双通道信号隔离电路的输入端in,双输出信号调制电路006的同相输出端通过电容c3连接双输出抗dv/dt电路005的一个输出端和双输入信号解调电路007的同相输入端,双输出信号调制电路006的反相输出端通过电容c4连接双输出抗dv/dt电路005的另一个输出端和双输入信号解调电路007的反相输入端,双输入信号解调电路007的输出端作为具有抗瞬变干扰的双通道信号隔离电路的输出端out。

5、进一步地,所述电容c1=c2=c3=c4,所述偏置电路002可以在以下三种结构中任取其中之一:

6、1)偏置电路包括电阻r1和r2,电源vdda连接电阻r1的一端,电阻r1的另一端连接电阻r2的一端并作为偏置电路002ad的输出端,电阻r2的另一端接地gnda;

7、2)偏置电路直接以电源vdda作为偏置电路002b的输出端;

8、3)偏置电路直接以地gnda作为偏置电路002c的输出端。

9、所述单输出抗dv/dt电路001包括基准电路100a和基准电路100b以及差分放大器101a;差分放大器101a的反相输入端连接基准电路100a的输出端和差分放大器101a的闭环输出端并作为单输出抗dv/dt电路001的输入端,差分放大器101a的同相输入端连接基准电路100b的输出端,差分放大器101a的开环输出端作为单输出抗dv/dt电路001的输出端;

10、所述双输出抗dv/dt电路005保留单输出抗dv/dt电路001中的基准电路100a、基准电路100b,用差分放大器101b替换差分放大器101a;差分放大器101b的反相输入端连接差分放大器101b的闭环输出端和基准电路100a的输出端并作为双输出dv/dt电路005的输入端,差分放大器101b的同相输入端连接基准电路100b的输出端,差分放大器101b的一个开环输出端作为双输出dv/dt电路005的一个输出端,差分放大器101b的另一个开环输出端作为双输出dv/dt电路005的另一个输出端。

11、所述差分放大器101a包括前级放大器200以及后续电路上调整管t0、上调整管t2、下调整管t2和下调整管t3;前级放大器200的同相输入端作为差分放大器101a的反相输入端,前级放大器200的反相输入端作为差分放大器101a的同相输入端,前级放大器200的高侧输出端连接上调整管t0的控制端和上调整管t2的控制端,前级放大器200的低侧输出端连接下调整管t1的控制端和下调整管t3的控制端;上调整管t0的电源端和上调整管t2的电源端均连接第二电压域的电源vddb,下调整管t1的电源端和下调整管t3的电源端均连接第二电压域的地端gndb;上调整管t0的输出端与下调整管t1的输出端互连并作为差分放大器101a的闭环输出端;上调整管t2的输出端与下调整管t3的输出端互连并作为差分放大器101a的开环输出端;

12、所述差分放大器101b保留差分放大器101a中的前级放大器200以及后续电路上调整管t0、上调整管t2、下调整管t1和下调整管t3,增设上调整管t4和下调整管t5;前级放大器200的同相输入端作为差分放大器101b的反相输入端,前级放大器200的反相输入端作为差分放大器101b的同相输入端,前级放大器的高侧输出端连接上调整管t0的控制端、上调整管t2的控制端和上调整管t4的控制端,前级放大器200的低侧输出端连接下调整管t1的控制端、下调整管t3的控制端和下调整管t5的控制端;上调整管t0的电源端、上调整管t2的电压端和上调整管t4的电源端均连接第二电压域的电源端vddb,下调整管t1的电源端、下调整管t3的电源端和下调整管t5的电源端均连接第二电压域的接地端gndb;上调整管t0的输出端与下调整管t1的输出端互连并作为差分放大器101b的闭环输出端;上调整管t2的输出端与下调整管t3的输出端互连并作为差分放大器101b的一个开环输出端;上调整管t4的输出端与下调整管t5的输出端互连并作为差分放大器101b的另一个开环输出端;

13、进一步地,所述上调整管t0、上调整管t2和上调整管t4可采用pmos管或pnp管,其中,pmos管的栅极和pnp管的基极分别为控制端;pmos管的源极和pnp管的发射极分别为电源端,连接第二电压域vddb;pmos管的漏极和pnp管的集电极分别为输出端;下调整管t1、下调整管t3和下调整管t5可采用nmos管或npn管,其中,nmos管的栅极和npn管的基极分别为控制端;nmos管的源极和npn管的发射极分别为电源端,连接第二电压域gndb;nmos管的漏极和npn管的集电极分别为输出端。

14、所述差分放大器101a中的前级放大器200包括pmos管p0、pmos管p1、nmos管n0、nmos管n1、nmos管n01以及电流源i0和i1;前级放大器200后续电路的上调整管t0和上调整管t2为pmos管,下调整管t1和下调整管t3为nmos管;pmos管p0的源极、pmos管p1的源极、nmos管n01的漏极以及pmos管t0的源极和pmos管t2的源极均连接电源vddb,pmos管p0的栅极与pmos管p1的栅极互连并连接pmos管p0的漏极和nmos管n0的漏极,nmos管n0的栅极作为前级放大器200的同相输入端,nmos管n1的栅极作为前级放大器200的反相输入端,nmos管n0的源极与nmos管n1的源极互连并经电流源i0后接地gndb,pmos管p1的漏极连接nmos管n1的漏极并作为前级放大器200的高侧(高电平)输出端与nmos管n01的栅极以及pmos管t0的栅极和pmos管t2的栅极连接在一起,nmos管n01的源极连接电流源i1的输入端并作为前级放大器200的低侧(低电平)输出端与nmos管t1的栅极和nmos管t3的栅极连接在一起,电流源i1的输出端连接nmos管t1的源极和nmos管t3的源极并接地gndb,pmos管t0的漏极与nmos管t1的漏极连接并作为前差分放大器101a的闭环输出端,pmos管t2的漏极与nmos管t3的漏极连接并作为前差分放大器101a的开环输出端。

15、进一步地,可以用pnp三极管q0替代pmos管p0、用pnp三极管q1替代pmos管p1、用npn三极管q3替代nmos管n0、用npn三极管q4替代nmos管n1、用npn三极管q2替代nmos管n01以及用pnp三极管t0替代pmos管t0、用pnp三极管t2替代pmos管t2、用npn三极管t1替代nmos管t1、用npn三极管t3替代nmos管t3;pnp三极管q0的发射极、pnp三极管q1的发射极、npn三极管q2的集电极以及pnp三极管t0的发射极和pnp三极管t2的发射极均连接电源vddb,pnp三极管q0的基极与pnp三极管q1的基极互连并连接pnp三极管q0的集电极和npn三极管q3的集电极,npn三极管q3的基极作为前级放大器200的同相输入端,npn三极管q4的基极作为前级放大器200的反相输入端,npn三极管q3的发射极与npn三极管q4的发射极互连并经电流源i0后接地gndb,pnp三极管q1的集电极连接npn三极管q4的集电极并作为前级放大器200的高侧(高电平)输出端与npn三极管q2的基极以及pnp三极管t0的基极和pnp三极管t0的基极连接在一起,npn三极管q2的发射极连接电流源i1的输入端并作为前级放大器200的低侧(低电平)输出端与npn三极管t1的基极和npn三极管t3的基极连接在一起,电流源i1的输出端连接npn三极管t1的发射极和npn三极管t3的发射极并接地gndb,pnp三极管t0的集电极与npn三极管t1的集电极连接并作为前差分放大器101a的闭环输出端,pnp三极管t2的集电极与npn三极管t3的集电极连接并作为前差分放大器101a的开环输出端。

16、所述单输出信号调制电路003包括振荡器和与门and1,振荡器输出连接与门and1的一个输入端,与门and1的另一个输入端作为单输出信号调制电路003的输入端,该输入端同时也是抗瞬变干扰的单通道信号隔离电路的输入端in,与门and1的输出端作为单输出信号调制电路003的输出端;

17、所述双输出信号调制电路006保留单输出信号调制电路003中的振荡器和与门and1,增设反相器inv1,振荡器输出连接与门and1的一个输入端,与门and1的另一个输入端作为双输出信号调制电路006的输入端,该输入端同时也是抗瞬变干扰的双通道信号隔离电路的输入端in,与门and1的输出连接反相器inv1的输入端并作为双输出信号调制电路006的同相输出端,反相器inv1的输出端作为双输出信号调制电路的反相输出端。

18、所述单输入信号解调电路004包括基准电路100c、基准电路100d以及比较器cmp1和滤波器,基准电路100c的输出连接比较器cmp1的同相输入端并作为单输入信号解调电路004的输入端,基准电路100d的输出连接比较器cmp1的反相输入端,比较器cmp1的输出连接滤波器的输入端,滤波器的输出端作为单输入信号解调电路004的输出端;

19、所述双输入信号解调电路007保留单输入信号解调电路004中的基准电路100c、基准电路100d以及比较器cmp1和滤波器,增设基准电路100e和比较器cmp2,基准电路100c的输出连接比较器cmp1的同相输入端并作为双输入信号解调电路007的同相输入端,基准电路100d的输出连接比较器cmp1的反相输入端和比较器cmp2的反相输入端,比较器cmp2的同相输入端连接基准电路101e的输出并作为双输入信号解调电路007的反相输入端,比较器cmp1的输出端与比较器cmp2的输出端互连并连接滤波器的输入端,滤波器的输出端作为双输入信号解调电路007的输出端。

20、进一步地,在单输入信号解调电路004中,可以保留基准电路100c和基准电路100d以及比较器cmp1和滤波器,增设比较器cmp2,基准电路100c的输出连接比较器cmp1的同相输入端和比较器cmp2的反相输入端并作为单输入信号解调电路004的输入端,基准电路100d的输出连接比较器cmp1的反相输入端和比较器cmp2的同相输入端,比较器cmp1的输出端与比较器cmp2的输出端互连并连接滤波器的输入端,滤波器的输出端作为单输入信号解调电路004的输出端;

21、在双输入信号解调电路007中,可以保留单输入信号解调电路004中的基准电路100c、基准电路100e以及比较器cmp1、比较器cmp1和滤波器,去除基准电路100d,基准电路100c的输出连接比较器cmp1的同相输入端和比较器cmp2的反相输入端并作为双输入信号解调电路007的同相输入端,基准电路100e的输出连接比较器cmp1的反相输入端和比较器cmp2的同相输入端并作为双输入信号解调电路007的反相输入端,比较器cmp1的输出端与比较器cmp2的输出端互连并连接滤波器的输入端,滤波器的输出端作为双输入信号解调电路007的输出端。

22、进一步地,所述基准电路100a、基准电路100b、基准电路100c、基准电路100d及基准电路100e的电路可以采用相同结构,任取以下三种之一:

23、1)基准电路包括电阻r3和r4,电源vddb连接电阻r3的一端,电阻r3的另一端连接电阻r4的一端并作为基准电路的输出端,电阻r4的另一端接地gndb;

24、2)基准电路包括电流源i2和nmos管n2,电源vddb连接电流源i2的输入端,电流源i2的输出端连接nmos管n2的漏极和栅极并作为基准电路的输出端,nmos管n2的源极接地gndb;

25、3)基准电路包括pmos管p3和电流源i3,电源vddb连接pmos管p3的源极,pmos管p3的栅极和漏极均连接电流源i3的输入端并作为基准电路的输出端,电流源i3的输出端接地gndb。

26、本发明的优点及显著效果:

27、1、本发明包括偏置电路、抗dv/dt电路、信号调制电路、信号解调电路和若干电容。偏置电路和信号调制电路工作在第一电压域,抗dv/dt电路和信号解调电路工作在第二电压域,信号从第一电压域向第二电压域传输。当第一电压域和第二电压域之间的压差产生变化(瞬变)时,抗dv/dt电路能够检测该差压变化率dv/dt,然后将信号解调电路的输入端口的电压稳定在常规电平,该常规电平是两电压域压差没有变化时的电平,从而消除dv/dt的影响,避免由dv/dt导致的输出逻辑紊乱问题,即使dv/dt期间信号也能在两个电压域之间进行有效传输。

28、2、本发明具有很高的抗dv/dt能力,抗dv/dt电路能够完全吸收dv/dt信号在信号解调电路输入端口产生的位移电流,消除dv/dt信号对信号正常传输的影响。

29、3、本发明提出的抗dv/dt电路既能适用于单通道信号调制/解调电路,也能适用于双通道信号调制/解调电路。

- 还没有人留言评论。精彩留言会获得点赞!