一种并发数为6的4:2压缩器

本发明属于集成电路,具体涉及一种并发数为6的4:2压缩器。

背景技术:

1、乘法器作为基本运算单元,广泛应用于各种集成电路工程当中。无论是通信、射频等传统领域,还是人工智能、大语言模型等新兴领域,乘法器都是其中使用频率高、复用程度大的器件,其结构的差异会对电路的延迟、功耗、面积等造成巨大的影响。硬件乘法器的构成通常由编码部分、根据编码结果生成部分积的部分积生成部分、树形部分积压缩部分、加法器部分这四部分组成。

2、现有技术中,编码部分普遍采用基4-booth编码方式,因为基4-booth编码可以将部分积的数量减少一半,大大减少了后续的计算量。高基booth编码可以将部分积的个数进一步压缩,但是在压缩的过程中会计算乘3,而乘3对于二进制电路而言是一个很棘手的事情,因此行业内无特殊需求的情况下普遍都会采用基4-booth编码。对于基4-booth编码而言,其将乘数每三位作为一个编码,生成的结果有以下几种:+2a、+a、0、-a、-2a,其中-a对原本的a“取反加-”,+2a对a左移补0,-2a对-a左移补1,即可完成计算。部分积生成部分就是根据编码结果,选择这个位置的部分积应该是+2a、+a、0、-a、-2a这五种情况的哪一种。根据基4-booth编码的原理,生成部分积的个数应该是乘法器乘数位宽的一半。部分积压缩部分在行业内通常使用wallace、dadda树形结构,他们的核心是通过3:2压缩器、半加器来压缩部分积,最终只剩下两个部分积,最后通过乘法器的加法器部分来将这两个部分积相加,求出最终的乘法结果。现有技术中已经有用压缩比更高的5:2压缩器等加快部分积的压缩速度。但是这种高阶压缩器的结构都是以前述的基本压缩器构成的,在使用的过程中很不方便。

3、在求-a的时候,取反只需资源消耗很少的非门就能完成,但是+1需要使用一个对应长度的加法器,面积消耗很大的同时,对关键路径的影响也十分巨大。将需要加的1称为尾数,因此在实际的实现过程中,通常使用先取反,将需要加的尾数放置于下一个部分积的末尾。因为各个部分积的权重不同,将尾数放置于下一个部分积的末尾并不会发生同一个位置有两个数的情况。通过这种方法,可以避免在计算-a的过程中引入加法器的延时和面积,但是在最后一个部分积生成的尾数没有可以放置的地方,因此会额外生成一个单bit的部分积,在后文中称其为尾数部分积,长度为1bit,其权重与最后一个部分积的最低位权重一致。而在处理尾数部分积时,现有技术中通常将尾数部分积看作一个完整的部分积,在最后一步使用一组3:2压缩器去对其进行处理,但这样处理的结果就是在原本压缩部分积的基础之上又额外的增加了一组3:2压缩器的资源以及关键路径。

4、综上所述,现有技术中的压缩器都是基于传统的基本压缩器构成的,在使用的过程中很不方便,而且在处理尾数部分积时还存在消耗资源又增加延时的等问题。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提出一种能够减少消耗资源且缩短关键路径的并发数为6的4:2压缩器。

2、本发明的一种并发数为6的4:2压缩器,包括计算进位部分和接收后级进位部分;所述4:2压缩器的输入信号为第一路输入信号、第二路输入信号、第三路输入信号,和第四路输入信号,进位输入信号为第一路进位输入信号和第二路进位输入信号,输出信号为第一路输出信号和第二路输出信号,进位输出信号为第一路进位输出信号和第二路进位输出信号。

3、进一步,所述4:2压缩器中计算进位部分的输入的信号有:第一路输入信号、第二路输入信号、第三路输入信号,和第四路输入信号;所述计算进位部分的输出信号有:第一路进位输出信号、第二路进位输出信号,以及内部连接信号。

4、进一步,所述4:2压缩器中接收后级进位部分的输入的信号有:第一路进位输入信号、第二路进位输入信号,以及内部连接信号,所述接收后级进位部分的输出的信号有:第一路输出信号和第二路输出信号。

5、进一步,所述4:2压缩器中的信号满足下列关系:(c_out2+c_out1+carry)*2+sum*1=(a+b+c+d+c_in1+c_in2)*1。

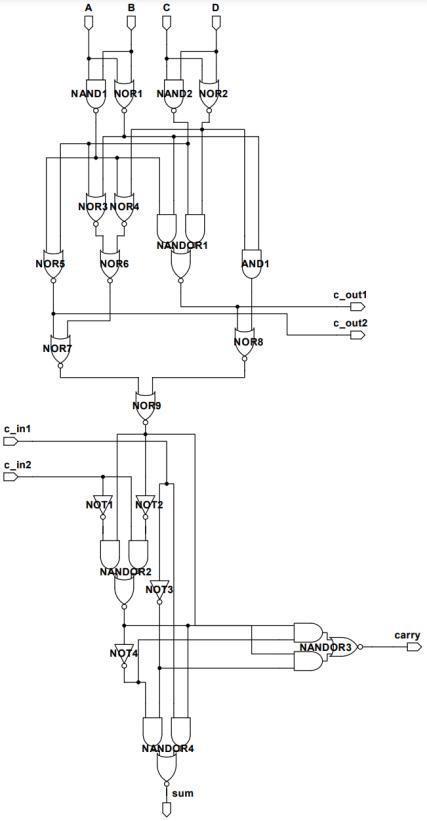

6、进一步,所述4:2压缩器中的计算进位部分包括二输入的第一与非门、第一或非门、第二与非门、第二或非门、第三或非门、第四或非门、第五或非门、第六或非门、第一与门、第七或非门、第八或非门、第九或非门,以及四输入的第一与或非门;

7、且所述第一与非门和第一或非门的输入端为4:2压缩器的第一路输入信号和第二路输入信号;所述第二与非门和第二或非门的输入端为4:2压缩器的第三路输入信号和第四路输入信号;所述第三或非门的输入端为第二与非门的输出端和第一或非门的输出端;所述第四或非门的输入端为第一与非门的输出端和第二或非门的输出端;所述第五或非门的输入端为第一与非门的输出端和第二与非门的输出端;所述第六或非门的输入端为第三或非门的输出端和第四或非门的输出端;所述第一与或非门的输入端为第一与非门的输出端、第一或非门的输出端、第二与非门的输出端和第二或非门的输出端;所述第一与门的输入端为第一或非门的输出端和第二或非门的输出端;所述第七或非门的输入端为第五或非门的输出端和第六或非门的输出端;所述第八或非门的输入端为第一与或非门的输出端和第一与门的输出端;所述第九或非门的输入端为第七或非门的输出端和第八或非门的输出端;

8、所述计算进位部分的第一路进位输出信号为第一与或非门的输出端;所述计算进位部分的第二路进位输出信号为第五或非门的输出端;所述计算进位部分的内部连接信号为九或非门的输出端。

9、进一步,所述4:2压缩器中接收后级进位部分包括一输入的第一非门、第二非门、第三非门、第四非门,四输入的第二与或非门、第三与或非门、第四与或非门;

10、所述第一非门的输入端为第二路进位输入信号;所述第二非门的输入端为内部连接信号;所述第二与或非门的输入端为第一非门的输出端、内部连接信号、第二路进位输入信号和第二非门的输出端;所述第三非门的输入端为第一路进位输入信号;所述第四非门的输入端为第二与或非门的输出端;所述第三与或非门的输入端为内部连接信号、第四非门的输出端、第二与或非门的输出端和第三非门的输出端;所述第四与或非门的输入端为第四非门的输出端、第三非门的输出端、第一路进位输入信号和第二与或非门的输出端;所述接收后级进位部分的第一路输出信号为第四与或非门的输出端;所述接收后级进位部分的第二路输出信号为第三与或非门的输出端。

11、与现有技术相比,本发明具有以下有益的技术效果:

12、本发明所述的并发数为6的4:2压缩器,一方面,对于单bit的尾数部分积可以直接纳入计算,在总体计算过程中减少了消耗的资源,缩短关键路径;另一方面大大提升了树形部分积压缩部分的性能,且不会对其他部分(编码部分、部分积生成部分以及最后的加法器部分)的结构造成影响,也就是说本发明所述的树形部分积压缩部分具有普适性,因此在具体应用中,例如修改工程时易于使用,可以进行高效替换。

13、此外所述4:2压缩器在级联时还不会将延迟沿着进位链传播。由于第一路进位输出信号c_out1和第二路进位输出信号c_out2的值仅与第一路输入信号a、第二路输入信号b、第三路输入信号c,以及第四路输入信号d有关,而与第一路进位输入信号c_in1和第二路进位输入信号c_in2无关,因此计算的延迟不会顺着进位链传播。在具体应用中,无论并联多少个本发明所述的4:2压缩器,其关键路径均为:第一与非门nand1→第三或非门nor3→第六或非门 nor6→第七或非门nor7→第九或非门 nor9→第二或门not2→第二与或非门nandor2→第四非门 not4→第四与非门nandor4。

- 还没有人留言评论。精彩留言会获得点赞!