一种阻流异质结可编程存储器件的制作方法

本发明涉及存储器件领域,特别是涉及一种阻流异质结可编程存储器件。

背景技术:

1、现有技术中,涉及的存储器件,一类具有低成本、高存储密度特点的3d多层堆叠存储器阵列,如专利cn101615656a和cn109545787a中,由导电类型相反的材料构成水平字线(wl)和垂直位线(bl),以及置于二者相交处的可编程绝缘介质构成一个存储单元。

2、该类3d存储器的特点是导电类型相反的wl和bl,如,p型/n型高掺杂多晶硅。当可编程介质层因编程而成为低阻状态,比如反熔丝一次可编程(anti-fuse otp)存储绝缘介质被介电击穿成为导电介质后,bl和wl自动构成一个单向导通的二极管,这一设置的优势是,在不使用额外空间设置二极管器件的基础上,仍然对存储密度极高的3d多层堆叠存储器具有有效的控制作用,因此制备成本也较低。

3、然而,实际情况下,任何二极管总是存在一定的反向电流,若反向电流较大,则存在一定情况使得不能维持稳定的编程电压,导致工作失效。此类工作失效情况尤其在存储阵列规模较大、集成度较大时,比如128层、单层1mbit的以上的情况下,是可以在正常工作的情况下发生的。存储阵列规模越大,对反向电流大小的控制要求也越严格。因此,为了保证存储器的工作稳定性,针对此类3d存储器件的存储单元,在绝缘存储介质与wl或bl之间加一层半导体材料作为缓冲层,如专利cn109545787a介于单元器件处于中间的的介质层,可以由存储绝缘介质和低掺杂半导体两个部分构成,低掺杂半导体的导电类型与其直接接触的wl或bl相同且掺杂浓度较低,一般为低掺杂多晶硅,可以在不影响器件二极管单向导通特性的同时,通过优化缓冲层的厚度来有效控制反向电流大小。

4、这一方法的特点是,缓冲层厚度越厚,反向电流越小。但是,缓冲层厚度往往占用芯片使用面积,尤其当存储单元尺寸进一步缩小至深亚微米以下以提高存储密度时,缓冲层仍然会占存储单元相当比例的面积,使得存储器密度的进一步提高受到限制。并且,由于一般缓冲层需沉积在高深宽比的存储孔侧壁上,若采用晶体半导体,如低掺杂多晶硅作为缓冲层,则工艺上实现的成本很高,因为厚度均匀性控制良好的原子层沉积(ald)技术所制备的薄膜多为无序相,且掺杂浓度不易控制。因此现有技术往往需要在器件性能、芯片占用面积(存储密度)和工艺成本等多方面进行折中考虑。

技术实现思路

1、本发明的目的是提供一种阻流异质结可编程存储器件,可实现低成本高密度存储。

2、为实现上述目的,本发明提供了如下方案:

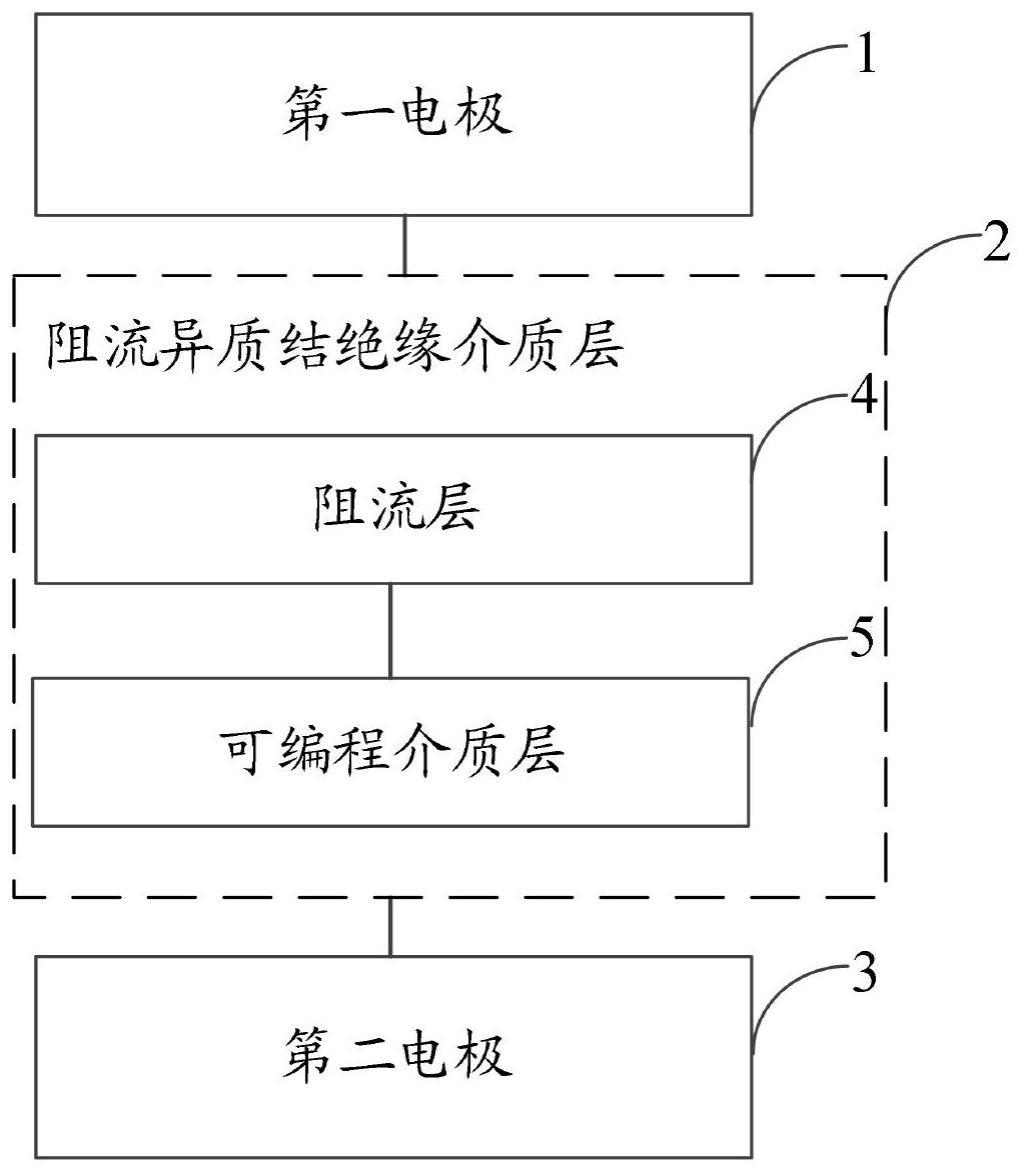

3、一种阻流异质结可编程存储器件,所述存储器件包括:依次连接的第一电极、阻流异质结绝缘介质层和第二电极;

4、所述阻流异质结绝缘介质层包括:阻流层和可编程介质层;

5、所述阻流层和所述可编程介质层采用的绝缘介质不同;所述第一电极和所述第二电极采用设定配套材料构成;所述阻流层的禁带宽度小于所述可编程介质层的禁带宽度;所述阻流层与直接接触的第一电极或第二电极之间不额外形成接触势垒。

6、可选地,所述可编程介质层采用的绝缘介质为反熔丝绝缘介质、阻变非易失存储介质或者相变非易失存储介质。

7、可选地,所述反熔丝绝缘介质的材料为氧化硅或者氧化铝。

8、可选地,所述阻流层采用的绝缘介质包括电荷转移绝缘体或电性绝缘体。

9、可选地,所述电荷转移绝缘体包括tio2、zno或者hfo2薄膜。

10、可选地,所述电性绝缘体包括本征sic。

11、可选地,所述阻流层的形态为晶态、多晶态或者无序态;所述阻流层为无序hfo2薄膜、无序sic薄膜或者无序硅薄膜。

12、可选地,所述设定配套材料包括四种配套材料;

13、其中,所述第一电极为p型半导体或导体,所述第二电极为n型半导体;

14、或者,所述第一电极为p型肖特基金属,所述第二电极为n+半导体或导体;

15、或者,所述第一电极为n+半导体或导体,所述第二电极为p+半导体;

16、或者,所述第一电极为n型肖特基金属,所述第二电极为p+半导体或导体。

17、可选地,所述p型肖特基金属为au或者pt。

18、可选地,所述n型肖特基金属为al。

19、根据本发明提供的具体实施例,本发明公开了以下技术效果:

20、本发明提供了一种阻流异质结可编程存储器件,由于绝缘阻流层的加入,因其绝缘性,大大降低了反向电流的隧道效应,可以在阻流层厚度较小、占用芯片面积较小的情况下,仍然保证极低的反向电流,并且无需采用采用晶体半导体进行缓冲,使得工艺成本更低。由于阻流层和可编程介质层采用的绝缘介质不同,且阻流层的禁带宽度小于可编程介质层的禁带宽度,和其接触的第一或第二电极之间不额外形成接触势垒,因此阻流层的加入不影响器件处于正向工作时的电流电压特性。因此本发明可实现低成本高密度存储。

技术特征:

1.一种阻流异质结可编程存储器件,其特征在于,所述存储器件包括:依次连接的第一电极、阻流异质结绝缘介质层和第二电极;

2.根据权利要求1所述的阻流异质结可编程存储器件,其特征在于,所述可编程介质层采用的绝缘介质为反熔丝绝缘介质、阻变非易失存储介质或者相变非易失存储介质。

3.根据权利要求2所述的阻流异质结可编程存储器件,其特征在于,所述反熔丝绝缘介质的材料为氧化硅或者氧化铝。

4.根据权利要求1所述的阻流异质结可编程存储器件,其特征在于,所述阻流层采用的绝缘介质包括电荷转移绝缘体或电性绝缘体。

5.根据权利要求4所述的阻流异质结可编程存储器件,其特征在于,所述电荷转移绝缘体包括tio2、zno或者hfo2薄膜。

6.根据权利要求4所述的阻流异质结可编程存储器件,其特征在于,所述电性绝缘体包括本征sic。

7.根据权利要求1所述的阻流异质结可编程存储器件,其特征在于,所述阻流层的形态为晶态、多晶态或者无序态;所述阻流层为无序hfo2薄膜、无序sic薄膜或者无序硅薄膜。

8.根据权利要求1所述的阻流异质结可编程存储器件,其特征在于,所述设定配套材料包括四种配套材料;

9.根据权利要求8所述的阻流异质结可编程存储器件,其特征在于,所述p型肖特基金属为au或者pt。

10.根据权利要求8所述的阻流异质结可编程存储器件,其特征在于,所述n型肖特基金属为al。

技术总结

本发明公开一种阻流异质结可编程存储器件,涉及存储器件领域;存储器件包括:依次连接的第一电极、阻流异质结绝缘介质层和第二电极;阻流异质结绝缘介质层包括:阻流层和可编程介质层;阻流层和可编程介质层采用的绝缘介质不同;第一电极和第二电极采用设定配套材料构成;阻流层的禁带宽度小于可编程介质层的禁带宽度;本发明能够实现低成本高密度存储。

技术研发人员:王苛,彭泽忠

受保护的技术使用者:成都皮兆永存科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!