一种可重构芯粒间连接结构的电路及芯片的制作方法

本发明涉及芯粒制造领域,特别是涉及一种芯粒间的可重构连接结构及芯片。

背景技术:

1、晶圆(wafer)是半导体集成电路的核心材料在晶圆上可以加工制作出各种电路元件结构,使之成为有特定电性功能的ic产品。

2、对于由多种类型的芯粒构成的芯片,通常由多个晶圆独立生产每种类型的芯粒,最终将这些芯粒重新组合再采用高级封装技术将多个芯粒封装在一起实现复杂的芯片功能。上述制造芯片的方式需要采用高级封装技术,需要消耗大量的封装成本。

技术实现思路

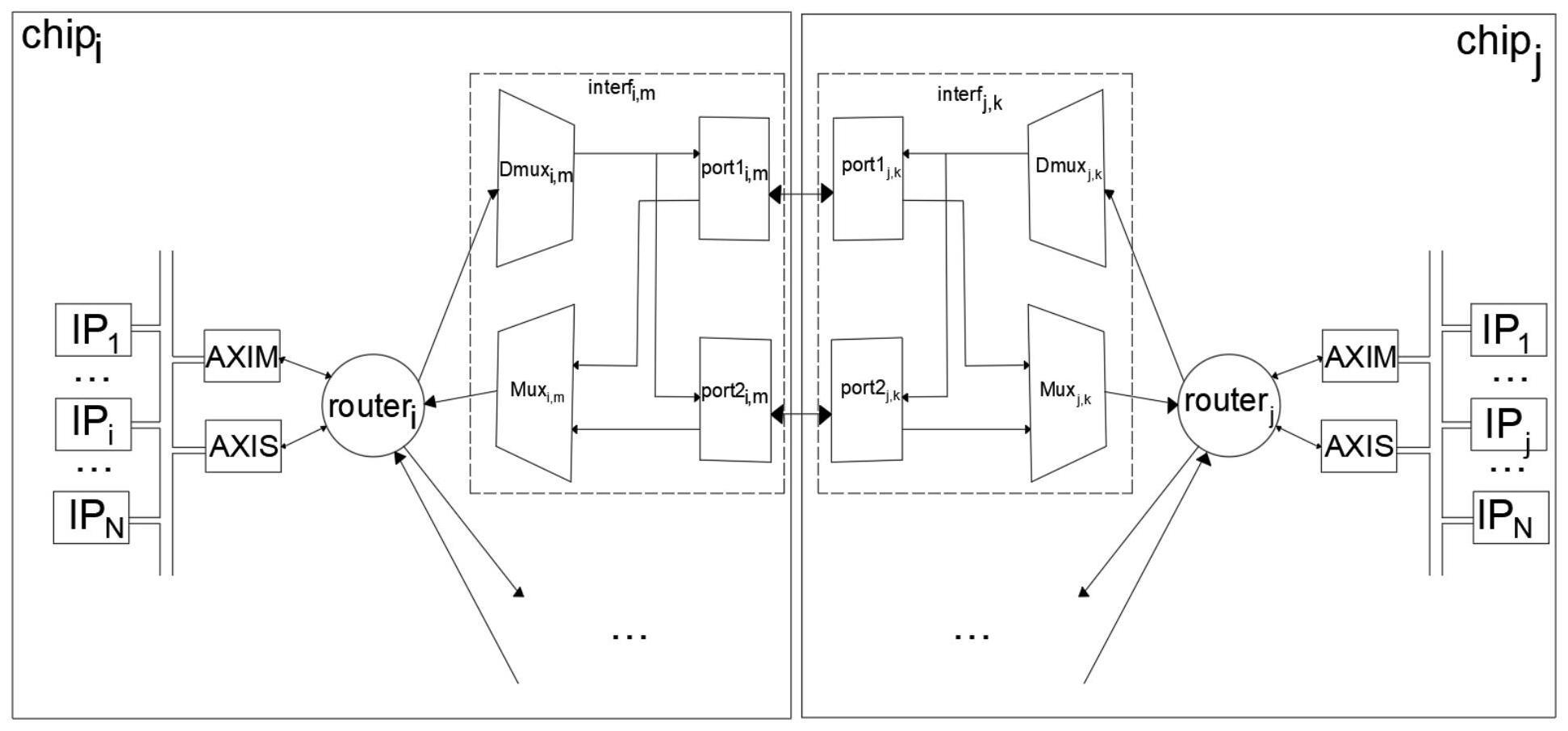

1、针对上述技术问题,本发明采用的技术方案为:一种可重构芯粒间连接结构的电路,第i个芯粒chipi和物理位置与chipi相邻的第j个芯粒chipj之间预先连接所有的物理连线coni,j,i≠j且1≤j≤n。

2、所述chipi包括m个接口单元interfi,通过第i个路由器routeri将interfi接入片上网络;chipj包括k个接口单元interfj,通过第j个路由器routerj将interfj接入片上网络。

3、所述interfi中的第m个接口单元interfi,m包括多路分配器dmuxi,m、多路复用器muxi,m、通用输入输出端口port1i,m和通用输入输出端口port2i,m;其中,多路分配器dmuxi,m的输入通道连接routeri,输出通道分别接入port1i,m和port2i,m;多路复用器muxi,m的输出通道连接routeri,输入通道分别接入port1i,m和port2i,m。

4、所述interfj,k包括多路分配器dmuxj,k、多路复用器muxj,k、通用输入输出端口port1j,k和通用输入输出端口port2j,k;其中,多路分配器dmuxj,k的输入通道连接routerj,输出通道分别接入port1j,k和port2j,k;多路复用器muxj,k的输出通道连接routerj,输入通道分别接入port1j,k和port2j,k。

5、当chipi通过interfi,m和interfj,k接入chipj时,port1i,m通过物理连线连接port1j,k,port2i,m通过物理连线连接port2j,k。

6、本发明至少具有以下有益效果:

7、芯粒的接口单元中通用输入输出端口具有选通和阻塞功能,使得芯粒之间的连接可重构。进而保证芯粒在保持连接和切断之间切换仍能正常工作,在保持连接的状态下不需要采用高级封装,相比较现有技术中将所有芯粒重组后需要采用高级封装使两个芯粒连通的方式,本发明能够避免芯粒组合时采用高级封装技术,节约了封装成本。

技术特征:

1.一种可重构芯粒间连接结构的电路,其特征在于,第i个芯粒chipi和物理位置与chipi相邻的第j个芯粒chipj之间预先连接所有的物理连线coni,j,i≠j且1≤j≤n;

2.根据权利要求1所述的电路,其特征在于,chipi中的port1i,m被配置为输入模式或输出模式,port2i,m被配置为输入模式或输出模式,且port1i,m和port2i,m配置的模式不同。

3.根据权利要求1所述的电路,其特征在于,当芯粒的物理连线被切断时,为被配置为输入模式的通用输入输出端口配置缺省值。

4.根据权利要求1所述的电路,其特征在于,所述chip中的n个芯粒高度相同。

5.根据权利要求1所述的电路,其特征在于,coni,j具有连接状态和断开状态,当coni,j被指定为连接状态时,coni,j保持预连接状态,chipi和chipj直接连接基板进行封装,在chipi和chipj与基板之间不连接中介层。

6.根据权利要求1所述的电路,其特征在于,coni,j具有连接状态和断开状态,当coni,j被指定为断开状态时,coni,j被切断,chipi和chipj通过中介层连通后连接基板进行封装。

7.根据权利要求1所述的电路,其特征在于,coni,j的获取步骤包括:在对晶圆上的芯粒进行切割时,选择不切断chipi和chipj之间的rdl连接线。

8.根据权利要求1所述的电路,其特征在于,port1i,m和port2i,m均为gpio接口。

9.一种芯片,其特征在于,所述芯片包括n个芯粒chip={chip1,chip2,…,chipi,…,chipn},chipi为芯片中的第i个芯粒,1≤i≤n;在物理位置相邻的芯粒之间具有权利要求1-8任意一项所述的一种可重构芯粒间连接结构的电路。

技术总结

本发明涉及芯粒制造领域,特别是涉及一种芯粒间的可重构连接结构及芯片,其包括第i个芯粒chip<subgt;i</subgt;及其物理位置相邻的第j个芯粒chip<subgt;j</subgt;之间预先连接所有的物理连线;chip<subgt;i</subgt;包括M个接口单元interf<subgt;i</subgt;,通过第i个路由器router<subgt;i</subgt;将interf<subgt;i</subgt;接入片上网络;chip<subgt;j</subgt;包括K个接口单元interf<subgt;j</subgt;,通过第j个路由器router<subgt;j</subgt;将interf<subgt;j</subgt;接入片上网络;当chip<subgt;i</subgt;通过相应的接口单元接入chip<subgt;j</subgt;时,相应接口单元中通用输入输出端口通过物理连线连接,芯粒的接口单元中通用输入输出端口具有选通和阻塞功能,使得芯粒之间的连接可重构,进而节约封装成本的目的。

技术研发人员:杨建

受保护的技术使用者:毫厘智能科技(江苏)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!