任意整数分频电路及高速时钟芯片、通信芯片的制作方法

本技术属于电子电路,尤其涉及一种任意整数分频电路及高速时钟芯片、通信芯片。

背景技术:

1、任意整数分频电路多用于时钟发生电路中。其输入为较高频时钟信号,输出则是分频后的低频时钟,随着集成电路往高频率和宽适用范围方向发展,需要分频器支持更高输入频率,更多分频位数。

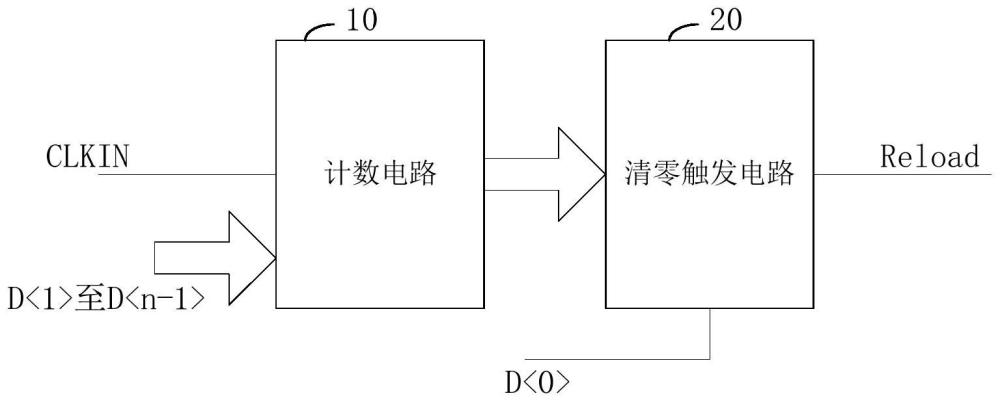

2、相关的任意整数分频电路采用二分频器依次顺序分频后进行计数递增或递减的方式进行时钟分频,分频比n由电路结构确定,可以设置为数字控制字d<n-1>、…、d<1>、d<0>控制。例如,在图1所示的任意整数分频电路中,当输出时钟reload到来时,由分频控制字d<n-1>、…,d<1>、d<0>确定每个分频器的初始状态,clk(m)的值将复位成d<m>;当输出时钟reload释放后,各二分频器开始工作,clk(n-1)至clk(0)时钟所表示的二进制值按照递减的方式减小到0,当clk(n-1)至clk(0)均为0后,其后的或门检测出复位信号,再经过一个触发器后输出输出时钟reload。起始设置的分频控制字d<n-1>、…、d<1>、d<0>决定了分频比,d<n-1>、…,d<1>、d<0>代表的十进制值为d=20×d<0>+21×d<1>+22×d<2>+23×d<3>+…+2n-1×d<n-1>,分频比为d+1,加1原因是计数复位时使用了1个触发器进行打拍,导致时钟复位信号往后延了一个固定周期。

3、相关的任意整数分频电路结构较简单,第一级二分频模块101工作频率为f,第二级二分频模块102工作频率为f/2,最后一级二分频模块103工作频率为f/2n。

4、二分频模块除了需要支持二分频功能外,还需要支持数据清零和复位功能。相关的二分频电路使用逻辑门和锁存器构成,可以实现以上功能,第一级二分频模块101的工作频率在整个系统中最高,整个电路的频率约束瓶颈在第一级二分频模块101,但是这些门电路对于输入频率比较敏感,在高频输入时二分频功能将失效,这将直接导致任意整数分频电路失效。

5、故相关的任意整数分频电路存在在给定的工艺条件下,存在工作速度瓶颈,从而导致工作频率不够高并无法在超高速系统中应用的问题。

技术实现思路

1、本技术的目的在于提供一种任意整数分频电路及高速时钟芯片、通信芯片,旨在解决相关的任意整数分频电路在给定的工艺条件下,存在工作速度瓶颈,从而导致工作频率不够高并无法在超高速系统中应用的问题。

2、本技术实施例提供了一种任意整数分频电路,包括:

3、计数电路,配置为接入输入时钟,从计数数值对所述输入时钟进行递减计数以输出计数信号,且当计数电路的计数达到0时回零重新计数;

4、清零触发电路,配置为当所述计数信号为0时,生成清零信号,且响应于第1控制字为0,将所述清零信号延时3个周期以输出输出时钟,响应于所述第1控制字为1,将所述清零信号延时4个周期以输出所述输出时钟;所述周期为所述输入时钟的周期;

5、其中,所述计数数值为2k+1,k为d<1>+21×d<2>+22×d<3>+…+2n-2×d<n-1>,则d=2*k+d<0>;d<i>为第i+1控制字,i为小于n且大于等于0的整数,k为大于等于0的整数。

6、在其中一个实施例中,所述任意整数分频电路的分频比为d+4,其中,d为20×d<0>+21×d<1>+22×d<2>+23×d<3>+…+2n-1×d<n-1>。

7、在其中一个实施例中,所述计数信号包括n个子计数信号;所述计数电路包括:

8、预分频电路,配置为根据第2控制字对所述输入时钟进行两次二分频,以输出第1个子计数信号和第2个子计数信号;其中,所述预分频电路包括两个tspc d触发器;

9、计数器,配置为分别根据第3控制字至第n控制字依次对第2个子计数信号进行n-2次二分频,以输出第3个子计数信号至第n个子计数信号;

10、清零触发电路,具体配置为当所有子计数信号均为0时,生成所述清零信号,且响应于所述第1控制字为0,将所述清零信号延时3个周期以输出所述输出时钟,响应于第1控制字为1,将所述清零信号延时4个周期以输出所述输出时钟。

11、在其中一个实施例中,所述计数器包括:

12、依次串联连接的第1二分频器至第n-2二分频器;

13、第j二分频器配置为响应于输出时钟为高电平时,将第j+2控制字作为第j+2子计数信号输出,响应于输出时钟为低电平时,对第j-1子计数信号二分频以输出所述输出时钟。j为小于等于n-2的正整数。

14、在其中一个实施例中,所述第1二分频器至所述第n-2二分频器均为数字二分频器。

15、在其中一个实施例中,所述预分频电路包括第一tspc d触发器、第二tspc d触发器、反相器、传输门以及场效应管q1;

16、第一tspc d触发器的时钟端ck作为所述预分频电路的输入时钟输入端,以接入所述输入时钟;

17、第一tspc d触发器的负极输出端qn、第一tspc d触发器的数据端d、所述场效应管q1的漏极以及第二tspc d触发器的时钟端ck共同作为所述预分频电路的第1个子计数信号输出端,以输出所述第1个子计数信号;

18、所述反相器的输入端作为所述预分频电路的第2控制字输入端,以接入所述第2控制字;所述反相器的输出端与传输门的输入端连接,所述传输门的正极控制端和所述场效应管q1的栅极共同作为所述预分频电路的输出时钟输入端,以接入所述输出时钟;所述传输门的负极控制端作为所述预分频电路的反相输出时钟输入端,以接入反相后的所述输出时钟;

19、所述第二tspc d触发器的负极输出端qn、所述传输门的输出端以及所述第二tspcd触发器的数据端d共同作为所述预分频电路的的第2个子计数信号输出端,以输出所述第2个子计数信号。

20、在其中一个实施例中,所述清零触发电路包括:

21、或门,对n个所述子计数信号和第四数字信号进行或运算,以输出第一负极数字信号;所述第一负极数字信号作为所述清零信号;

22、第一触发器,根据所述输入时钟对所述第一负极数字信号进行触发,以输出第二负极数字信号和第二正极数字信号;

23、第二触发器,根据所述输入时钟对所述第二负极数字信号进行触发,以输所述第三负极数字信号和第三正极数字信号;

24、选择器,根据所述第1控制字选择输出所述第二正极数字信号或所述第三正极数字信号;

25、第三触发器,根据所述输入时钟对第二正极数字信号或所述第三正极数字信号进行触发,以输出所述输出时钟;

26、与非门,对所述第二负极数字信号、所述第三负极数字信号以及反相后的所述输出时钟进行与非运算,以输出所述第四数字信号。

27、在其中一个实施例中,所述第一触发器、所述第二触发器和所述第三触发器均为tspc d触发器。

28、本发明实施例还提供一种高速时钟芯片,所述高速时钟芯片包括上述的任意整数分频电路。

29、本发明实施例还提供一种通信芯片,所述通信芯片包括上述的任意整数分频电路。

30、本发明实施例与现有技术相比存在的有益效果是:一方面,由于d<0>为0时,输出时钟reload相比清零信号ab延迟3个输入时钟clkin的周期;d<0>为1时,输出时钟reload相比清零信号ab延迟4个输入时钟clkin的周期。因为d=20×d<0>+21×d<1>+22×d<2>+23×d<3>+…+2n-1×d<n-1>。且k=d<1>+21×d<2>+22×d<3>+…+2n-2×d<n-1>,则d=2*k+d<0>。当d<0>=1时,d=2*k+1,则分频比=计数数值+延迟周期数=(2*k+1)+4=d+4;当d<0>=0时,d=2*k,则分频比=计数数值+延迟周期数=(2*k+1)+3=2*k+4=d+4。因此所述任意整数分频电路的分频比为d+4,故可实现大于4的任意整数分频。另一方面,任意整数分频电路中,计数电路从计数数值对所述输入时钟进行递减计数以输出计数信号;计数数值为2k+1,k为d<1>+21×d<2>+22×d<3>+…+2n-2×d<n-1>,即:计数电路根据d<1>至d<n-1>进行递减计数,与相关的任意整数分频电路相比较,无需使用第1控制字d<0>进行二分频,第2控制字d<1>的频率远低于第1控制字d<0>信号的频率,故在给定的工艺条件下,突破了工作速度瓶颈,提高了工作频率,拓宽了在超高速系统中的应用。

- 还没有人留言评论。精彩留言会获得点赞!