半导体存储装置及包括其的电子系统的制作方法

本公开涉及半导体存储装置和包括该半导体存储装置的电子系统,更具体地,涉及具有共享一个源极/漏极区域的通道晶体管(pass transistors)的半导体存储装置和包括该半导体存储装置的电子系统。

背景技术:

1、随着信息通信装置变得多功能化,存储装置实现了大存储容量和高度集成。随着存储单元的尺寸为了高度集成而减小,存储装置中包括的用于操作和电连接目的的操作电路和/或布线结构变得更加复杂。因此,需要能够提高集成度并仍具有优异电特性的存储装置。

2、为了提高存储装置的集成度,可以增加相对于衬底垂直堆叠的字线的数目。因此,连接到字线的通道晶体管的数目也会增加,从而导致存储装置的尺寸增大以及存储装置特性的潜在劣化。

技术实现思路

1、本公开的各方面提供了一种具有改善的性能和可靠性的半导体存储装置。

2、本公开的各方面还提供了一种包括具有改善的性能和可靠性的半导体存储装置的电子系统。

3、然而,本公开的各方面不限于本文所描述的这些内容。通过参考下面给出的本公开的详细描述,本公开的上述和其他方面对于本公开所属领域的普通技术人员而言将变得更加明了。

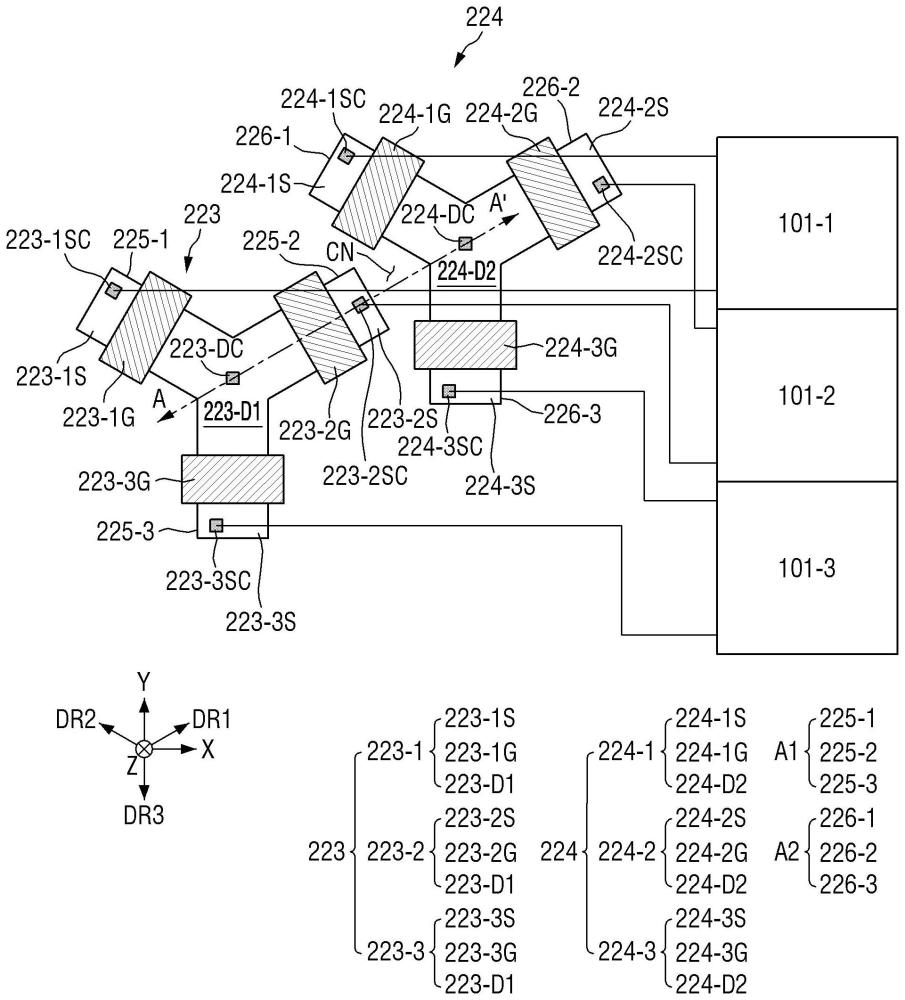

4、根据本公开的一个方面,一种半导体存储装置包括:衬底,所述衬底包括第一区域和第二区域,其中,所述第一区域包括外围电路区域,所述外围电路区域包括第一有源区域(far),并且所述第二区域包括存储单元块。所述far包括在第一方向上延伸的far第一延伸部、在第二方向上延伸的far第二延伸部和在第三方向上延伸的far第三延伸部,并且所述far第一延伸部、所述far第二延伸部和所述far第三延伸部相对于彼此形成大于90度的相应角度。所述半导体存储装置还包括第一通道晶体管电路,所述第一通道晶体管电路被配置为传输驱动信号以使工作电压被施加到所述存储单元块,其中,所述第一通道晶体管电路包括:位于所述far第一延伸部上的far第一栅极结构、位于所述far第二延伸部上的far第二栅极结构、位于所述far第三延伸部上的far第三栅极结构、以及位于所述far第一栅极结构、所述far第二栅极结构和所述far第三栅极结构之间的第一共享源极/漏极。

5、一方面,所述存储单元块包括第一存储单元块、第二存储单元块、第三存储单元块,并且其中所述第一通道晶体管电路还包括第一通道晶体管、第二通道晶体管和第三通道晶体管,所述第一通道晶体管、所述第二通道晶体管和所述第三通道晶体管被配置为传输所述驱动信号以使所述工作电压分别被施加到所述第一存储单元块、所述第二存储单元块和所述第三存储单元块。

6、一方面,所述第一通道晶体管电路还包括位于所述far第一延伸部上的第一单独源极/漏极、位于所述far第二延伸部上的第二单独源极/漏极以及位于所述far第三延伸部上的第三单独源极/漏极。

7、一方面,所述far呈y形。

8、一方面,所述半导体存储装置还包括:第二有源区域(sar),所述sar被限定在所述衬底的所述第一区域中并且与所述far间隔开;以及第二通道晶体管电路,所述第二通道晶体管电路位于所述sar中并且与所述第一通道晶体管电路间隔开,其中,所述sar包括在所述第一方向上延伸的sar第一延伸部、在所述第二方向上延伸的sar第二延伸部和在所述第三方向上延伸的sar第三延伸部,所述第二通道晶体管电路包括位于所述sar第一延伸部上的sar第一栅极结构、位于所述sar第二延伸部上的sar第二栅极结构、位于所述sar第三延伸部上的sar第三栅极结构以及位于所述sar第一栅极结构、所述sar第二栅极结构和所述sar第三栅极结构之间的第二共享源极/漏极。

9、一方面,所述far的中心限定凹部,并且所述sar第一延伸部、所述sar第二延伸部和所述sar第三延伸部之一对应于所述凹部。

10、一方面,所述衬底在第一水平方向和与所述第一水平方向正交的第二水平方向上延伸,并且所述第一共享源极/漏极和所述第二共享源极/漏极在所述第一方向上对齐。

11、一方面,所述半导体存储装置还包括:第三有源区域(tar),所述tar被限定在所述衬底的所述第一区域中并且与所述far和所述sar间隔开;以及第三通道晶体管电路,所述第三通道晶体管电路位于所述tar中并且与所述第一通道晶体管电路和所述第二通道晶体管电路间隔开,其中,所述tar包括在所述第一方向上延伸的tar第一延伸部、在所述第二方向上延伸的tar第二延伸部和在所述第三方向上延伸的tar第三延伸部,并且所述第三通道晶体管电路包括位于所述tar第一延伸部上的tar第一栅极结构、位于所述tar第二延伸部上的tar第二栅极结构、位于所述tar第三延伸部上的tar第三栅极结构以及第三共享源极/漏极。

12、一方面,所述far和所述sar呈y形并且是并排布置的,所述far和所述tar呈y形并且是并排布置的,并且所述第一共享源极/漏极与所述第二共享源极/漏极之间的距离、所述第二共享源极/漏极与所述第三共享源极/漏极之间的距离以及所述第一共享源极/漏极与所述第三共享源极/漏极之间的距离相等。

13、一方面,所述far和所述sar呈y形并且相对于彼此是倒置的,所述far和所述tar呈y形并且相对于彼此是倒置的,并且所述第一共享源极/漏极与所述第二共享源极/漏极之间的距离和所述第一共享源极/漏极与所述第三共享源极/漏极之间的距离相等。

14、一方面,所述半导体存储装置还包括:第四有源区域(foar),所述foar被限定在所述衬底的所述第一区域中并且与所述far、所述sar和所述tar间隔开;以及第四通道晶体管电路,所述第四通道晶体管电路位于所述foar中并且与所述第一通道晶体管电路、所述第二通道晶体管电路和所述第三通道晶体管电路间隔开,其中,所述foar包括在所述第一方向上延伸的foar第一延伸部、在所述第二方向上延伸的foar第二延伸部和在所述第三方向上延伸的foar第三延伸部,并且所述第四通道晶体管电路包括位于所述foar第一延伸部上的foar第一栅极结构、位于所述foar第二延伸部上的foar第二栅极结构、位于所述foar第三延伸部上的foar第三栅极结构、以及第四共享源极/漏极。

15、一方面,所述far和所述sar呈y形并且是并排布置的,所述far和所述foar呈y形并且是并排布置的,所述第一共享源极/漏极与所述第二共享源极/漏极之间的第一距离和所述第一共享源极/漏极与所述第四共享源极/漏极之间的第二距离相等,并且所述第一共享源极/漏极与所述第三共享源极/漏极之间的第三距离不同于所述第一距离或所述第二距离。

16、一方面,所述far和所述sar呈y形并且相对于彼此是倒置的,所述tar和所述foar呈y形并且相对于彼此是倒置的,所述sar和所述tar呈y形并且是并排布置的,所述far和所述foar呈y形并且是并排布置的,并且所述第一共享源极/漏极与所述第二共享源极/漏极之间的距离、所述第二共享源极/漏极与所述第三共享源极/漏极之间的距离、所述第三共享源极/漏极与所述第四共享源极/漏极之间的距离以及所述第一共享源极/漏极与所述第四共享源极/漏极之间的距离相等。

17、根据本公开的另一方面,一种半导体存储装置包括:第一衬底,所述第一衬底包括在第一水平方向和与所述第一水平方向正交的第二水平方向上延伸的第一表面,以及位于所述第一表面上的存储单元区域;以及第二衬底,所述第二衬底包括位于所述第一衬底下方的第二表面和位于所述第二表面上的第一外围电路区域,所述第一外围电路区域被配置为接收块选择信号并且将驱动信号传输到所述存储单元区域,其中,所述第一外围电路区域包括第一有源区域,所述第一有源区域包括在第一方向上延伸的第一栅极结构、在第二方向上延伸的第二栅极结构、在第三方向上延伸的第三栅极结构以及在所述第一栅极结构、所述第二栅极结构和所述第三栅极结构之间的第一共享源极/漏极,并且其中,所述第一方向、所述第二方向和所述第三方向彼此不平行并且所述第一栅极结构、所述第二栅极结构和所述第三栅极结构彼此间隔开。

18、一方面,所述第一有源区域包括第一延伸部、第二延伸部和第三延伸部,所述第一延伸部、所述第二延伸部和所述第三延伸部相对于彼此形成120度的相应角度。一方面,所述第一外围电路区域和所述存储单元区域通过接合位于所述第一衬底上的第一接合焊盘和位于所述第二衬底上的第二接合焊盘而连接,并且其中,所述第一衬底的所述第一表面和所述第二衬底的所述第二表面彼此面对。

19、一方面,所述存储单元区域包括在所述第一水平方向上延伸并且在垂直方向上堆叠的栅电极层,并且所述存储单元区域包括在所述垂直方向上延伸并且穿透所述栅电极层的沟道结构,并且每个所述沟道结构包括顺序堆叠在沟道孔的侧壁上的信息存储膜、半导体图案和可变电阻膜,所述沟道孔穿透所述栅电极层。

20、一方面,所述半导体存储装置还包括:第二外围电路区域,所述第二外围电路区域位于所述第二衬底上并且与所述第一外围电路区域间隔开,所述第二外围电路区域包括:第二有源区域,所述第二有源区域包括在所述第一方向上延伸的第四栅极结构、在所述第二方向上延伸的第五栅极结构和在所述第三方向上延伸的第六栅极结构,所述第四栅极结构、所述第五栅极结构和所述第六栅极结构彼此间隔开;第二共享源极/漏极,所述第二共享源极/漏极位于所述第四栅极结构、所述第五栅极结构和所述第六栅极结构之间,并且所述第一共享源极/漏极和所述第二共享源极/漏极在所述第一方向上对齐。一方面,所述第一有源区域和所述第二有源区域呈y形并且是并排布置的。

21、根据本公开的另一方面,一种电子系统,包括:主基板;半导体存储装置,所述半导体存储装置位于所述主基板上并且包括具有外围电路的第一衬底和具有存储单元的第二衬底;以及控制器,所述控制器位于所述主基板上并且电连接到所述半导体存储装置,其中,所述半导体存储装置包括被限定在所述第一衬底上的有源区域,所述有源区域包括在第一方向上延伸的第一延伸部、在第二方向上延伸的第二延伸部和在第三方向上延伸的第三延伸部,所述第一延伸部、所述第二延伸部和所述第三延伸部相对于彼此形成大于90度的相应角度,所述有源区域包括通道晶体管电路,所述通道晶体管电路被配置为传输驱动信号以使工作电压被施加到所述存储单元,并且所述通道晶体管电路包括位于所述第一延伸部上的第一栅极结构、位于所述第二延伸部上的第二栅极结构、位于所述第三延伸部上的第三栅极结构以及位于所述第一栅极结构、所述第二栅极结构和所述第三栅极结构之间的共享源极/漏极。

22、应注意的是,本公开的效果不限于上述效果,本公开的其他效果可从以下说明中看出。

- 还没有人留言评论。精彩留言会获得点赞!