浮栅存储器及其制备方法以及逻辑器件

本发明属于存储器领域,尤其涉及一种顶栅调控的浮栅存储器及其制备方法以及包含浮栅存储器的逻辑器件。

背景技术:

1、浮栅存储器,也称为浮栅晶体管,它作为非易失性存储器家族的一员,在集成电路中具有广泛的应用。参见图1所示的现有技术的浮栅存储器的结构示意图,其包括衬底7和依次布置在衬底7上的沟道层5、隧穿绝缘层4、浮栅层3、阻挡绝缘层2和控制栅(顶栅)1,以及布置在沟道层5之上的隧穿绝缘层4两侧的源极6和漏极8。现有技术的浮栅存储器的存储机制主要是:在控制栅1上施加电压脉冲时,控制栅1和源漏极之间的电压差使得沟道层5中的载流子经过隧穿绝缘层4隧穿到浮栅层3中并且被阻挡绝缘层2阻挡,从而在浮栅层3中存储大量的载流子;当撤去电压脉冲后,浮栅层3产生的局域电场调控沟道层5的半导体材料。例如,对于n型掺杂的半导体(如磷、砷等),当在控制栅1上施加正电压脉冲时,沟道层5中的电子经过隧穿绝缘层4隧穿到浮栅层3中,从而在浮栅层3中存储大量的电子,当撤去电压脉冲后,浮栅层3中的电子对沟道层5进行静电调控,使半导体的上表面呈现耗尽状态,此时沟道层5处于关态,关态是指沟道层5的电流处于关断状态,即电流不导通状态;当在控制栅1上施加负电压脉冲时,沟道层5中的空穴经过隧穿绝缘层4隧穿到浮栅层3中,从而在浮栅层3中存储大量的空穴,当撤去电压脉冲后,浮栅层3中的空穴对沟道层5进行静电调控,半导体表面呈现积累状态,此时沟道层5处于开态,开态是指沟道层5的电流处于开启状态,即电流导通状态。虽然浮栅存储器可以长时间存储数据,且编程速度相对较快,但对于同一种掺杂类型的半导体而言,在施加正/负脉冲电压后,沟道电流统一达到低/高态,这样无法实现有效的逻辑状态,不利于其在集成电路中的应用。技术人员试图通过改变不同类型的杂质掺杂来实现不同导电类型的阱,但这使得工艺更加繁琐复杂。

技术实现思路

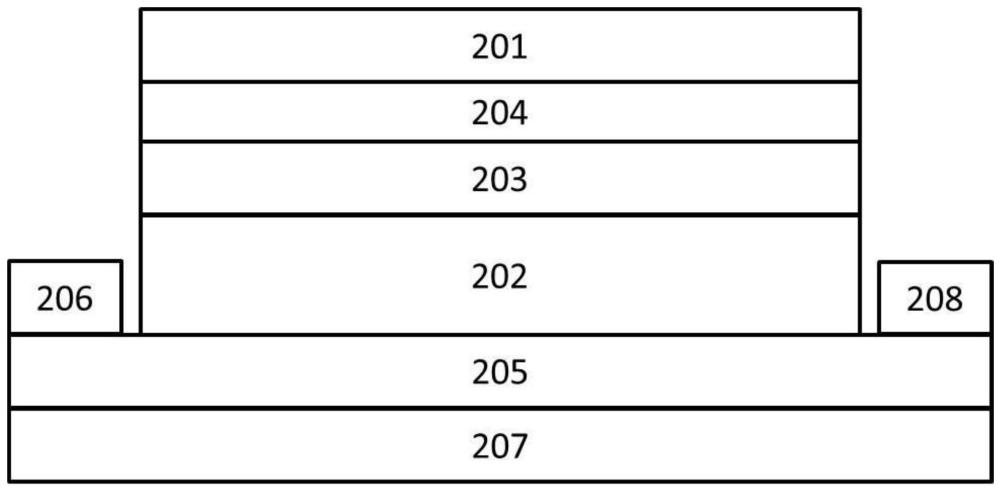

1、因此,本发明的目的在于克服上述现有技术的缺陷,提供一种浮栅存储器,包括衬底层和依次设置在所述衬底层之上的沟道层、阻挡绝缘层、浮栅层、隧穿绝缘层和控制栅,还包括设置在所述沟道层之上的所述阻挡绝缘层两侧的源电极和漏电极,其中,所述阻挡绝缘层的厚度大于所述隧穿绝缘层的厚度。

2、根据本发明的浮栅存储器,优选地,所述衬底层为si。

3、根据本发明的浮栅存储器,优选地,所述沟道层为mos2二维材料或者硅半导体。

4、根据本发明的浮栅存储器,优选地,所述阻挡层或所述隧穿层为hbn二维材料或sio2。

5、根据本发明的浮栅存储器,优选地,所述浮栅层为mlg二维材料或者多晶硅。

6、根据本发明的浮栅存储器,优选地,所述控制栅、所述源极和所述漏极为金属。

7、根据本发明的浮栅存储器,优选地,所述控制栅、所述源极和所述漏极为cr/au双层结构。

8、根据本发明的浮栅存储器,优选地,所述控制栅的面积小于所述浮栅层的面积。

9、本发明还提供了一种浮栅存储器的制备方法,包括如下步骤:

10、在衬底上制备沟道层;

11、在所述沟道层上依次堆垛阻挡绝缘层、浮栅层和隧穿绝缘层;

12、在所述隧穿绝缘层上制备控制栅;以及

13、在所述沟道层之上所述阻挡绝缘层的两侧分别制备源极和漏极。

14、本发明还提供了了一种逻辑器件,其包括衬底和设置在所述衬底之上的沟道层,以及

15、依次设置在所述沟道层的第一区域之上的第一阻挡绝缘层、第一浮栅层、第一隧穿绝缘层和第一控制栅,所述第一阻挡绝缘层的厚度大于所述第一隧穿绝缘层的厚度;

16、依次设置在所述沟道层的第二区域之上的第二隧穿绝缘层、第二浮栅层、第二阻挡绝缘层和第二控制栅,所述第二阻挡绝缘层的厚度大于所述第二隧穿绝缘层的厚度;

17、分别设置在所述沟道层之上所述第一区域和所述第二区域外侧的源极和漏极;以及

18、设置在所述沟道层之上所述第一区域和所述第二区域之间的输出端。

19、与现有技术相比,本发明的浮栅存储器基于二维半导体材料的堆垛,通过顶栅调控的浮栅存储器这一结构设计,实现了与传统硅基浮栅存储器工艺相互补的新型浮栅存储器,从而使利用单一掺杂的半导体制作的浮栅存储器实现逻辑功能成为可能。

技术特征:

1.一种浮栅存储器,包括衬底层和依次设置在所述衬底层之上的沟道层、阻挡绝缘层、浮栅层、隧穿绝缘层和控制栅,还包括设置在所述沟道层之上的所述阻挡绝缘层两侧的源电极和漏电极,其中,所述阻挡绝缘层的厚度大于所述隧穿绝缘层的厚度。

2.根据权利要求1所述的浮栅存储器,其中,所述衬底层为si。

3.根据权利要求1所述的浮栅存储器,其中,所述沟道层为mos2二维材料或者硅半导体。

4.根据权利要求1所述的浮栅存储器,其中,所述阻挡层或所述隧穿层为hbn二维材料或sio2。

5.根据权利要求1所述的浮栅存储器,其中,所述浮栅层为mlg二维材料或者多晶硅。

6.根据权利要求1所述的浮栅存储器,其中,所述控制栅、所述源极和所述漏极为金属。

7.根据权利要求6所述的浮栅存储器,其中,所述控制栅、所述源极和所述漏极为cr/au双层结构。

8.根据权利要求1-7中任一项所述的浮栅存储器,其中,所述控制栅的面积小于所述浮栅层的面积。

9.一种根据权利要求1-8中任一项所述的浮栅存储器的制备方法,包括如下步骤:

10.一种逻辑器件,其包括衬底和设置在所述衬底之上的沟道层,以及

技术总结

本发明提供了一种浮栅存储器,包括衬底层和依次设置在所述衬底层之上的沟道层、阻挡绝缘层、浮栅层、隧穿绝缘层和控制栅,还包括设置在所述沟道层之上的所述阻挡绝缘层两侧的源电极和漏电极,其中,所述阻挡绝缘层的厚度大于所述隧穿绝缘层的厚度。

技术研发人员:王昊,郭辉,杨海涛,高鸿钧

受保护的技术使用者:中国科学院物理研究所

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!