半导体元件搭载用封装体基板的制造方法和半导体元件安装基板的制造方法与流程

本发明涉及半导体元件搭载用封装体基板的制造方法和半导体元件安装基板的制造方法。

背景技术:

1、近年来,电子设备的小型化、轻量化、多功能化进一步推进。随着电子设备的小型化,封装体尺寸的进一步的小型化的要求变强烈。作为应对封装体尺寸的小型化的方式,提出了与半导体芯片大致等同尺寸的、所谓芯片尺寸封装体(csp;chip size/scalepackage)。其为在安装区域内而不是在半导体芯片的周边部具有与外部布线基板的连接部的封装体。作为具体例,有:使带凸块的聚酰亚胺薄膜粘接在半导体芯片的表面,通过芯片与金引线实现了电连接后,灌封密封环氧树脂而成的封装体(参见下述非专利文献1);在临时基板上形成半导体芯片、和在相当于与外部布线基板的连接部的位置形成金属凸块,将半导体芯片进行倒装焊接(face down bonding)后,在临时基板上进行传递模塑而成的封装体(参见下述非专利文献2)等。

2、另一方面,关于微细布线的形成,如下的半加成法备受关注:事先在基材表面形成较薄的镀层,在其上形成抗蚀镀层,利用电镀将导体形成为所需的厚度,之后,剥离抗蚀剂后,将前述薄的镀层利用软蚀刻去除。另外,还研究了如下方法:形成由加热·加压压制法形成的带载体的可剥离铜箔代替薄的镀层,然后将载体去除,形成薄铜箔层。

3、另外,为了提供布线密度优异、且生产效率优异、连接可靠性高的半导体元件搭载用封装体基板的制造方法,提出了如下方法:使用电路形成用支撑基板,所述电路形成用支撑基板是在极薄铜箔的厚度为1μm~5μm的带载体铜箔的极薄铜箔的载体铜箔面上设置绝缘树脂而成的,利用电镀铜等在其上制作布线导体,之后将带载体铜箔的支撑基板剥离,制作半导体元件搭载用封装体基板(例如参见下述专利文献1)。

4、现有技术文献

5、专利文献

6、专利文献1:日本特开2005-101137号公报

7、非专利文献

8、非专利文献1:nikkei materials&technology)94.4、no.140、p18-19

9、非专利文献2:smallest flip-chip-like package csp;the second vlsipackkging workshop of japan、p46-50、1994

技术实现思路

1、发明要解决的问题

2、对于上述专利文献1的半导体元件搭载用封装体基板的制造方法中使用的利用了带载体铜箔的极薄铜箔的电路形成用支撑基板,通常大多数情况下,在载体铜箔与极薄铜箔之间(界面)设有极薄的粘接层。然而,通常,该粘接层为几十nm的厚度,耐化学药品性弱。例如,制作多层结构的封装体基板时,为了层间连接而有时利用钻头、激光开设通孔等孔。此时,为了将残留于孔的内部等的树脂(胶渣)去除,使用包含高锰酸钠等的除胶渣液,进行去除胶渣的除胶渣处理。然而,如上述在使用利用了带载体铜箔的极薄铜箔的电路形成用支撑基板的情况下,化学溶液(除胶渣液)有时渗透到位于载体铜箔与极薄铜箔之间的粘接层中。如此,如果化学溶液渗透到载体铜箔与极薄铜箔之间的粘接层中,则载体铜箔与极薄铜箔的界面的粘接强度会降低。该载体铜箔与极薄铜箔的界面处的粘接强度的降低对生产效率造成影响。另外,引起了化学溶液的渗透的部分如果涉及成为制品的部分,则极薄铜箔被化学溶液腐蚀,有时成为制品不良的原因。进而,由于发生化学溶液的侵入,从而引起后续工序中使用的液体、装置的污染,也成为装置工作不良的原因。

3、另外,以往,为了防止该化学溶液的侵入,大多进行如下方式:在制作封装体基板时,在电路形成用支撑基板上,将带载体铜箔的极薄铜箔的侧面以绝缘树脂覆盖的方式构成。然而,为了覆盖带载体铜箔的极薄铜箔的侧面,必须减小原始的电路形成用支撑基板(拆卸芯(detach core)),还存在妨碍设计的自由度的问题。

4、另外,从操作性等观点出发,还设想了期望在半导体元件搭载用封装体基板的制造方法的工序内,将半导体元件搭载于基板的情况。然而,在以往方法的工序内想要将半导体元件搭载于基板时,在焊料等进行回流焊时,在金属层与极薄铜箔之间等大多产生所谓膨胀,寻求开发出半导体元件搭载用封装体基板的制造方法的工序内也能将半导体元件搭载于基板的方式。

5、为了解决上述课题,本发明的目的在于,提供:生产效率良好、设计的自由度高的半导体元件搭载用封装体基板的制造方法和半导体元件安装基板的制造方法。

6、用于解决问题的方案

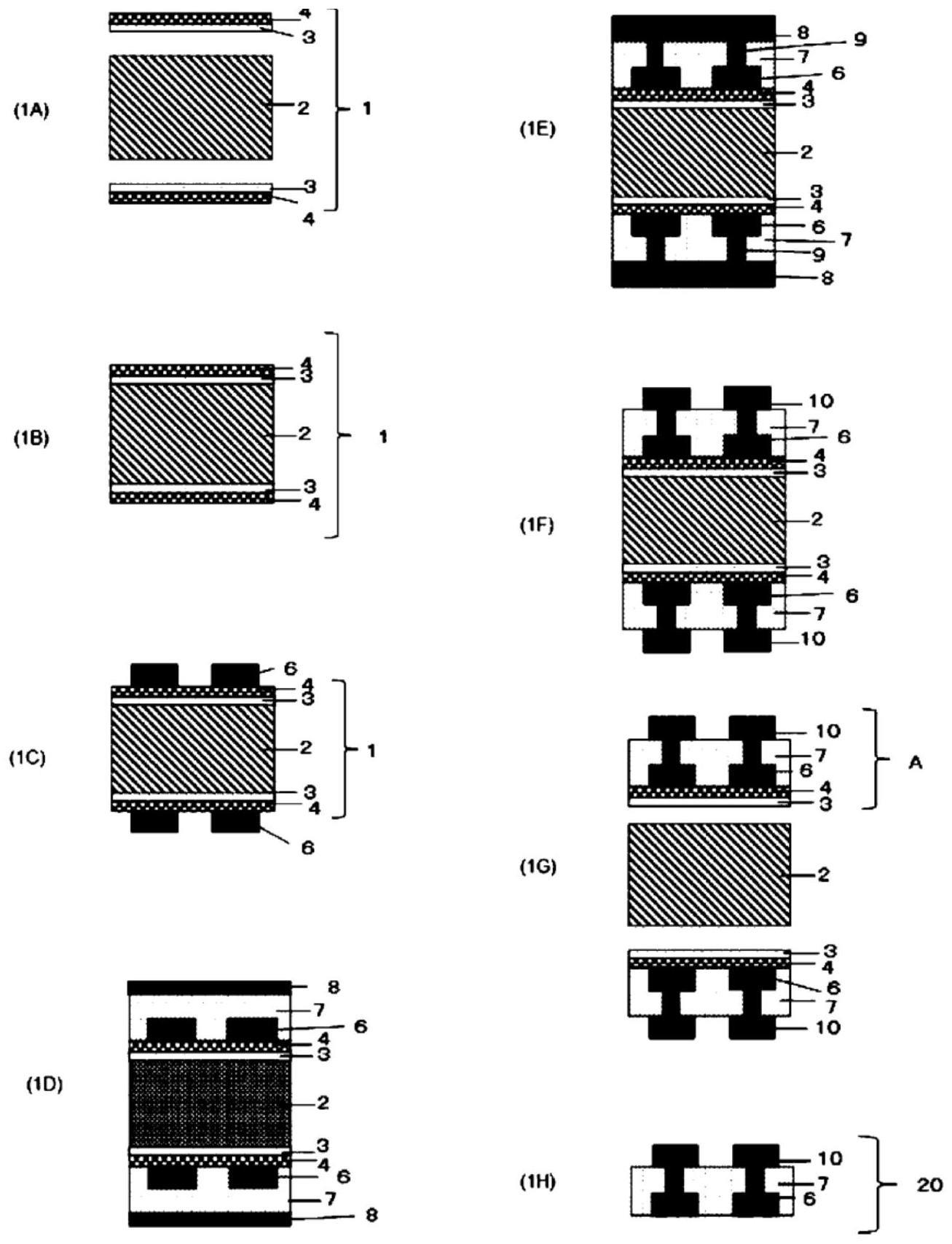

7、<1>一种半导体元件搭载用封装体基板的制造方法,其包括如下工序:

8、基板形成工序(a),形成依次含有第1绝缘树脂层、至少包含硅化合物的脱模层和厚度为1μm~5μm的极薄铜箔的电路形成用支撑基板;

9、第1布线导体形成工序(b),在前述电路形成用支撑基板的前述极薄铜箔上通过图形电镀铜形成第1布线导体;

10、层叠工序(c),以与前述第1布线导体接触的方式配置第2绝缘树脂层,将前述第2绝缘树脂层进行加热加压并层叠;

11、第2布线导体形成工序(d),在前述第2绝缘树脂层中形成到达前述第1布线导体的非贯通孔,使前述非贯通孔的内壁通过电镀铜和/或化学镀铜连接,形成第2布线导体;

12、剥离工序(e),从形成有前述第1布线导体和前述第2布线导体的电路形成用支撑基板剥离前述第1绝缘树脂层;和,

13、去除工序(f),将前述脱模层和/或前述极薄铜箔去除。

14、<2>根据前述<1>所述的半导体元件搭载用封装体基板的制造方法,其中,前述第1布线导体形成工序(b)包括如下工序:

15、工序(b-1),在前述极薄铜箔上层压镀覆用抗蚀剂;

16、工序(b-2),通过光刻法在前述镀覆用抗蚀剂上形成布线电路图案;

17、工序(b-3),在形成有前述布线电路图案的前述极薄铜箔上通过图形电镀铜形成前述第1布线导体;和,

18、工序(b-4),将前述镀覆用抗蚀剂去除。

19、<3>根据前述<1>或<2>所述的半导体元件搭载用封装体基板的制造方法,其中,前述层叠工序(c)包括如下工序:

20、工序(c-1),对前述第1布线导体表面实施粗糙化处理;和,

21、工序(c-2),将前述第2绝缘树脂层以其与实施了前述粗糙化处理的前述第1布线导体接触的方式配置,在前述第2绝缘树脂层上进一步配置金属层,并进行加热加压,将前述第2绝缘树脂层与前述金属层层叠。

22、<4>根据前述<1>~<3>中任一项所述的半导体元件搭载用封装体基板的制造方法,其中,前述第2布线导体形成工序(d)包括如下工序:

23、工序(d-1),在前述第2绝缘树脂层中形成到达前述第1布线导体的非贯通孔;

24、工序(d-2),使前述非贯通孔的内壁通过电镀铜和/或化学镀铜连接;和,

25、工序(d-3),以减成法或半加成法形成前述第2布线导体。

26、<5>根据前述<1>~<4>中任一项所述的半导体元件搭载用封装体基板的制造方法,其中,前述第2布线导体形成工序(d)中,对于形成有前述第1布线导体和前述第2布线导体的电路形成用支撑基板进而重复进行前述层叠工序(c)和前述第2布线导体形成工序(d),制造具有积层结构的半导体元件搭载用封装体基板。

27、<6>根据前述<1>~<5>中任一项所述的半导体元件搭载用封装体基板的制造方法,其中,前述第1绝缘树脂层的厚度为0.02mm~2.0mm。

28、<7>根据前述<1>~<6>中任一项所述的半导体元件搭载用封装体基板的制造方法,其中,前述第2布线导体形成工序(d)中,由激光形成前述非贯通孔。

29、<8>根据前述<1>~<7>中任一项所述的半导体元件搭载用封装体基板的制造方法,其中,前述剥离工序(e)中,将前述第1绝缘树脂层以物理的方式剥离。

30、<9>根据前述<1>~<8>中任一项所述的半导体元件搭载用封装体基板的制造方法,其中,前述去除工序(f)中,用硫酸系或过氧化氢系蚀刻液去除前述脱模层和/或前述极薄铜箔。

31、<10>根据前述<1>~<9>中任一项所述的半导体元件搭载用封装体基板的制造方法,其中,前述基板形成工序(a)中,包括如下工序(a-1):以前述脱模层与前述第1绝缘树脂层接触的方式在前述第1绝缘树脂层上配置在厚度为1μm~20μm的铜箔上形成有前述脱模层的带脱模层的铜箔,之后对前述带脱模层的铜箔的前述铜箔部分实施蚀刻处理,形成前述极薄铜箔。

32、<11>根据前述<1>~<10>中任一项所述的半导体元件搭载用封装体基板的制造方法,其中,前述脱模层包含除有机硅化合物以外的前述硅化合物。

33、<12>根据前述<1>~<11>中任一项所述的半导体元件搭载用封装体基板的制造方法,其中,在前述第1绝缘树脂层上直接层叠前述脱模层。

34、<13>一种半导体元件安装基板的制造方法,其包括如下工序:

35、基板形成工序(a),形成依次含有第1绝缘树脂层、至少包含硅化合物的脱模层和厚度为1μm~5μm的极薄铜箔的电路形成用支撑基板;

36、第1布线导体形成工序(b),在前述电路形成用支撑基板的前述极薄铜箔上通过图形电镀铜形成第1布线导体;

37、层叠工序(c),以与前述第1布线导体接触的方式配置第2绝缘树脂层,将前述第2绝缘树脂层进行加热加压并层叠;

38、第2布线导体形成工序(d),在前述第2绝缘树脂层中形成到达前述第1布线导体的非贯通孔,使前述非贯通孔的内壁通过电镀铜和/或化学镀铜连接,形成第2布线导体;

39、半导体元件搭载工序(g),在前述第2布线导体上搭载半导体元件;

40、剥离工序(e),从前述第2布线导体上搭载有前述半导体元件的电路形成用支撑基板剥离前述第1绝缘树脂层;和,

41、去除工序(f),将前述脱模层和/或前述极薄铜箔去除。

42、<14>根据前述<13>所述的半导体元件安装基板的制造方法,其中,前述半导体元件搭载工序(g)中,借助接合材料在前述第2布线导体上搭载前述半导体元件。

43、<15>根据前述<13>或<14>所述的半导体元件安装基板的制造方法,其中,在前述第1绝缘树脂层上直接层叠前述脱模层。

44、发明的效果

45、根据本发明的半导体元件搭载用封装体基板的制造方法,可以提供:生产效率良好、设计的自由度高的半导体元件搭载用封装体基板的制造方法和半导体元件安装基板的制造方法。

- 还没有人留言评论。精彩留言会获得点赞!