具有触发定时控制和/或增益提升的比较器的制作方法

背景技术:

1、本发明涉及比较器设计,并且更具体地,涉及具有触发定时控制和/或增益提升的宽输入范围和低噪声比较器。

2、模数转换器(analog-to-digital converter,adc)广泛用于许多应用中。在这些adc中,比较器扮演重要角色。比较器是用于比较两个模拟输入信号并生成指示两个模拟输入信号的比较结果的模拟输出信号的电路。比较器可以被视为一位adc。在电源管理集成电路(power management integrated circuit,pmic)的应用中,输入电压范围比传统adc中的输入电压范围宽得多。典型的两级比较器和单级比较器由于在更宽输入电压范围下的更高偏移变化和更差噪声性能而不适合。

3、以典型的两级比较器为例,当输入电压电平为高且接近电源电压时,在第一级的输出具有最大增益的时刻,第二级由于其输入电压电平太高而不触发。一旦第二级开始触发,来自第一级的大增益消失,从而导致来自典型的两级比较器的更高偏移和不良噪声性能。

4、以典型的单级比较器为例,当输入电压电平为高且接近电源电压时,在第一子级的输出具有最大增益的时刻,第二子级由于其输入电压电平太低而不触发。一旦第二子级开始触发,第二子级的输入电压电平开始下降,并且第一子级的电流增益已经减小,从而导致来自典型的单级比较器的较高偏移和不良噪声性能。

5、因此,需要一种创新的比较器设计,其能够在整个宽输入范围内实现合适的偏移电平和合适的噪声电平。

技术实现思路

1、所要求保护的发明的目的之一是提供具有触发定时控制和/或增益提升的宽输入范围和低噪声比较器。

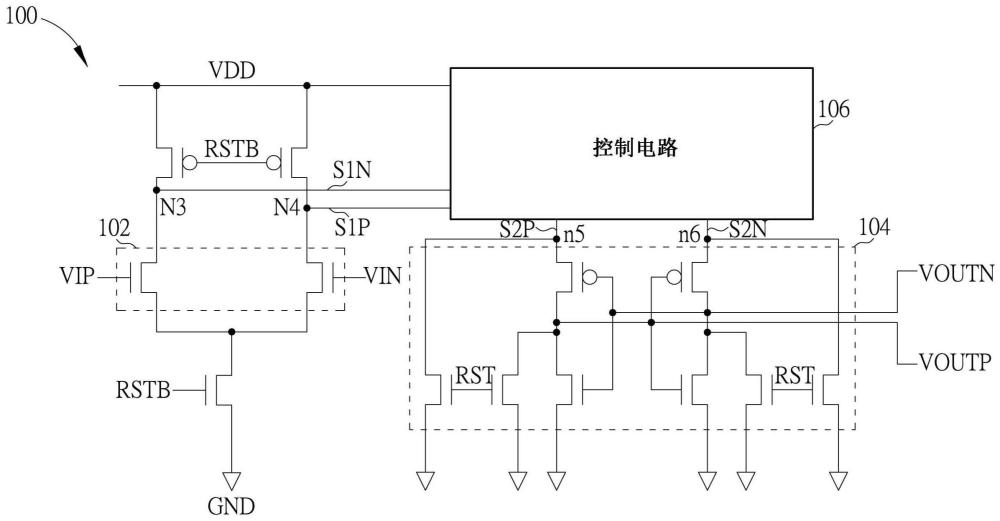

2、根据本发明的第一方面,公开了一种示例性多级比较器。示例性多级比较器包括第一级电路、第二级电路和控制电路。第一级电路被布置为接收多级比较器的输入信号,根据输入信号生成第一级输出信号,并在第一级电路的输出端口处输出第一级输出信号。第二级电路被布置为在第二级电路的输入端口处接收第二级输入信号,并执行第二级操作以生成多级比较器的输出信号。控制电路耦接在第一级电路的输出端口与第二级电路的输入端口之间,并且被布置为控制第二级操作的开始时间。

3、根据本发明的第二方面,公开了一种示例性单级比较器。示例性单级比较器包括第一子级电路、第二子级电路和控制电路。第一子级电路被布置为接收单级比较器的输入信号,根据输入信号生成第一子级输出信号,并在第一子级电路的输出端口处输出第一子级输出信号。第二子级电路被布置为在第二子级电路的输入端口处接收第二子级输入信号,并针对第二子级输入信号执行第二子级操作以生成单级比较器的输出信号。控制电路耦接在第一子级电路的输出端口与第二子级电路的输入端口之间,并且被布置为控制第二子级操作的开始时间。

4、在阅读了在各个附图中例示的优选实施方式的以下详细描述之后,本发明的这些和其他目的对于本领域的普通技术人员无疑将变得显而易见。

技术特征:

1.一种多级比较器,所述多级比较器包括:

2.根据权利要求1所述的多级比较器,其中,所述控制电路还被布置为接收时钟信号,并且至少参考所述时钟信号来控制所述第二级操作的所述开始时间。

3.根据权利要求2所述的多级比较器,其中,所述多级比较器在所述时钟信号的控制下以正常模式和复位模式中的一种模式工作;并且所述控制电路包括:

4.根据权利要求3所述的多级比较器,其中,所述触发信号发生器电路还包括:

5.根据权利要求3所述的多级比较器,其中,所述控制电路还包括:

6.根据权利要求2所述的多级比较器,其中,所述多级比较器在所述时钟信号的控制下以正常模式和复位模式中的一种模式工作;并且所述控制电路包括:

7.根据权利要求6所述的多级比较器,其中,所述控制电路还包括:

8.根据权利要求1所述的多级比较器,其中,所述第二级电路包括输入晶体管对,并且所述第二级电路的所述输入端口包括所述输入晶体管对的栅极端子。

9.根据权利要求1所述的多级比较器,其中,所述第二级电路包括输入晶体管对,并且所述第二级电路的所述输入端口包括所述输入晶体管对的非栅极端子。

10.根据权利要求1所述的多级比较器,其中,所述第一级电路包括用于接收所述多级比较器的所述输入信号的第一输入晶体管对,所述控制电路包括用于接收所述第一级输出信号的第二输入晶体管对,所述第一输入晶体管对和所述第二输入晶体管对中的一个输入晶体管对包括一对n型晶体管,并且所述第一输入晶体管对和所述第二输入晶体管对中的另一个输入晶体管对包括一对p型晶体管。

11.一种单级比较器,所述单级比较器包括:

12.根据权利要求11所述的单级比较器,其中,所述控制电路还被布置为接收时钟信号,并且参考所述时钟信号来控制所述第二子级操作的所述开始时间。

13.根据权利要求12所述的单级比较器,其中,所述单级比较器在所述时钟信号的控制下以正常模式和复位模式中的一种模式工作;并且所述控制电路包括:

14.根据权利要求13所述的单级比较器,其中,所述触发信号发生器电路还包括:

15.根据权利要求13所述的单级比较器,其中,所述控制电路还包括:

16.根据权利要求12所述的单级比较器,其中,所述单级比较器在所述时钟信号的控制下以正常模式和复位模式中的一种模式工作;并且所述控制电路包括:

17.根据权利要求16所述的单级比较器,其中,所述控制电路还包括:

18.根据权利要求11所述的单级比较器,其中,所述第二子级电路包括输入晶体管对,并且所述第二子级电路的所述输入端口包括所述输入晶体管对的栅极端子。

19.根据权利要求11所述的单级比较器,其中,所述第二子级电路包括输入晶体管对,并且所述第二子级电路的所述输入端口包括所述输入晶体管对的非栅极端子。

20.根据权利要求11所述的单级比较器,其中,所述第一子级电路包括用于接收所述单级比较器的所述输入信号的第一输入晶体管对,所述控制电路包括用于接收所述第一子级输出信号的第二输入晶体管对,所述第一输入晶体管对和所述第二输入晶体管对中的一个输入晶体管对包括一对n型晶体管,并且所述第一输入晶体管对和所述第二输入晶体管对中的另一个输入晶体管对包括一对p型晶体管。

技术总结

具有触发定时控制和/或增益提升的比较器。多级比较器包括第一级电路、第二级电路和控制电路。第一级电路接收多级比较器的输入信号,根据输入信号生成第一级输出信号,并在第一级电路的输出端口处输出第一级输出信号。第二级电路在第二级电路的输入端口处接收第二级输入信号,并且执行第二级操作以生成多级比较器的输出信号。控制电路耦接在第一级电路的输出端口与第二级电路的输入端口之间,并控制第二级操作的开始时间。

技术研发人员:黄文常

受保护的技术使用者:联发科技股份有限公司

技术研发日:

技术公布日:2024/4/22

- 还没有人留言评论。精彩留言会获得点赞!