一种阶梯矩阵码及其高并行低时延顺序统计量译码方法

本发明属于数字通信的,具体涉及一种阶梯矩阵码及其高并行低时延顺序统计量译码方法。

背景技术:

1、线性分组码的顺序统计量译码算法最早由fossorier和林舒在1995年提出,其可适用于任意线性分组码,并在不计复杂度前提下可获得最大似然译码算法性能。实际上,顺序统计量译码算法是一种典型的(近似)最大似然译码算法。随着超高可靠低延迟通信成为5g的三大应用场景之一,可提供超高可靠性能的顺序统计量译码受到了学界和工业界广泛的关注和讨论。

2、顺序统计量译码的基本思想是根据接收序列的可靠性对比特进行排序,之后通过高斯消元找到最可靠基底,并对最可靠基底进行错误图样搜索,通过重编码得到候选码字的列表,最后通过相关度量等选择最优码字输出,完成译码。顺序统计量译码具有众多优点,但其需要根据接收序列可靠性对每组接收序列执行高斯消元。然而,现有顺序统计量译码的高斯消元只能串行实现,这导致了不可避免的译码时延问题,严重限制了顺序统计量译码算法的实际应用。此外,传统顺序统计量译码算法的错误图样测试顺序是基于hamming重量实现的,并没有考虑实际接收中最可靠基底的软信息,这点也有待进一步优化提升。

技术实现思路

1、本发明的主要目的在于克服现有技术的缺点与不足,针对顺序统计量译码的串行高斯消元问题,提出一种阶梯矩阵码及其高并行低时延顺序统计量译码方法,通过特殊的阶梯形式生成矩阵或校验矩阵,获得上三角或下三角形式的置换矩阵,从而可实现全并行的高斯消元,并可结合局部约束顺序统计量译码等新型顺序统计量译码,极大降低重编码次数,实现低复杂低时延高性能译码。

2、为了达到上述目的,本发明采用以下技术方案:

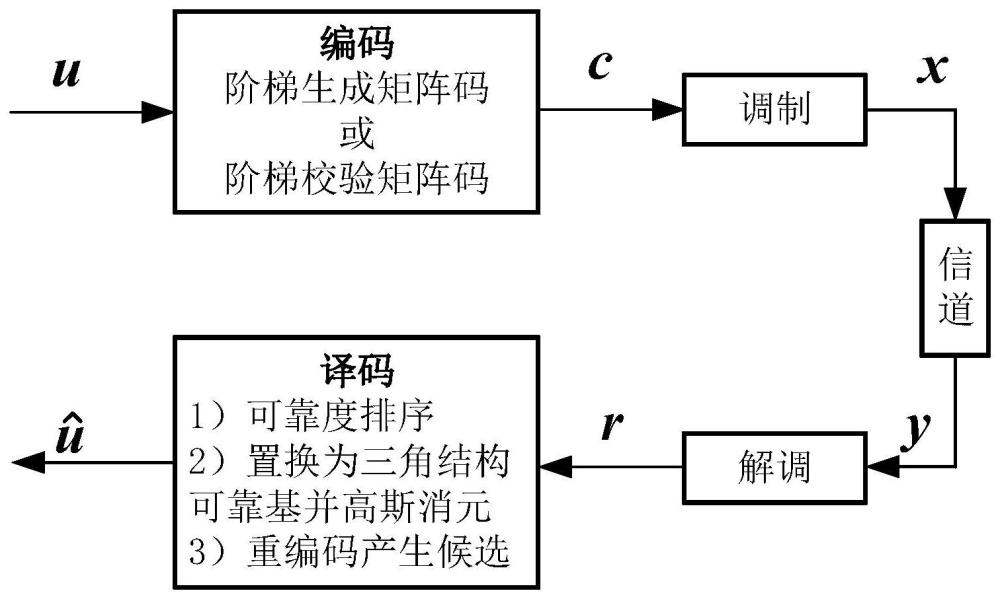

3、本发明公开了一种阶梯矩阵码及其高并行低时延顺序统计量译码方法,阶梯矩阵的描述为:阶梯矩阵第l行定义为gl=(hl,il,jl),其中hl的长度为∑0≤m<lwm的二元序列,il是长度为wl≥1的全1序列,jl是长度为n-∑0≤m≤lwm的全零序列;所述阶梯矩阵码从定义角度分为阶梯生成矩阵码和阶梯校验矩阵码,其中阶梯生成矩阵码的生成矩阵具有阶梯结构或经过行列交换后具有阶梯结构,k组w=(w0,w1,…,wk-1)构成了阶梯生成矩阵的轮廓,且wi≥1,∑wi=n;阶梯校验矩阵码的校验矩阵具有阶梯结构或经过行列交换后具有阶梯结构,n-k组w=(w0,w1,…,wn-k-1)构成了阶梯校验矩阵的轮廓,且wi≥1,∑wi=n;给定信源序列和阶梯矩阵码所述阶梯矩阵码及其高并行低时延顺序统计量译码方法的具体编译码过程如下:

4、(1)阶梯生成矩阵码的码字c属于阶梯生成矩阵gk×n的行生成空间,即阶梯校验矩阵码的码字c属于阶梯校验矩阵h(n-k)×n的零空间,即码字c满足h(n-k)×nct=0;

5、(2)接收端收到码字c对应的接收序列y并经解调后计算得到对应的对数似然比序列之后根据r判决得到码字对应的硬判决序列随后执行代表顺序统计量译码算法;定义|rj|为zj对应的可靠性,定义为测试错误图样,则为测试码字;设定参数δ,0≤δ≤n-k,译码的具体过程如下:

6、(2.1)对于阶梯生成矩阵码,基于比特的可靠性排序将生成矩阵进行列置换,得到gπ=[lk×k|mk×δ|nk×(n-k-δ)],其中l为上三角或下三角矩阵,对应于k个阶梯的k个可靠比特,mk×δ对应剩余比特中可靠的δ个比特,并对r,z,v和e做与π相应的置换,得到和而对于阶梯校验矩阵码,则基于比特的可靠性排序将校验矩阵进行行列置换,得到其中l为上三角或下三角矩阵,对应于n-k阶梯中的n-k-δ个不可靠比特,并对r,z,v和e做与πr相应的置换,得到和

7、(2.2)对于阶梯生成矩阵码,在gπ基础上执行传统或全部k行并行的高斯消元,得到其中ik×k为k阶单位矩阵;而对于阶梯校验矩阵码,则在πlhπr基础上执行传统的或全部n-k行并行的高斯消元处理,得到其中i(n-k-δ)×(n-k-δ)为n-k-δ阶单位矩阵,oδ×(n-k-δ)为全零子矩阵;

8、(2.3)基于或产生错误图样并执行重编码,得到候选码字列表v(i),并从中挑选最似然的或满足某种校验的候选码字作为译码输出,完成译码。

9、作为优先的技术方案,步骤(1)中,阶梯生成矩阵码的轮廓分布w=(w0,w1,…,wk-1)或阶梯校验矩阵码的轮廓分布w=(w0,w1,…,wn-k-1)是任意的,包括但不限于均分分配、非均匀分配、特殊的基于里德-穆勒码矩阵结构的分配和基于polar类码矩阵结构的分配。

10、作为优先的技术方案,步骤(1)中,阶梯码的产生方式是任意的,包括但不限于基于随机方式的构造和基于结构化方式的构造。

11、作为优先的技术方案,步骤(2)中,当δ=0时,采用的译码方案包括但不限于原始顺序统计量译码和顺序统计量译码的各种变种形式;当δ>0时采用基于局部约束的顺序统计量译码算法。

12、作为优先的技术方案,步骤(2.1)中,对于阶梯生成矩阵码,子矩阵l的形式是任意特殊三角形式的,包括但不限于上三角、下三角、准上三角或准下三角的形式,且子矩阵l的获得方式是任意的,典型的实现为要求置换后l的第i列对应于原始阶梯生成矩阵g的第i个阶梯中最可靠的比特,即第i列对应于zt(∑0≤m<iwm≤t<∑0≤m<(i+1)wm)中最可靠的比特,且子矩阵m的δ列对应于剩余n-k个比特中最可靠的。

13、作为优先的技术方案,步骤(2.1)中,对于阶梯校验矩阵码,子矩阵l的形式是任意三角形式的,包括但不限于上三角、下三角、准上三角或准下三角的形式,且子矩阵l的获得方式是任意的,典型的实现为要求置换后l的n-k-δ列对应于原始阶梯校验矩阵h的n-k级阶梯中最不可靠的n-k-δ个比特,且每级阶梯至多贡献1个。

14、作为优先的技术方案,骤(2.2)中,对于阶梯生成矩阵码包含的子矩阵l或阶梯校验矩阵码所包含的子矩阵u所执行的高斯消元是任意实现的,包括但不限于逐行串行的传统高斯消元、部分行并行的高斯消元或全部行并行的高斯消元。

15、作为优先的技术方案,步骤(2.3)中,产生候选码字的顺序是任意的,包括但不限于基于hamming重量的可靠基底错误图样产生顺序、基于软信息的可靠基底错误图样产生顺序或基于局部约束的可靠基底错误图样产生顺序。

16、本发明与现有技术相比,具有如下优点和有益效果:

17、(1)本发明提出的阶梯矩阵码及其高并行低时延顺序统计量译码方法,可以获得逼近有限码长界的性能,尤其是在中高信噪比区域,基于优化的候选码字列表顺序和提前终止设计,可获得较低的重编码次数,从而实现低复杂、低时延、高可靠译码。

18、(2)本发明译码设计精妙,基于特殊的阶梯生成矩阵或阶梯校验矩阵,并结合特殊的可靠基底选取,使得置换生成矩阵或置换校验矩阵具有上三角或下三角结构,从而可实现全并行高斯消元,极大的降低了高斯消元部分所需的时延。

19、(3)本发明译码可选择多样,其中引入的参数δ,当δ=0时对应于传统的顺序统计量译码及其变种,当δ>0时对应于局部约束的顺序统计量译码。局部约束的顺序统计量译码可以更为有效地优化候选码字列表,结合优选的提前终止设计,极大地降低重编码次数。

20、(4)本发明编码构造简单,易于实现,无论是随机的阶梯码构造还是结构化的阶梯码构造,均可以获得优异的性能。

- 还没有人留言评论。精彩留言会获得点赞!