一种防串扰芯片结构、制造方法及倒装焊芯片与流程

本申请属于量子芯片制备,特别是涉及一种防串扰芯片结构、制造方法及倒装焊芯片。

背景技术:

1、量子计算机是一类遵循量子力学规律进行高速数学和逻辑运算、存储及处理量子信息的物理装置。量子芯片是量子计算机的核心部件,量子芯片的实现有多种物理体系,如超导体系、半导体量子点、离子阱、金刚石空位、拓扑量子、光子等。

2、随着所设计的量子芯片中的量子比特数目不断增加,量子芯片的尺寸逐渐增大,封装盒也不断增大,与量子比特对应的控制线也逐渐增多;因此,在设计过程中,如何解决因上述发展变化给量子比特性能带来不良影响的问题,是需要解决的技术问题。

技术实现思路

1、为解决上述技术问题,本申请的目的是提供一种防串扰芯片结构,包括:

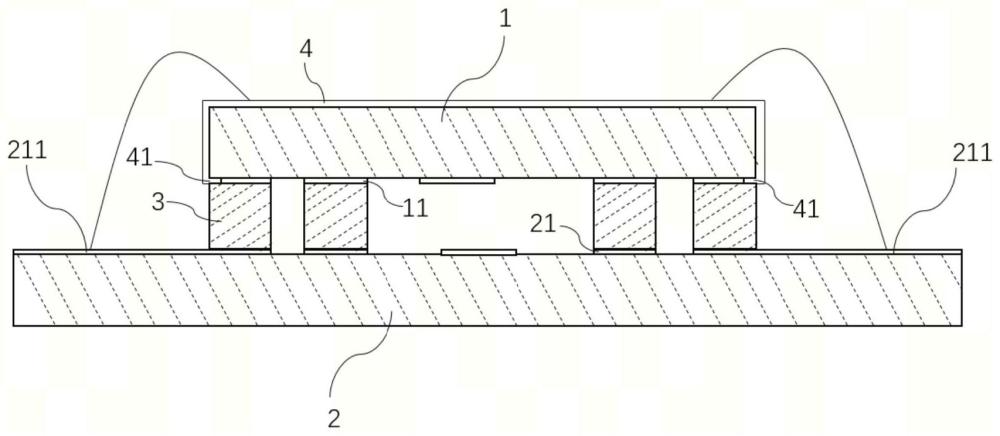

2、对置的第一芯片和第二芯片,所述第一芯片有第一表面和第二表面,所述第二芯片有第三表面,所述第一表面和所述第三表面相对设置并分别形成有第一电路层和第二电路层,且所述第一电路层形成有比特结构;

3、连接件,位于所述第一芯片和所述第二芯片之间,并电性连接所述第一电路层和所述第二电路层;以及

4、包覆所述第二表面的屏蔽层;

5、其中,所述屏蔽层、连接件和第二电路层共同形成用于容纳所述比特结构的信号屏蔽腔,从而降低所述屏蔽腔以外的外部信号对所述比特结构的影响。

6、优选的,所述第一电路层和所述第二电路层均为超导金属层;

7、所述第二电路层形成有直流控制线、微波控制线和谐振腔。

8、优选的,所述屏蔽层是超导薄膜。

9、优选的,所述第二电路层设有接地层,所述屏蔽层通过导线与所述接地层电性连接。

10、优选的,所述屏蔽层还包括位于所述第一表面的连接部;

11、所述连接件为铟柱,所述铟柱有多个,全部所述铟柱中的一部分靠近所述第一表面的边沿设置,且部分所述铟柱在所述第一表面与所述连接部电性连接;

12、或,所述连接件为铟墙,所述铟墙靠近所述第一表面的边沿设置,且所述铟墙在所述第一表面层表面与所述连接部电性连接。

13、优选的,所述第一芯片背离所述第一表面的表面设置有至少一个凹槽;

14、所述屏蔽层还包覆所述凹槽内壁。

15、本申请还提供一种防串扰芯片结构的制造方法,包括:

16、提供倒装焊芯片,有对置的第一芯片和第二芯片,所述第一芯片有第一表面和第二表面,所述第二芯片有第三表面,所述第一表面和所述第三表面相对设置,并在所述第一表面和所述第三表面之间设有连接件,所述第一表面和所述第三表面分别形成有通过所述连接件电性连接的第一电路层和第二电路层,且所述第一电路层形成有比特结构;

17、镀屏蔽层,使得所述屏蔽层覆盖所述第二表面,所述屏蔽层还具有延伸到第一表面的连接部,所述连接部与所述连接件靠近所述第一电路层的一端电性连接。

18、本申请还提供另一种防串扰芯片结构的制造方法,包括:

19、提供第一芯片和第二芯片,所述第一芯片有第一表面和第二表面,所述第二芯片有第三表面,第一表面和所述第三表面分别形成有第一电路层和第二电路层,且所述第一电路层形成有比特结构;

20、形成屏蔽层,所述屏蔽层覆盖所述第二表面,并且还包括在所述第一表面的连接部;

21、对置所述第一表面和所述第三表面,在所述第一表面和所述第三表面之间设置连接件,所述连接件分别与所述第一电路层和所述第二电路层电性连接,所述连接件靠近所述第一电路层的一端还与所述连接部电性连接。

22、优选的,所述制造方法还包括:

23、在所述第二电路层设置有接地层;

24、利用导线电性连接所述屏蔽层和所述接地层,使得所述屏蔽层接地,提供更好的屏蔽效果。

25、本申请还提供一种倒装焊芯片,包括:

26、前述任一项所述的防串扰芯片结构;

27、封装盒;

28、所述防串扰芯片结构设置在所述封装盒内。

29、有益效果:

30、在本申请示例的方案中,提供一种倒装焊芯片,其中一个芯片设置有比特结构,在有比特结构的芯片外围镀有超导薄膜,超导薄膜、连接件以及另一芯片的第二电路层共同形成一个容纳比特结构的屏蔽腔,以此来降低腔模频率以及信号串扰对比特结构的影响,完全或部分避免量子比特的性能降低。

技术特征:

1.一种防串扰芯片结构,其特征在于,包括:

2.根据权利要求1所述的防串扰芯片结构,其特征在于,所述第一电路层(11)和所述第二电路层(21)均为超导金属层;

3.根据权利要求2所述的防串扰芯片结构,其特征在于,所述屏蔽层(4)是超导薄膜。

4.根据权利要求3所述的防串扰芯片结构,其特征在于,所述第二电路层(21)设有接地层(211),所述屏蔽层(4)通过导线与所述接地层(211)电性连接。

5.根据权利要求1所述的防串扰芯片结构,其特征在于,

6.根据权利要求1-5任一项所述的防串扰芯片结构,其特征在于,所述第一芯片(1)背离所述第一表面的表面设置有至少一个凹槽(12);

7.一种防串扰芯片结构的制造方法,其特征在于,包括:

8.一种防串扰芯片结构的制造方法,其特征在于,包括:

9.根据权利要求7或8所述的制造方法,其特征在于,所述制造方法还包括:

10.一种倒装焊芯片,其特征在于,包括:

技术总结

本申请公开了一种防串扰芯片结构、制造方法及倒装焊芯片,属于量子比特芯片领域。一种防串扰芯片结构,包括:对置的第一芯片和第二芯片,第一芯片有第一表面和第二表面,第二芯片有第三表面,第一表面和第三表面相对设置并分别形成有第一电路层和第二电路层,且第一电路层形成有比特结构;连接件,位于第一芯片和第二芯片之间,并电性连接第一电路层和第二电路层;以及包覆第二表面的屏蔽层;其中,屏蔽层、连接件和第二电路层共同形成用于容纳比特结构的信号屏蔽腔,从而降低屏蔽腔以外的外部信号对比特结构的影响。通过上述方式,本发明能够解决腔膜频率和信号串扰降低量子比特性能的问题。

技术研发人员:请求不公布姓名,请求不公布姓名,贾志龙

受保护的技术使用者:本源量子计算科技(合肥)股份有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!