一种用于高速模数转换器的栅压自举开关电路

本技术属于集成电路,尤其涉及一种用于高速模数转换器的栅压自举开关电路。

背景技术:

1、模数转换器一般用于将连续的模拟信号转换为离散的数字信号,而转换得到的数字信号是用于提供给电子设备进行处理操作。随着通信技术和多媒体市场的快速发展,用户对于模数转换器的精度和速度要求也与日俱增。其中,流水线模数转换器(pipelineadc)凭借在低功耗、面积小的情况下实现高速度、高精度的模数转换的优势,在众多模数转换器中脱颖而出。然而,流水线模数转换器的转换精度受到其上栅压自举开关的非线性输出的限制,尤其在输入信号频率较高的应用场景中,现有的栅压自举开关难以满足新一代通信技术的需求。

技术实现思路

1、为了解决相关技术中存在的上述问题,本发明提供了一种用于高速模数转换器的栅压自举开关电路。本发明要解决的技术问题通过以下技术方案实现:

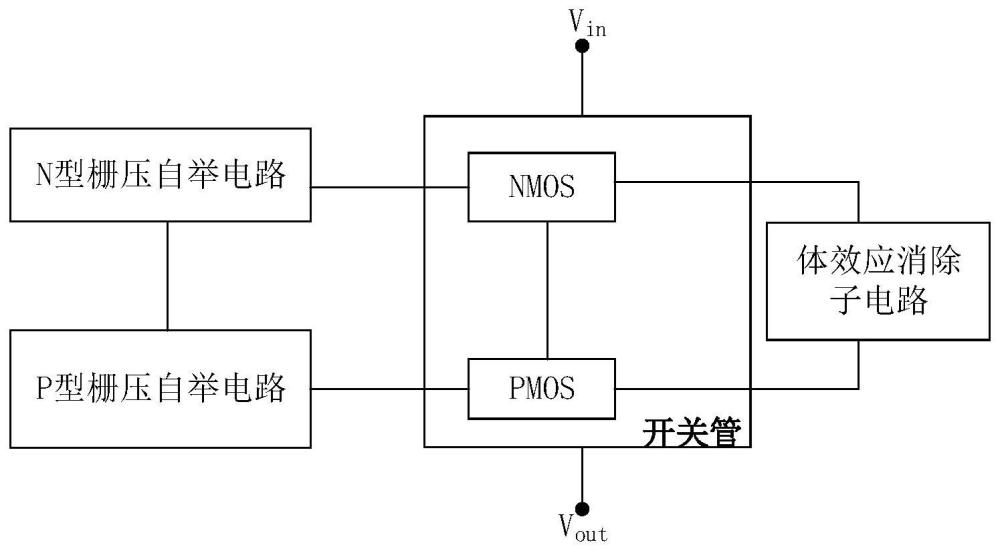

2、一种用于高速模数转换器的栅压自举开关电路,包括:开关管、p型栅压自举电路,以及n型栅压自举电路;其中所述开关管包括相互并联的nmos管和pmos管,所述开关管的一端连接至输入端vin,所述开关管的另一端连接至输出端vout;所述nmos管与所述n型栅压自举电路连接;所述pmos管与所述p型栅压自举电路连接;所述p型栅压自举电路和所述n型栅压自举电路之间相互连接;

3、其中,所述开关管用于消除所述pmos管和所述nmos管的沟道电荷注入效应、时钟馈通效应和体效应;所述n型栅压自举电路用于保持所述nmos管的导通电阻恒定;所述p型栅压自举电路用于保持所述pmos管的导通电阻恒定。

4、这里,所述nmos管包括mos管mns;所述pmos管包括mos管mps;其中,所述mps的源极和所述mns的漏极均连接至所述输入端vin;所述mps的漏极和所述mns的源极均连接至所述输出端vout。

5、这里,所述开关电路还包括:体效应消除子电路,用于消除所述开关管的体效应;其中,所述体效应消除子电路的第一端与所述mns的衬底连接,所述体效应消除子电路的第二端接入时钟clkb,所述体效应消除子电路的第三端与所述mps的衬底连接,所述体效应消除子电路的第四端接入时钟clk,所述体效应消除子电路的第五端接入电源电压vdd,所述体效应消除子电路的第六端连接所述输入端vin,所述体效应消除子电路的第七端接地;其中,所述时钟clkb输出的信号与所述时钟clk输出的控制信号相反。

6、这里,所述体效应消除子电路包括:mos管mn17、mp18、mn19和mp20;其中,所述mn17的源极分别与所述mn19的漏极、所述mns的衬底连接;所述mn19的源极接地;所述mn19的栅极接入所述时钟clkb;所述mp17的栅极与所述mns的栅极连接;所述mp18的漏极分别与所述mp20的源极、所述mps的衬底连接;所述mp20的漏极接入所述电源电压vdd;所述mp20的栅极接入所述时钟clk;所述mp18的栅极与所述mps的栅极连接;所述mn17的漏极与所述mns的漏极均连接至所述输入端vin;所述mp18的源极与所述mps的漏极连接。

7、这里,所述n型栅压自举电路包括:mos管mn1、mp1、mn3、mp3、mn5、mp5、mn7、mp7、mn9、mp9、mn11、mp11、mn13、mp13和mn15,以及电容cbn;其中,所述mp5的源极接入电源电压vdd,所述mp5的漏极分别与所述电容cbn的顶极板、所述mp7的源极,以及所述mp3的源极连接,所述mp5的栅极分别与所述mn3的漏极、所述mn15的栅极连接;所述mp3的漏极与所述mn3的漏极连接,所述mp3的栅极分别与所述mp13的漏极、所述mn13的漏极、所述mn15的漏极连接;所述mn5的漏极分别与所述电容cbn的底极板、所述mn13的源极、所述mn15的源极、所述mn1的源极,以及所述mp1的漏极连接,所述mn5的源极接地,所述mn5的栅极接入时钟clkb;所述mp7的栅极接入所述时钟clkb,所述mp7的漏极分别与所述mn7的漏极、所述mn1的栅极连接;所述mn7的栅极接入所述电源电压vdd,所述mn7的源极分别与所述mp9的漏极、所述mn9的漏极连接;所述mp9的源极接入所述电源电压vdd,所述mp9的栅极和所述mn9的栅极均接入所述时钟clkb,所述mn9的源极接地;所述mp13的源极接入所述电源电压vdd,所述mp13的栅极和所述mn13的栅极均接入时钟clk;其中,所述时钟clkb输出的信号与所述时钟clk输出的控制信号相反;所述mn1的漏极与所述mp1的源极连接;所述mn3的源极分别与所述mp11的漏极、所述mn11的漏极连接,所述mn3的栅极和所述mp11的源极均接入所述电源电压vdd;所述mp11的栅极和所述mn11的栅极均接入所述时钟clkb;所述mn11的源极接地。

8、这里,所述p型栅压自举电路包括:mos管mn2、mp2、mn4、mp4、mn6、mp6、mn8、mp8、mn10、mp10、mn12、mp12、mn14、mp14和mp16,以及电容cbp;其中,所述mp6的源极接入所述电源电压vdd;所述mp6的栅极接入所述时钟clk;所述mp6的漏极分别与所述电容cbp的顶极板、所述mn2的源极、所述mp2的漏极、所述mp14的源极,以及所述mp16的源极连接;所述mn6的漏极、所述mn4的漏极和所述mn8的漏极均与所述电容cbp的底极板连接;所述mn6的源极接地;所述mn6的栅极分别与所述mn4的源极、所述mp4的源极,以及所述mp16的栅极连接;所述mp14的栅极和所述mn14的栅极均接入所述时钟clkb;所述mp14的漏极分别与所述mn14的漏极、所述mp16的漏极,以及所述mn4的栅极连接;所述mn14的源极接地;所述mp2的栅极分别与所述mn8的源极、所述mp8的源极连接;所述mn8的栅极接入所述时钟clk;所述mp8的栅极、所述mn10的源极均接地;所述mp8的漏极分别与所述mn10的漏极、所述mp10的漏极连接;所述mn10的栅极和所述mp10的栅极均接入所述时钟clk;所述mp10的源极接入所述电源电压vdd;所述mp4的栅极和所述mn12的源极均接地;所述mp4的漏极分别与所述mp12的漏极、所述mn12的漏极连接;所述mp12的栅极和所述mn12的栅极均接入所述时钟clk连接;所述mp12的源极接入所述电源电压vdd;所述mn2的漏极与所述mp2的源极连接。

9、这里,所述mp5的栅极与所述mns的栅极连接;所述mn1的漏极与所述mns的漏极连接。

10、这里,所述mn6的栅极与所述mps的栅极连接;所述mn2的漏极与所述mps的漏极连接。

11、这里,所述mp2的栅极与所述mp1的栅极连接;所述mn2的栅极与所述mn1的栅极连接。

12、这里,mn17和mn19为n型mos管;mp18和mp20为p型mos管。

13、本发明具有如下有益技术效果:针对栅压自举开关存在沟道电荷注入效应、时钟馈通效应和体效应,导致开关管非线性失真,无法适用于输入信号频率较高的场景的问题,本发明提出了一种用于高速模数转换器的栅压自举开关电路。相较于现有的典型栅压自举开关电路,本发明提供的栅压自举开关电路,通过将nmos管和pmos管并联,以相互抵消开关管存在的沟道电荷注入效应和时钟馈通效应,以及提供体效应消除子电路,以消除开关管的体效应。此外,本发明还向开关管中的pmos管提供p型栅压自举电路和n型栅压自举电路,以保持开关管的导通电阻恒定。本发明提供的栅压自举开关电路,可以在有效确保开关管栅源电压保持恒定,不受输入端vin输入信号变化影响的同时,改善开关管存在的非线性失真,提高了开关管的线性度和响应速度,实现了在输入信号频率较高的场景下的高精度采样。

14、以下将结合附图及实施例对本发明做进一步详细说明。

- 还没有人留言评论。精彩留言会获得点赞!