一种低成本延时电路的制作方法

本发明总的来说涉及集成电路。具体来说,本发明涉及一种低成本延时电路。

背景技术:

1、在多芯片之间的通信过程中,比如sigma-delta调制芯片与解调芯片之间的通信中,如图1所示,b芯片的解调模块输出clkout时钟,送给a芯片的调制模块,这条路径的延时包含b芯片的pad输出延时,板级连接延时和芯片a的pad输入延时。a芯片的调制模块收到clkout时钟后,会产生dat信号,送给b芯片的解调模块,这条路径的延时包含a芯片的pad输出延时,板级连接延时和芯片b的pad输入延时。b芯片的解调模块在接收到dat信号时,如果用之前输出的clkout信号采样,可能会存在无法正确采样到dat信号的问题。

技术实现思路

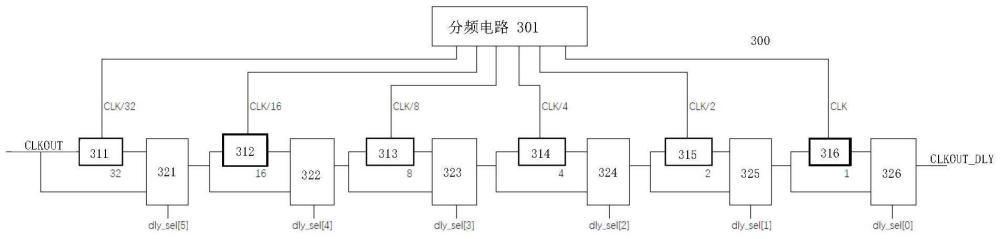

1、为至少部分解决现有技术中的上述问题,本发明提出一种低成本延时电路包括:

2、分频电路,所述分频电路接收时钟源clk,并提供基于时钟源clk生成的n个分频信号:clk/2n分频信号、clk/2n-1分频信号、…、clk/23分频信号、clk/22分频信号、clk/2分频信号及未分频的时钟源clk信号;

3、第一至第n+1d触发器;以及

4、第一至第n+1选择器,

5、其中第一d触发器的d输入端接收需要延迟的信号clkout,时钟控制端连接clk/2n分频信号,输出端q连接到第一选择器的第一输入端,第一选择器的第二输入端连接信号clkout,第一选择器的选择信号端接收第一选择信号,第一选择器基于第一选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出,

6、第二d触发器的d输入端连接第一选择器的输出端,时钟控制端连接clk/2n-1分频信号,输出端q连接到第二选择器的第一输入端,第二选择器的第二输入端连接第一选择器的输出端,第二选择器的选择信号端接收第二选择信号,第二选择器基于第二选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出,

7、以此类推直至第n d触发器,第n d触发器的d输入端连接第n-1选择器的输出端,时钟控制端连接clk/2分频信号,输出端q连接到第n选择器的第一输入端,第n选择器的第二输入端连接第n-1选择器的输出端,第n选择器的选择信号端接收第n选择信号,第n选择器基于第n选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出。

8、第n+1d触发器的d输入端连接第n选择器的输出端,时钟控制端连接clk信号,输出端q连接到第n+1选择器326的第一输入端,第n+1选择器的第二输入端连接第n选择器的输出端,第n+1选择器的选择信号端接收第n+1选择信号,第n+1选择器基于第n+1选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出。

9、在本发明的一个实施例中,所述分频电路包括n位计数器cnt[n:0]、第一至第n比较器、第一至第n-1与门,

10、n位计数器cnt[n:0]对时钟源clk信号进行计数,形成n位二进制数,第一比较器对第一位二进制数cnt[0]的值进行比较,当第一位二进制数cnt[0]的值为1时输出高电平,当第一位二进制数cnt[0]的值为0时,输出低电平,从而形成clk/2分频信号,

11、第二比较器对第二位二进制数cnt[1]的值进行比较,当第二位二进制数cnt[1]的值为1时,输出高电平,当第二位二进制数cnt[1]的值为0时,输出低电平,第一与门将第一比较器和第二比较器的输出进行与操作,形成clk/4分频信号,

12、第三比较器对第三位二进制数cnt[2]的值进行比较,当第三位二进制数cnt[2]的值为1时,输出高电平,当第三位二进制数cnt[2]的值为0时,输出低电平,第二与门将第三比较器的输出和第一与门的输出进行与操作,形成clk/8分频信号;

13、以此类推,第n比较器对第n位二进制数cnt[n-1]的值进行比较,当第n位二进制数cnt[n-1]的值为1时,输出高电平,当第n位二进制数cnt[n-1]的值为0时,输出低电平,第n-1与门将第n比较器的输出和第n-2与门的输出进行与操作,形成clk/2n分频信号。

14、在本发明的一个实施例中,所形成的时钟的占空比是1:n,时钟高电平只有一个最高频率宽度。

15、在本发明的一个实施例中,所形成的clk/2n分频信号、clk/2n-1分频信号、…、clk/23分频信号、clk/22分频信号、clk/2分频信号的高电平是对齐的。

16、在本发明的一个实施例中,n=5。

17、在本发明的一个实施例中,通过配置第一至第n+1选择信号的值,获得延时特定时钟周期的信号clkout_dly。

18、在本发明的一个实施例中,所述特定时钟周期是0至2n+2n-1+…+22+2+20范围内任意数量的clk时钟周期。

19、本发明的另一个实施例提供一种低成本延时电路包括:

20、分频电路,所述分频电路接收时钟源clk,并提供基于时钟源clk生成的n-m个分频信号:clk/2n-m分频信号、clk/2n-m-1分频信号、…、clk/22分频信号、clk/2分频信号及未分频的时钟源clk信号,其中1≤m<n;

21、第一至第m组d触发器、第m+1至第n+1d触发器;以及

22、第一至第n+1选择器,

23、第一组d触发器包括2m个级联的d触发器,2m个级联的d触发器的连接方式为:首个d触发器的d输入端接收需要延迟的信号clkout,末尾d触发器的输出端q连接到第一选择器的第一输入端,中间的每个d触发器的d输入端与相邻的前一个d触发器的输出端q相连,2m个级联的d触发器的时钟控制端分别连接clk/2n-m分频信号,第一选择器的第二输入端连接信号clkout,第一选择器的选择信号端接收第一选择信号,第一选择器基于第一选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出,

24、第二组d触发器包括2m-1个级联的d触发器,2m-1个级联的d触发器的连接方式为:首个d触发器的d输入端连接第一选择器的输出端,末尾d触发器的输出端q连接到第二选择器的第一输入端,中间的每个d触发器的d输入端与相邻的前一个d触发器的输出端q相连,2m-1个级联的d触发器的时钟控制端分别连接clk/2n-m分频信号,第二选择器的第二输入端连接第一选择器的输出端,第二选择器的选择信号端接收第二选择信号,第二选择器基于第二选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出,

25、以此类推直至第m组d触发器,第m组d触发器包括2个级联的d触发器,2个级联的d触发器的连接方式为:首个d触发器的d输入端连接第m-1选择器的输出端,末尾d触发器的输出端q连接到第m选择器的第一输入端,首个d触发器的d输入端与末尾d触发器的输出端q相连,2个级联的d触发器的时钟控制端分别连接clk/2n-m分频信号,第m选择器的第二输入端连接第m-1选择器的输出端,第m选择器的选择信号端接收第m选择信号,第m选择器基于第m选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出,

26、第m+1d触发器的d输入端连接第m选择器的输出端,时钟控制端连接clk/2n-m分频信号,输出端q连接到第m+1选择器的第一输入端,第m+1选择器的第二输入端连接第m选择器的输出端,第m+1选择器的选择信号端接收第m+1选择信号,第m+1选择器基于第m+1选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出,

27、第m+2d触发器的d输入端连接第m+1选择器的输出端,时钟控制端连接clk/2n-m-1分频信号,输出端q连接到第m+2选择器的第一输入端,第m+2选择器的第二输入端连接第m+1选择器的输出端,第m+2选择器的选择信号端接收第m+2选择信号,第m+2选择器基于第m+2选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出,

28、以此类推直至第n d触发器,第n d触发器的d输入端连接第n-1选择器的输出端,时钟控制端连接clk/2分频信号,输出端q连接到第n选择器的第一输入端,第n选择器的第二输入端连接第n-1选择器的输出端,第n选择器的选择信号端接收第n选择信号,第n选择器基于第n选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出,

29、第n+1d触发器的d输入端连接第n选择器的输出端,时钟控制端连接clk信号,输出端q连接到第n+1选择器326的第一输入端,第n+1选择器的第二输入端连接第n选择器的输出端,第n+1选择器的选择信号端接收第n+1选择信号,第n+1选择器基于第n+1选择信号的值选择第一输入端信号或第二输入端信号中的一个作为输出。

30、在本发明的另一个实施例中,信号clkout的频率大于clk/2n-m+1分频信号的频率,且小于clk/2n-m分频信号的频率。

31、在本发明的另一个实施例中,n=5,m=1、2或3。

32、本发明提供的低成本延时电路在保证调整精度的基础上,相对减少所需d触发器的个数。

- 还没有人留言评论。精彩留言会获得点赞!