用薄栅极多晶硅形成高电压晶体管的方法与流程

本公开大体上涉及半导体器件,且更具体地涉及非易失性存储器(nvm)器件及其制造方法,该nvm器件包括嵌入或整体地形成在单个衬底上的存储器单元、高电压场效应晶体管(hvfet)和高级逻辑fet。

背景技术:

0、背景

1、闪存或非易失性存储器(nvm)器件通常包括储存元件或单元的网格或阵列,每个储存元件或单元包括至少一个nvm晶体管和多个外围电路,外围电路包括解码器、驱动器、读出放大器和控制电路,以从阵列读取和向阵列写入。nvm晶体管通常包括电荷俘获或电荷储存层,并且需要4到10伏范围内的高电压(hv)用于编程和擦除操作。外围电路包括通常在低电压下工作的逻辑场效应晶体管(fet),以及能够支持nvm晶体管所需的高电压的多个hvfet。

2、为了提供改善的效率、安全性、功能性和可靠性,在与存储器单元相同的衬底上单片地包含逻辑fet和hvfet变得越来越普遍。然而,将逻辑fet和hvfet与nvm晶体管包含在同一个衬底上具有挑战性,因为每个器件或晶体管通常需要不同的制造参数。

3、因此,需要一种包含嵌入在或整体地形成在单个衬底上的存储器单元、hvfet和逻辑fet的半导体或nvm器件及其制造方法。

技术实现思路

0、概述

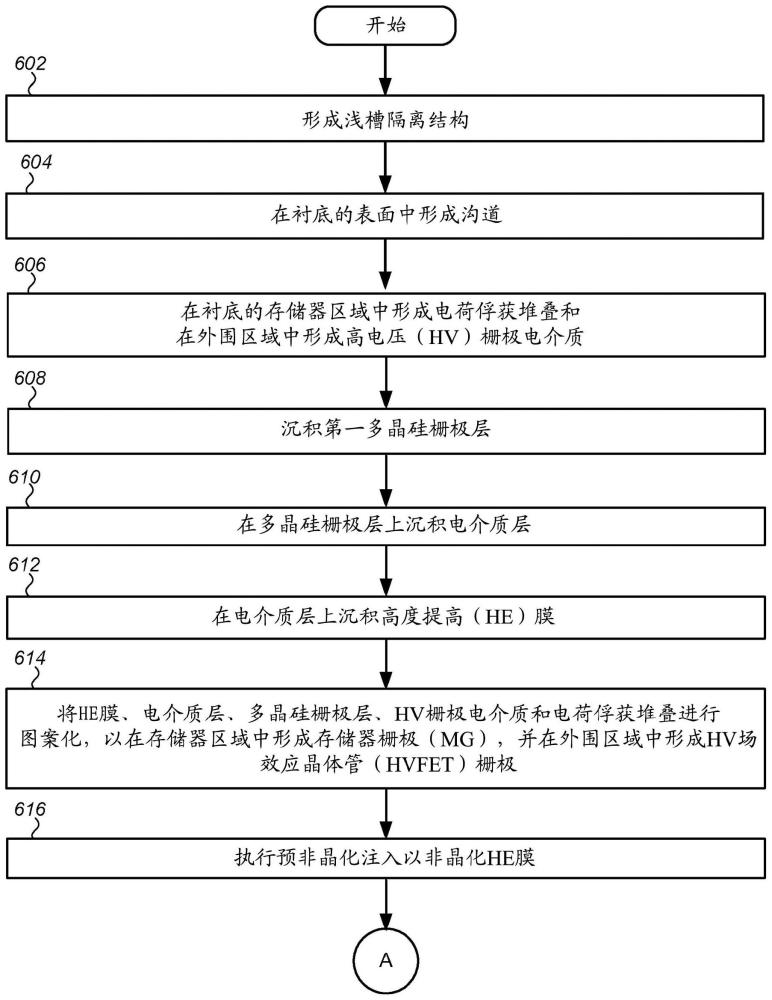

1、提供了一种半导体器件及其制造方法。通常,该方法开始于形成用于存储器栅极(mg)的将在衬底的存储器区域中的衬底的表面上形成的ono堆叠,以及形成用于高压场效应晶体管(hvfet)栅极的将在外围区域中的衬底的表面上形成的栅极电介质。接下来,多晶硅栅极层沉积在ono堆叠和栅极电介质上,电介质层形成在多晶硅栅极层上,并且高度提高(height-enhancing)(he)膜沉积在电介质层上。然后,针对mg和hvfet栅极对he膜、电介质层、栅极层、栅极电介质和ono堆叠进行图案化。邻近hvfet栅极注入源极/漏极(s/d)区域,并去除he多晶硅层以形成mg和hvfet栅极。衬底中s/d区域的深度通常大于衬底的表面上方的hvfet栅极的高度。在一些实施例中,he膜包括非晶硅或多晶硅,并且足够厚以防止来自漏极注入的掺杂剂到达hvfet栅极下面的沟道。

2、根据另一实施例,该方法还包括,在去除he膜之后,形成包括在外围区域中的用于低压(lv)逻辑fet的多晶硅栅极,并且使用高k金属栅极(hkmg)工艺用金属栅极替换lv逻辑fet的多晶硅栅极。

3、本技术提供了以下内容:

4、1).一种制造半导体器件的方法,包括:

5、在外围区域中的衬底的表面上形成的栅极电介质上沉积多晶硅栅极层;

6、在所述多晶硅栅极层上形成电介质层;

7、在所述电介质层上沉积高度提高(he)膜;

8、针对将要在所述外围区域中形成的高压场效应晶体管(hvfet)栅极对所述he膜、所述电介质层、所述多晶硅栅极层和所述栅极电介质进行图案化;

9、执行高能量注入,以在邻近所述hvfet栅极的所述衬底中的源极或漏极(s/d)区域中形成至少一个轻掺杂区域;

10、去除所述he膜;和

11、在所述外围区域中形成低压(lv)逻辑fet,其中所述lv逻辑fet是高k金属栅极(hkmg)逻辑fet。

12、2).根据1)所述的方法,其中,所述衬底中的所述轻掺杂区的深度大于所述hvfet栅极的高度。

13、3).根据1)所述的方法,其中,沉积所述he膜包括沉积非晶硅膜或多晶硅膜。

14、4).根据3)所述的方法,还包括用预非晶化注入对所述he膜注入。

15、5).根据1)所述的方法,其中,去除所述he膜包括化学机械平面化(cmp)、等离子蚀刻或其组合。

16、6).根据1)所述的方法,其中,执行所述高能量注入包括形成轻掺杂漏极(ldd)。

17、7).根据1)所述的方法,其中,所述hvfet栅极包括由图案化的多晶硅栅极层形成的多晶硅栅极,并且所述方法还包括在所述多晶硅栅极上形成硅化物。

18、8).根据1)所述的方法,其中,沉积所述多晶硅栅极层包括在存储器区域中形成在所述衬底的表面上的ono堆叠上沉积所述多晶硅栅极层;和

19、图案化所述he膜、所述电介质层、所述多晶硅栅极层和所述栅极电介质,还包括针对将在所述存储器区域中形成的存储器栅极(mg)对所述电介质层、所述多晶硅栅极层和所述ono堆叠进行图案化。

20、9).一种制造半导体器件的方法,包括:

21、将多晶硅栅极层沉积在存储器区域中的衬底的表面上形成的ono堆叠上,以及在外围区域中的所述衬底的表面上形成的栅极电介质上;

22、在所述多晶硅栅极层上形成电介质层;

23、在所述电介质层上沉积高度提高(he)膜;

24、针对将要在所述存储器区域中形成的存储器栅极(mg)和将要在所述外围区域中形成的高压场效应晶体管(hvfet)栅极对所述he膜、所述电介质层、所述多晶硅栅极层、所述栅极电介质和所述ono堆叠进行图案化;

25、执行高能量注入,以在邻近所述hvfet栅极的所述衬底中的源极或漏极(s/d)区域中形成至少一个轻掺杂区域;

26、去除所述he膜;和

27、在所述外围区域中形成低压(lv)逻辑fet,其中所述lv逻辑fet是高k金属栅极(hkmg)逻辑fet。

28、10).根据9)所述的方法,其中,沉积所述he膜包括将所述he膜沉积到足以防止来自所述高能量注入的掺杂剂到达所述hvfet栅极下方的沟道的厚度。

29、11).根据9)所述的方法,其中,沉积所述he膜包括沉积非晶硅膜或多晶硅膜。

30、12).根据11)所述的方法,还包括用预非晶化注入对所述he膜注入。

31、13).根据9)所述的方法,其中,去除所述he膜包括化学机械平面化(cmp)、等离子蚀刻或其组合。

32、14).根据9)所述的方法,其中,执行所述高能量注入包括形成轻掺杂漏极(ldd)。

33、15).根据9)所述的方法,其中,所述hvfet栅极包括由图案化的多晶硅栅极层形成的多晶硅栅极,并且所述方法还包括在所述多晶硅栅极上形成硅化物。

34、16).根据9)所述的方法,其中,图案化所述he膜、所述电介质层、所述多晶硅栅极层、所述栅极电介质和所述ono堆叠包括:与针对所述hvfet栅极对所述he膜、所述电介质层、所述多晶硅栅极层和所述栅极电介质进行图案化分开地,针对所述mg对所述he膜、所述电介质层、所述多晶硅栅极层和所述ono堆叠进行图案化。

35、17).一种制造半导体器件的方法,包括:

36、在衬底的表面上形成的栅极电介质上沉积多晶硅栅极层;

37、在所述多晶硅栅极层上形成电介质层;

38、在所述电介质层上沉积高度提高(he)膜;

39、针对将要在所述衬底的表面上形成的高压场效应晶体管(hvfet)栅极对所述he膜、所述电介质层、所述多晶硅栅极层和所述栅极电介质进行图案化;

40、执行高能量注入,以在邻近所述hvfet栅极的所述衬底中的源极或漏极(s/d)区域中形成至少一个轻掺杂区域;

41、去除所述he膜;和

42、在所述衬底的表面上形成低压(lv)逻辑fet,其中,所述lv逻辑fet是高k金属栅极(hkmg)逻辑fet,

43、其中,所述衬底中的所述轻掺杂区域的深度大于所述衬底的表面上方的所述hvfet栅极的栅极高度,并且其中,沉积所述he膜包括将所述he膜沉积到足以防止来自所述高能量注入的掺杂剂到达所述hvfet栅极下方的沟道的厚度。

44、18).根据17)所述的方法,其中,沉积所述he膜包括沉积非晶硅膜或多晶硅膜。

45、19).根据18)所述的方法,还包括用预非晶化注入对所述he膜注入。

46、20).根据17)所述的方法,其中,去除所述he膜包括化学机械平面化(cmp)、等离子蚀刻或其组合。

47、21).根据17)所述的方法,其中,执行所述高能量注入包括形成轻掺杂漏极(ldd)。

48、本发明的实施例的另外的特征和优点以及本发明的各种实施例的结构和操作在下面参照附图被详细地描述。应当注意,本发明不限于本文中描述的具体实施例。本文中介绍这样的实施例只是用于例证的目的。基于本文中包含的教导,另外的实施例对于相关领域的技术人员将是明显的。

- 还没有人留言评论。精彩留言会获得点赞!