动态锁存电路、芯片、比较器及模数转换器的制作方法

本申请涉及模拟集成电路,尤其涉及一种动态锁存电路、芯片、比较器及模数转换器。

背景技术:

1、随着现代通讯技术和信号处理技术的发展,越来越多的模拟信号需要转化成数字信号进行处理。因此,对高速高精度的模数转换器(analog to digital converter,adc)提出了更高的要求。在超高速adc中,高速高精度的比较器具有举足轻重的作用。

2、在高速高精度的比较器中,对比较器的失调电压要求很高,因此,比较器中的动态锁存电路的失调电压需要尽量小,来减小对比较器中的预放大电路增益的要求,使预放大电路的高宽带优化更容易实现。从而,比较器更容易实现高速比较。

3、传统技术中,在锁存阶段的初期,由于动态锁存电路对差分输入信号的放大能力较弱,导致动态锁存电路的失调电压过大。

技术实现思路

1、本申请提供一种动态锁存电路、芯片、比较器及模数转换器,能够减小动态锁存电路的失调电压。

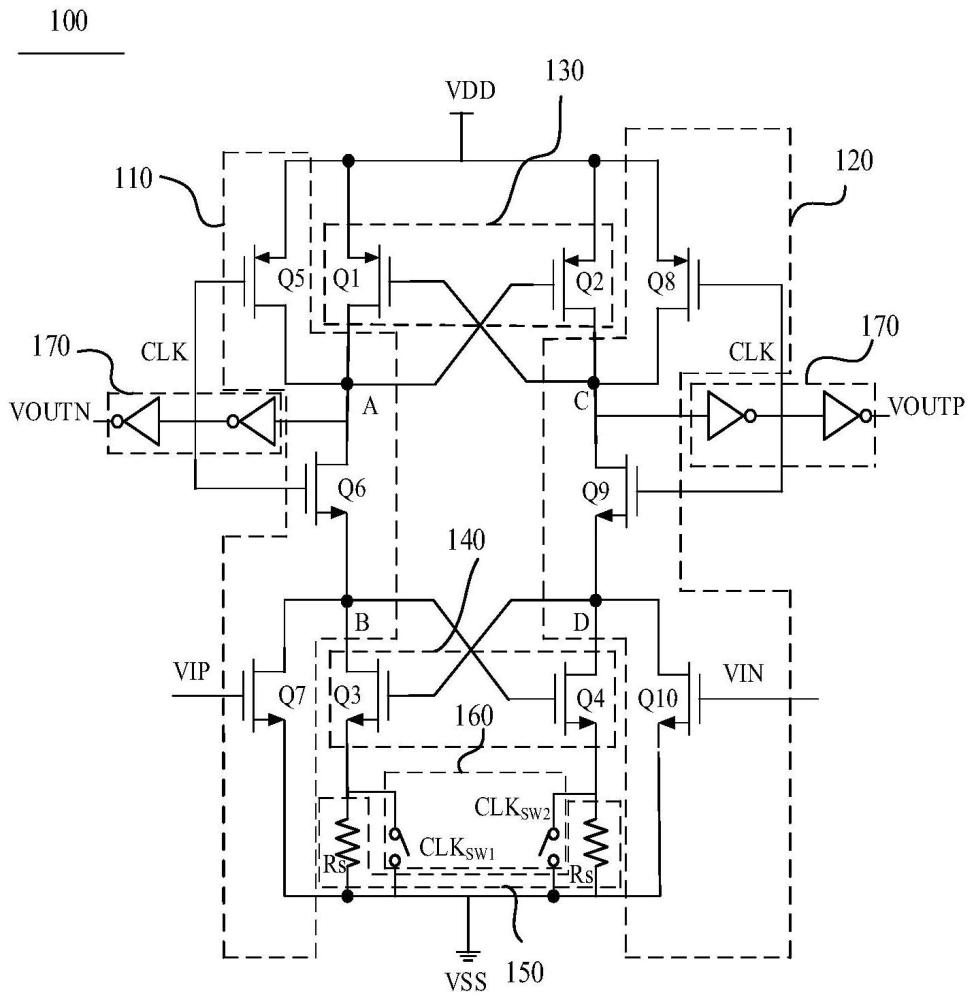

2、第一方面,本申请提供一种动态锁存电路,该动态锁存电路包括:第一开关串联支路、第二开关串联支路、第一交叉耦合管组、第二交叉耦合管组以及跨导衰减电路;

3、在电源输入端与接地端之间串联连接有第一开关串联支路和第二开关串联支路;

4、第一开关串联支路包括多个晶体管、第一节点和第二节点,第一交叉耦合管组与电源输入端电连接,第一交叉耦合管组还电连接在第一节点与第三节点之间;

5、第二开关串联支路包括多个晶体管、第三节点和第四节点,第二交叉耦合管组与跨导衰减电路电连接,第二交叉耦合管组还电连接在第二节点与第四节点之间,跨导衰减电路还电连接接地端;

6、跨导衰减电路,用于在动态锁存电路处于比较状态时,减小第二交叉耦合管组中的晶体管的跨导,以使第一交叉耦合管组中的晶体管先于第二交叉耦合管组中的晶体管导通。

7、通过第一方面提供的动态锁存电路,在动态锁存电路处于比较状态时,通过跨导衰减电路减小第二交叉耦合管组中的晶体管的跨导,使第一交叉耦合管组中的晶体管先于第二交叉耦合管组中的晶体管导通。如此,在差分电压对信号被第一交叉耦合管组放大一定倍数后,第二交叉耦合管组中的晶体管导通,使差分电压对信号的放大倍数增大。进而,降低第二交叉耦合管组中的晶体管对动态锁存电路的影响。从而,降低了动态锁存电路的失调电压。

8、在一种可能的设计中,动态锁存电路还包括:锁存响应电路;

9、第二交叉耦合管组还与锁存响应电路电连接,锁存响应电路还电连接接地端;

10、锁存响应电路,用于在第一交叉耦合管组中的晶体管和第二交叉耦合管组中的晶体管皆导通后,将跨导衰减电路短路,以增大第二交叉耦合管组中的晶体管的跨导。

11、在一种可能的设计中,锁存响应电路包括:多个开关管。

12、在一种可能的设计中,跨导衰减电路包括:多个电阻器。

13、在一种可能的设计中,动态锁存电路还包括:输出驱动电路;

14、输出驱动电路与第一节点电连接,输出驱动电路还与第三节点电连接;

15、输出驱动电路,用于增加动态锁存电路的输出电压,以增强动态锁存电路的驱动强度。

16、在一种可能的设计中,输出驱动电路包括:多个反相器。

17、在一种可能的设计中,第一交叉耦合管组包括:第一晶体管和第二晶体管,第二交叉耦合管组包括:第三晶体管和第四晶体管;

18、第一晶体管和第二晶体管交叉耦合电连接,第三晶体管和第四晶体管交叉耦合电连接。

19、第二方面,本申请提供一种芯片,包括:上述第一方面及第一方面任一种可能的设计中的动态锁存电路。

20、上述第二方面以及上述第二方面的各可能的设计中所提供的芯片,其有益效果可以参见上述第一方面和第一方面的各可能的实施方式所带来的有益效果,在此不再赘述。

21、第三方面,本申请提供一种比较器,包括:多级放大电路以及上述第一方面及第一方面任一种可能的设计中的动态锁存电路。

22、第四方面,本申请提供一种模数转换器,包括:电容阵列电路、控制逻辑电路以及上述第三方面中的比较器;

23、电容阵列电路与比较器电连接,比较器与控制逻辑电路电连接,逻辑控制电路还与电容阵列电路电连接;

24、电容阵列电路,用于向比较器提供差分电压对信号,以使动态锁存电路对差分电压对信号进行比较;

25、控制逻辑电路,用于向比较器提供时钟信号,时钟信号用于指示动态锁存电路的工作状态。

技术特征:

1.一种动态锁存电路,其特征在于,所述动态锁存电路包括:第一开关串联支路、第二开关串联支路、第一交叉耦合管组、第二交叉耦合管组以及跨导衰减电路;

2.根据权利要求1所述的动态锁存电路,其特征在于,所述动态锁存电路还包括:锁存响应电路;

3.根据权利要求2所述的动态锁存电路,其特征在于,所述锁存响应电路包括:多个开关管。

4.根据权利要求1所述的动态锁存电路,其特征在于,所述跨导衰减电路包括:多个电阻器。

5.根据权利要求1所述的动态锁存电路,其特征在于,所述动态锁存电路还包括:输出驱动电路;

6.根据权利要求5所述的动态锁存电路,其特征在于,所述输出驱动电路包括:多个反相器。

7.根据权利要求1-6任一项所述的动态锁存电路,其特征在于,所述第一交叉耦合管组包括:第一晶体管和第二晶体管,所述第二交叉耦合管组包括:第三晶体管和第四晶体管;

8.一种芯片,其特征在于,包括:如权利要求1-7任一项所述的动态锁存电路。

9.一种比较器,其特征在于,所述比较器包括:多级放大电路以及如权利要求1-7任一项所述的动态锁存电路。

10.一种模数转换器,其特征在于,包括:电容阵列电路、控制逻辑电路以及如权利要求9所述的比较器;

技术总结

本申请提供一种动态锁存电路、芯片、比较器及模数转换器。该动态锁存电路包括:第一开关串联支路、第二开关串联支路、第一交叉耦合管组、第二交叉耦合管组以及跨导衰减电路。在动态锁存电路处于比较状态时,通过跨导衰减电路减小第二交叉耦合管组中的晶体管的跨导,使第一交叉耦合管组中的晶体管先于第二交叉耦合管组中的晶体管导通。如此,在差分电压对信号被第一交叉耦合管组放大一定倍数后,第二交叉耦合管组中的晶体管导通,使差分电压对信号的放大倍数增大。进而,降低第二交叉耦合管组中的晶体管对动态锁存电路的影响。从而,降低了动态锁存电路的失调电压。

技术研发人员:黄玲玲

受保护的技术使用者:珠海楠欣半导体科技有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!