一种分段冗余电容阵列及其方法与流程

本发明涉及电子电路,特别是涉及一种分段冗余电容阵列及其方法。

背景技术:

1、模数转换器(adc)作为模拟和数字界的桥梁,一直以来都是研究的重点。传感器系统将现实模拟世界的非电信号转换为电信号,再由模数转换器将电信号转换为数字信号以便于计算机处理。模数转换器常用于传感器接口电路。电容阵列作为模数转换器的重要组成部分之一,对于模数转换器的整体性能十分总要。

2、现有的电容阵列存在以下问题:1.如要做到高分辨率(>10bit),电容数量将>1024,这极大的增加了面积和功耗。2.由于传统电容阵列所用的电容数量巨大,对于匹配性能要求极高,如果电容摆放不合理,将会损耗精度。3.由于参考电压在开关翻转时可能跌落,造成误判,会出现转换误差,降低精度。

3、故而,在现有的模数转换器中,电容阵列的使用是实现模拟信号到数字信号转换的关键部分。然而,现有的电容阵列结构单一,冗余性不足,导致转换精度和稳定性受到限制。

技术实现思路

1、为了解决现有技术中存在的问题,本发明提供了一种分段冗余电容阵列及其方法,主要是应用于模数转换器的10bit分段冗余电容阵列。分段冗余电容阵列减少了所需电容的数量,同时提高了转换过程中对误判的容忍能力,减小了转换误差,提高了精度。

2、为了实现上述目的,本发明采用如下技术方案:

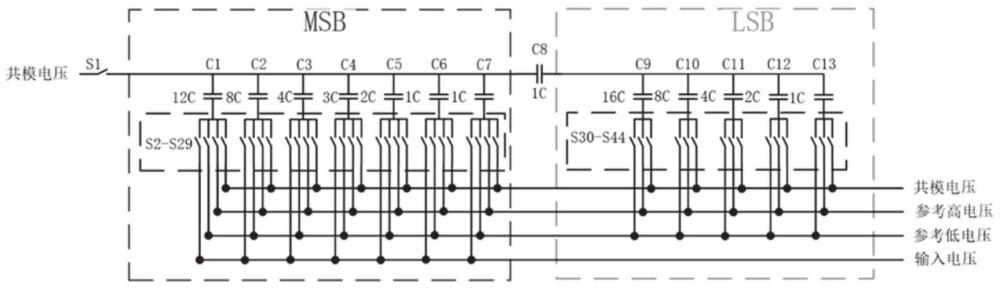

3、第一方面本发明提供一种分段冗余电容阵列,用于模数转换器,其特征在于,包括:桥接电容c8、msb电容阵列和lsb电容阵列;所述msb电容阵列与lsb电容阵列均包括多个并联的电容,所述msb电容阵列与lsb电容阵列通过桥接电容c8连接,用于全电容阵列分段冗余。

4、作为本发明进一步改进,所述msb电容阵列的多个电容共同的顶板与桥接电容c8的顶板连接,且通过开关s1与共模电压连接,所述msb电容阵列的多个电容各自的底板通过第一开关阵列分别与共模电压、参考高电压、参考低电压、输入电压连接。

5、作为本发明进一步改进,所述lsb电容阵列的多个电容共同的顶板与桥接电容c8的顶板连接,所述lsb电容阵列的多个电容各自的底板通过第二开关阵列分别与共模电压、参考高电压、参考低电压连接。

6、作为本发明进一步改进,所述msb电容阵列的多个并联的电容的大小依次减小,所述lsb电容阵列的多个并联的电容的大小依次减小。

7、作为本发明进一步改进,所述msb电容阵列包括第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5、第六电容c6及第七电容c7,对应电容大小分别为12c、8c、4c、3c、2c、1c、1c,其中c为单位电容。

8、作为本发明进一步改进,所述lsb电容阵列包括:第九电容c9、第十电容c10、第十一电容c11、第十二电容c12及第十三电容c13,电容大小分别为16c,8c,4c,2c,1c,其中c为单位电容。

9、作为本发明进一步改进,所述桥接电容c8的电容大小为1c。

10、作为本发明进一步改进,所述分段冗余电容阵列为10bit分段冗余电容阵列。

11、作为本发明进一步改进,所述分段冗余电容阵列的分段结构包括63个单位电容。

12、第二方面本发明提供一种分段冗余电容阵列的冗余方法,包括:将最高位电容拆分,并分配给后级电容,全电容阵列分段冗余。

13、与现有技术相比,本发明具有以下有益效果:

14、本发明的分段冗余电容阵列包括msb电容阵列、lsb电容阵列、桥接电容,通过将分段冗余电容阵列算法和冗余算法相结合,减少了所需电容的数量,同时提高了转换过程中对误判的容忍能力,减小了转换误差,提高了精度。分段冗余电容阵列可以极大的减少电容数量,实现面积的优化;而冗余技术可以提高精度。将两技术结合而产生的分段冗余电容阵列同时具有两者的优点,发挥小体积分段冗余的目的。在全阵列使用重构的冗余算法的作用下,达到全电容阵列分段冗余的效果,并且无需增加额外电容。

技术特征:

1.一种分段冗余电容阵列,用于模数转换器,其特征在于,包括:桥接电容c8、msb电容阵列和lsb电容阵列;所述msb电容阵列与lsb电容阵列均包括多个并联的电容,所述msb电容阵列与lsb电容阵列通过桥接电容c8连接,用于全电容阵列分段冗余。

2.根据权利要求1所述的分段冗余电容阵列,其特征在于,所述msb电容阵列的多个电容共同的顶板与桥接电容c8的顶板连接,且通过开关s1与共模电压连接,所述msb电容阵列的多个电容各自的底板通过第一开关阵列分别与共模电压、参考高电压、参考低电压、输入电压连接。

3.根据权利要求1所述的分段冗余电容阵列,其特征在于,所述lsb电容阵列的多个电容共同的顶板与桥接电容c8的顶板连接,所述lsb电容阵列的多个电容各自的底板通过第二开关阵列分别与共模电压、参考高电压、参考低电压连接。

4.根据权利要求1所述的分段冗余电容阵列,其特征在于,所述msb电容阵列的多个并联的电容的大小依次减小,所述lsb电容阵列的多个并联的电容的大小依次减小。

5.根据权利要求1所述的分段冗余电容阵列,其特征在于,所述msb电容阵列包括第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5、第六电容c6及第七电容c7,对应电容大小分别为12c、8c、4c、3c、2c、1c、1c,其中c为单位电容。

6.根据权利要求1所述的分段冗余电容阵列,其特征在于,所述lsb电容阵列包括:第九电容c9、第十电容c10、第十一电容c11、第十二电容c12及第十三电容c13,电容大小分别为16c,8c,4c,2c,1c,其中c为单位电容。

7.根据权利要求1所述的分段冗余电容阵列,其特征在于,所述桥接电容c8的电容大小为1c。

8.根据权利要求1所述的分段冗余电容阵列,其特征在于,所述分段冗余电容阵列为10bit分段冗余电容阵列。

9.根据权利要求8所述的分段冗余电容阵列,其特征在于,所述分段冗余电容阵列的分段结构包括63个单位电容。

10.权利要求1至9任一项所述的分段冗余电容阵列的冗余方法,其特征在于,包括:将最高位电容拆分,并分配给后级电容,全电容阵列分段冗余。

技术总结

本发明涉及电子电路技术领域,公开了一种分段冗余电容阵列包括:桥接电容C8、MSB电容阵列和LSB电容阵列;所述MSB电容阵列与LSB电容阵列均包括多个并联的电容,所述MSB电容阵列与LSB电容阵列通过桥接电容C8连接,用于全电容阵列分段冗余。主要是应用于模数转换器的10bit分段冗余电容阵列。分段冗余电容阵列减少了所需电容的数量,同时提高了转换过程中对误判的容忍能力,减小了转换误差,提高了精度。

技术研发人员:刘铭扬,李政,李振明,杨雅婷,刘伟,侯影,刘昱

受保护的技术使用者:中国电力科学研究院有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!