一种基于SAR-ADC的多序列转换方法和电路与流程

本发明属于数模转换,尤其涉及一种基于sar-adc的多序列转换方法和电路。

背景技术:

1、随着集成电路和数字信号处理技术的快速发展,我们可以在数字域里实现比模拟域里更高精度,更快速度,更低价格的各种信号处理功能,因此,模数转换器作为模拟系统和数字系统的接口就变得非常重要。为了使用强大的数字信号处理技术来对真实世界中的模拟信号进行处理,用于在模拟信号和数字信号之间起桥梁作用的模数转换器在电视、移动装置和其他消费电子产品中,均得到了极为广泛的应用。

2、而在各种类型的模数转换器当中,逐次逼近型的模数转换器(sar-adc)因为其低功耗,中等精度和中高分辨率而得到了广泛的应用。逐次逼近模数转换器(sar-adc)的精度较高,功耗和面积小,并且随着纳米级互补金属氧化物半导体(cmos)工艺的成熟,实现高速高精度sar-adc也成为可能。近年来,sar-adc的研究成果中精度已经可达16位。

3、传统mcu集成的sar-adc,数字设计部分转换序列的配置较为单一,无法满足当前更多新的应用场景,从而降低了mcu的通用性特点,传统方案大多只支持单触发源触发单个通道转换或者单个序列转化。当遇到要求单序列足够长,多序列组合且独立可配,就无法满足应用需求。尤其是在基于双电机高效智能foc电机应用当中,提供了很好的帮助。

4、传统的mcu方案通过例化两个或者以上的sar-adc模块,实现多序列转换,这就带了很高的芯片成本和硬件开销;尤其是当电机应用的冗余程度和需求更高时,会带来大量的芯片面积浪费;当多序列转换对实时性要求不高的情况下,或者仅仅对某一个序列的实时性要求较高的情况下,通过例化一个sar-adc模块可以有效降低芯片成本,但是,传统的设计方案需要通过软件进行序列配置的频繁切换,降低了实时性,使得改进后cpu占用率大大降低;本发明支持最高32个通道的序列转换,可以自由组合为四个基本序列,同时各个序列的工作模式和序列长度独立可配,在不增加硬件资源的情况下,最大化的降低了软件参与度,极大丰富了应用场景,提高了灵活性,在较少开销的前提下实现了基本序列的动态更新。

技术实现思路

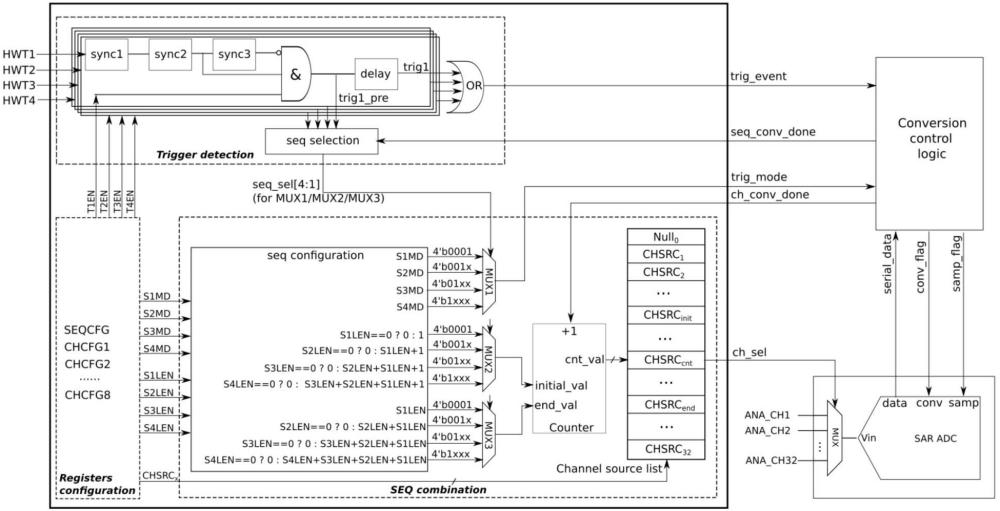

1、为了解决现有技术中的上述问题,本发明提出了一种基于sar-adc的多序列转换方法和电路,所述电路包含:寄存器配置模块,触发监测模块和序列组合模块;

2、所述寄存器配置模块用于配置序列配置寄存器seqcfg和8个通道配置寄存器chcfgx(x=1~8);用于描述四个基本序列seq1~seq4;所述序列配置寄存器seqcfg是32bit寄存器;包括s1md~s4md位:是序列seq1~seq4触发模式控制位;其中:0为序列触发模式,1为通道触发模式;t1en~t4en:是序列seq1~seq4的触发源使能控制位,0为失效,1为使能;s1len~s4len:是序列seq1~seq4的长度控制位;

3、其中:所述通道配置寄存器chcfgx(x=1~8)是32bit寄存器;通道配置寄存器chcfg1包含通道源chsrc1~ chsrc4;通道配置寄存器chcfg2包含通道源chsrc5~ chsrc8;以此类推,通道配置寄存器chcfg8包含通道源chsrc29~ chsrc32;chsrc1~ chsrc32通道源的值1~32对应模拟通道ana_ch1~ana_ch32 ;若干个通道源组合在一起形成一个序列;

4、所述触发监测模块设置输入信号触发源hwt1~hwt4;四个触发源hwt1~hwt4,分别对应每个基本序列seq1~seq4;触发源hwt1~hwt4信号用于接收芯片引脚或者其他ip的输出,经过三级同步sync1~sync3和‘&’逻辑,在获取使能后的触发源的上升沿trig1_pre~trig4_pre脉冲作为预触发信号;4路预触发信号trig1_pre~trig4_pre为脉冲信号,经过序列选择模块的时序逻辑,输出4bit的序列选择seq_sel[4:1]信号,作为序列信息的选择信号;所述4路预触发信号trig1_pre~trig4_pre经过延时和“or”操作,产生trig_event信号,trig_event作为真正的有效触发信号去触发转换控制逻辑模块进行通道转换,从而使得触发通道转换之前,序列相关配置已经完成切换并且保持稳定;等到所选择的序列转换完成,转换控制逻辑模块将seq_conv_done信号置1,此信号将序列选择信号清0,完成序列的转换;序列选择信号被送到序列组合模块,用来选择和切换序列配置信息;

5、所述序列组合模块包含序列配置模块,3个多路选择单元mux1/mux2/mux3,计数器counter和通道源列表;其中:

6、所述通道源列表包括32个通道源chsrc1~chsrc32,每个通道源chsrcx(x=1~32)包含32个模拟通道的配置信息;

7、所述计数器counter的cnt_val’输出值作为通道源列表的索引,指向通道源列表的哪一个通道源chsrcy,相应通道源chsrcy的值则表示当前选择的具体通道ana_chz,切换通道的时候,计数器递增以修改通道源列表的索引值,以切换到下一个通道源所代表的模拟通道;

8、所述序列配置模块用于整合来自寄存器配置模块的序列配置信息,序列配置信息包含触发模式以及序列的起始位置信息;

9、所述多路选择单元mux1/mux2/mux3,多路选择单元选择来自触发检测模块的seq_sel[4:1]信号,mux1用于选择序列的触发模式,mux2和mux3用于选择序列的起始和结束地址。

10、进一步的,序列转换采用了分时复用,同一个时间点仅有一个模拟通道进行模数转换。

11、进一步的,寄存器配置模块设置外部读写接口,以支持对基本序列长度和组织方式的动态更新。

12、进一步的,触发源单次触发一个通道称为通道触发模式,需要多次触发才能够完成包含多个通道源的一个序列的转换。

13、进一步的,为每个序列配置独立的触发源。

14、一种基于sar-adc的多序列转换方法,使用上述基于sar-adc的多序列转换电路进行多序列转化。

15、一种芯片,包括上述基于sar-adc的多序列转换电路。

16、一种计算终端,包括所述的基于sar-adc的多序列转换电路。

17、一种基于sar-adc的多序列转换系统,包括所述的基于sar-adc的多序列转换电路。

18、一种基于sar-adc的多序列转换数字电路,包括所述的基于sar-adc的多序列转换电路。

19、本发明的有益效果包括:

20、(1)支持多通道的序列转换,可以自由组合为四个基本序列,同时各个序列的工作模式和序列长度独立可配,在不增加硬件资源的情况下,极大丰富了应用场景,提高了灵活性;通过设置虚拟的通道源chsrc1~chsrc32,使得在寄存器中的虚拟通道源能够用来选择一个模拟通道ana_chx,

21、(2)多序列自由组合方式可以平衡序列数量和单序列通道源数量,适应更多的应用场景;既可以满足某些对序列通道数量有要求的应用,又可以满足独立触发多序列转换的应用;适应了对实时性要求不高或者只对某个序列有较高实时性要求的情况,此时可大大降低芯片成本;更重要的是,多序列转换方式可以降低软件参与度,采用硬件触发方式提高多序列adc转换的控制精度;

22、(3)通过本地计算终端对基本序列的使用数据更新序列seq1~seq4的长度控制位s1len~s4len,通过减少基本序列的切换次数来进一步的保障序列转换的稳定性;根据相同使用场景中多个计算终端对基本序列的使用数据,更新通道配置寄存器chcfgx(x=1~8)的配置数据,以实现动态序列和本地计算终端的定制化的基本序列组成;提高计算环境中多个计算终端对序列触发模式的使用频率,提高基本序列的可用性;基于数据或者大数据分析来动态支持基本序列的动态更新和部分动态更新,大大提高了序列转换的效率。

- 还没有人留言评论。精彩留言会获得点赞!