半导体结构及其制备方法与流程

本公开实施例涉及半导体领域,特别涉及一种半导体结构及其制备方法。

背景技术:

1、动态随机存取存储器(dram)包括阵列排布的存储单元以及用于对存储单元进行读写操作的外围电路。外围电路包括晶体管,晶体管的栅极、源极、漏极可以通过相应的接触插塞与周边结构以及外界的控制端或信号端等电连接。

2、由于目前的半导体结构的制备工艺繁琐,在制备接触插塞前可能会出现一些问题,导致半导体结构的良率下降。

技术实现思路

1、本公开实施例提供一种半导体结构及其制备方法,至少有利于提高半导体结构的良率。

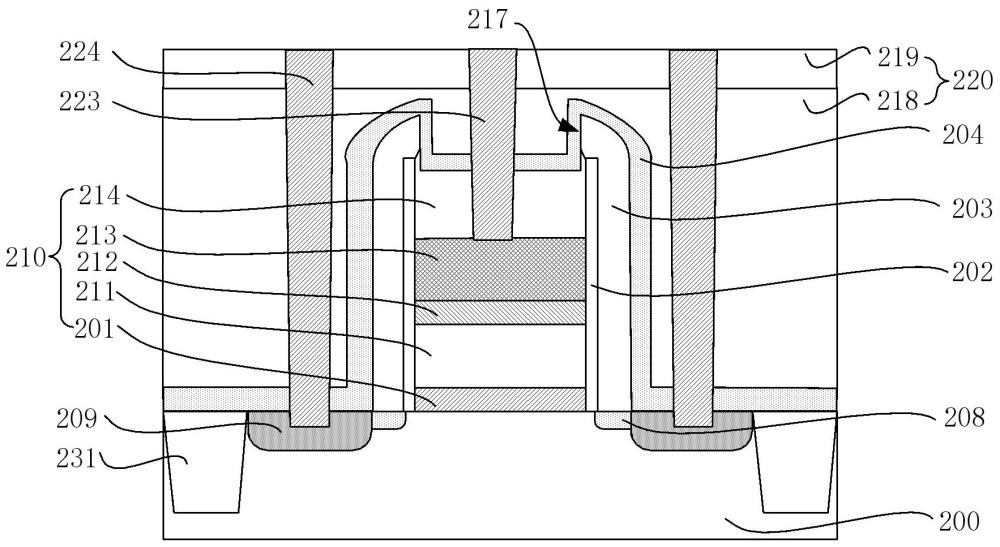

2、根据本公开一些实施例,本公开实施例一方面提供一种半导体结构,包括:基底;栅极结构,所述栅极结构位于所述基底的部分表面上,所述栅极结构包括依次层叠的栅介质层、栅导电层以及栅盖帽层,所述栅盖帽层具有凹槽;第一间隔层以及第二间隔层,所述第一间隔层位于所述栅极结构的侧壁,所述第二间隔层位于所述第一间隔层的侧面;保护层,所述保护层共形覆盖所述基底的部分表面、所述第二间隔层的表面以及所述栅盖帽层的顶面;所述保护层还共形覆盖所述凹槽的内壁面,位于所述凹槽底部的所述保护层的顶面不高于所述第二间隔层的顶面;介质层,所述介质层覆盖所述保护层的表面。

3、在一些实施例中,沿垂直于所述基底表面的方向,所述保护层的厚度小于或等于所述凹槽的深度。

4、在一些实施例中,所述介质层位于所述凹槽内,位于所述凹槽内的所述介质层的顶面不低于所述保护层的顶面。

5、在一些实施例中,所述介质层包括层叠的第一介质层以及第二介质层,所述第一介质层的顶面不低于所述保护层的顶面。

6、在一些实施例中,沿垂直于所述基底表面的方向,所述凹槽的深度与所述栅盖帽层的厚度的比值范围为0.1~0.5。

7、在一些实施例中,还包括第一接触插塞,所述第一接触插塞贯穿所述介质层、所述保护层以及所述栅盖帽层且与所述栅导电层接触,所述第一接触插塞还位于所述凹槽内。

8、根据本公开一些实施例,本公开实施例另一方面还提供一种半导体结构的制备方法,包括:提供基底;形成栅极结构,所述栅极结构位于所述基底的部分表面上,所述栅极结构包括依次层叠的栅介质层、栅导电层以及栅盖帽层,所述栅盖帽层的宽度从底部到顶部逐渐减小;形成第一间隔层,所述第一间隔层位于所述栅极结构的侧壁;形成第二间隔层,所述第二间隔层位于所述第一间隔层的侧壁和顶面;对所述栅盖帽层进行刻蚀处理,以使所述栅盖帽层中形成自所述栅盖帽层的顶面向内部延伸的凹槽;形成保护层,所述保护层共形覆盖所述基底的部分表面、所述第二间隔层的表面以及所述栅盖帽层的顶面;所述保护层还共形覆盖所述凹槽的内壁面,位于所述凹槽底部的所述保护层的顶面不高于所述第二间隔层的顶面;形成介质层,所述介质层覆盖所述保护层的表面。

9、在一些实施例中,对所述栅盖帽层进行刻蚀处理之前还包括:形成牺牲层,所述牺牲层覆盖所述基底、所述第二间隔层、所述栅极结构以及所述第一间隔层的表面;回刻蚀所述牺牲层,直至露出所述栅盖帽层;沿着所暴露的所述栅盖帽层对部分厚度的所述栅盖帽层进行刻蚀处理;在形成所述保护层之前,去除所述牺牲层。

10、在一些实施例中,对所述栅盖帽层进行刻蚀处理的工艺步骤中,所述牺牲层的材料的刻蚀速率小于所述栅盖帽层的材料的刻蚀速率。

11、在一些实施例中,形成第一间隔层之后且形成第二间隔层之前包括:对所述栅极结构的两侧的所述基底进行第一次掺杂处理,以使所述栅极结构的两侧的所述基底内分别形成第一轻掺杂区以及第二轻掺杂区,所述第二间隔层位于所述第一轻掺杂区上以及第二轻掺杂区上;形成所述第二间隔层之后包括:对所述栅极结构的两侧的所述基底进行第二次掺杂处理,以使所述栅极结构的两侧的所述基底内分别形成第一掺杂区以及第二掺杂区,所述保护层位于所述第一掺杂区以及第二掺杂区上。

12、在一些实施例中,形成所述介质层之后还包括:形成所述介质层之后还包括:刻蚀所述介质层、所述保护层以及所述栅盖帽层,形成暴露所述栅导电层的第一接触孔,所述第一接触孔在所述基底上的正投影位于所述凹槽在所述基底上的正投影中;形成第一接触插塞,所述第一接触插塞填充所述第一接触孔。

13、本公开实施例提供的技术方案至少具有以下优点:

14、本公开实施例提供的半导体结构中,设置第一间隔层以及第二间隔层位于栅导电层以及栅盖帽层的侧面,以降低栅极结构与相邻导电结构之间的寄生电容。栅盖帽层具有凹槽,保护层共形覆盖凹槽的内壁面,位于凹槽底部的保护层的顶面不高于第二间隔层的顶面,如此,对介质层进行化学机械研磨工艺以使介质层的表面平坦化工艺之后,去除研磨液的溶液只能对介质层以及保护层进行刻蚀或者被保护层所阻挡,从而保护第一间隔层以及栅极结构,防止去除研磨液的溶液对第一间隔层以及栅盖帽层造成刻蚀影响。上述方案可以有效避免去除研磨液的溶液腐蚀第一间隔层以及栅盖帽层,进而腐蚀栅导电层的问题,有利于提高半导体结构的良率。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,沿垂直于所述基底表面的方向,所述保护层的厚度小于或等于所述凹槽的深度。

3.根据权利要求2所述的半导体结构,其特征在于,所述介质层位于所述凹槽内,位于所述凹槽内的所述介质层的顶面不低于所述保护层的顶面。

4.根据权利要求3所述的半导体结构,其特征在于,所述介质层包括层叠的第一介质层以及第二介质层,所述第一介质层的顶面不低于所述保护层的顶面。

5.根据权利要求1-4任一项所述的半导体结构,其特征在于,沿垂直于所述基底表面的方向,所述凹槽的深度与所述栅盖帽层的厚度的比值范围为0.1~0.5。

6.根据权利要求1-4任一项所述的半导体结构,其特征在于,还包括第一接触插塞,所述第一接触插塞贯穿所述介质层、所述保护层以及所述栅盖帽层且与所述栅导电层接触,所述第一接触插塞还位于所述凹槽内。

7.一种半导体结构的制备方法,其特征在于,包括:

8.根据权利要求7所述的制备方法,其特征在于,对所述栅盖帽层进行刻蚀处理之前还包括:

9.根据权利要求8所述的制备方法,其特征在于,对所述栅盖帽层进行刻蚀处理的工艺步骤中,所述牺牲层的材料的刻蚀速率小于所述栅盖帽层的材料的刻蚀速率。

10.根据权利要求7-9任一项所述的制备方法,其特征在于,形成第一间隔层之后且形成第二间隔层之前包括:对所述栅极结构的两侧的所述基底进行第一次掺杂处理,以使所述栅极结构的两侧的所述基底内分别形成第一轻掺杂区以及第二轻掺杂区,所述第二间隔层位于所述第一轻掺杂区上以及第二轻掺杂区上;

11.根据权利要求7-9任一项所述的制备方法,其特征在于,形成所述介质层之后还包括:刻蚀所述介质层、所述保护层以及所述栅盖帽层,形成暴露所述栅导电层的第一接触孔,所述第一接触孔在所述基底上的正投影位于所述凹槽在所述基底上的正投影中;形成第一接触插塞,所述第一接触插塞填充所述第一接触孔。

技术总结

本公开实施例涉及半导体领域,提供一种半导体结构及其制备方法。半导体结构包括:基底;栅极结构,栅极结构位于基底的部分表面上,栅极结构包括依次层叠的栅介质层、栅导电层以及栅盖帽层,栅盖帽层具有凹槽;第一间隔层以及第二间隔层,第一间隔层位于栅极结构的侧壁,第二间隔层位于第一间隔层的侧面;保护层,保护层共形覆盖基底的部分表面、第二间隔层的表面以及栅盖帽层的顶面;保护层还共形覆盖凹槽的内壁面,位于凹槽底部的保护层的顶面不高于第二间隔层的顶面;介质层,介质层覆盖保护层的表面。本公开实施例提供的半导体结构及其制备方法可以提高半导体结构的良率。

技术研发人员:金星,宣锋

受保护的技术使用者:长鑫新桥存储技术有限公司

技术研发日:

技术公布日:2024/2/6

- 还没有人留言评论。精彩留言会获得点赞!