射频开关芯片片上模拟地与射频地连接电路及封装结构的制作方法

本申请涉及射频开关芯片领域,特别涉及一种射频开关芯片片上模拟地与射频地连接电路及封装结构。

背景技术:

1、随着5g通信的发展,应用系统pcb板布局芯片面积及走线资源愈发紧张,对芯片的尺寸等封装方面出现两个趋势。一、将部分芯片集成到一颗芯片上,提高芯片在系统板面积利用效率;二、小尺寸的芯片继续保持相同性能指标下,将封装尺寸不断缩小。

2、射频开关尤其是低掷数2t开关是小尺寸芯片,主要封装形式就是qfn和lga封装的6个pin脚,其中一个pin脚是gnd地。而2t开关为考虑两个通道相互之间的隔离度,需要把各自的射频地分开,再加上模拟部分电路的地,一般片上有3个地pad。

3、如何把片上3个pad引线连接到封装框架上唯一的gnd地pin脚。lga封装采用基板转接,但加个基板成本,产品成本竞争力不够。出于成本考虑,一般采用wb qfn封装,而wb打线同一个地pin最多只能连接两个gnd pad。

技术实现思路

1、本申请提供一种射频开关芯片片上模拟地与射频地连接电路及封装结构,射频芯片片上模拟地与射频地连接数量和封装问题。

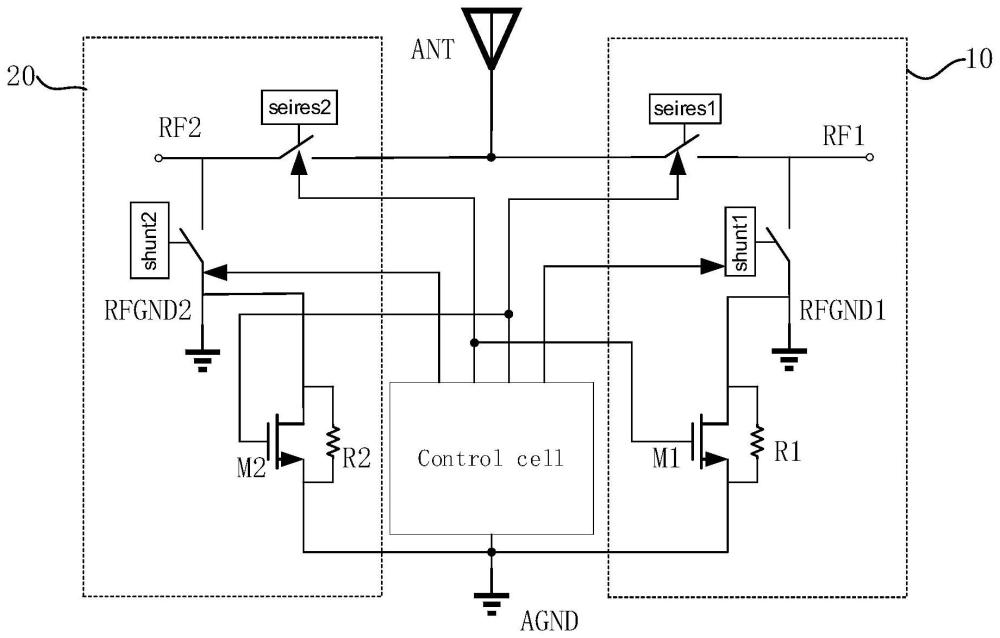

2、一方面,本申请提供一种射频开关芯片片上模拟地与射频地连接电路,包括射频天线、控制单元、对称设置的第一射频电路和第二射频电路;所述第一射频电路和第二射频电路共同连接到射频天线和控制单元上;

3、所述第一射频电路和第二射频电路分别包含有射频输入端、射频地和控制电路;所述控制单元设置有用于第一射频电路和第二射频电路共用的模拟地;每个控制电路的两个输入端分别连接在对应射频电路的射频地和模拟地之间,且控制电路的控制端连接到控制单元上;所述控制电路用于将所在射频电路中的射频地与控制单元的模拟地导通;

4、当所述控制单元通过控制电路导通模拟地和第一射频电路的射频地时,第一射频电路与射频天线导通工作,第二射频电路隔离断开;当所述控制单元通过控制电路导通模拟地和第二射频电路的射频地时,第二射频电路与射频天线导通工作,第一射频电路隔离断开。

5、具体的,所述第一射频电路的第一射频输入端rf1与射频天线之间设置有第一开关se1,所述第二射频电路的第二射频输入端rf2与射频天线之间设置有第二开关se2;

6、所述第一开关se1的控制端连接到控制单元的第一控制端;所述第二开关se2的控制端连接到所述控制单元第二控制端。

7、具体的,位于所述第一射频电路的第一控制电路包括第一控制开关s1、第一开关管m1、以及与第一开关管m1并联的第一导通电阻r1;

8、所述第一控制开关s1的一端连接到第一射频输入端rf1,另一端连接到第一射频地rfgnd1;所述第一控制开关s1的控制端连接到控制单元的第三控制端;

9、并联的所述第一开关管m1与第一导通电阻r1连接到第一射频地rfgnd1与模拟地agnd之间。

10、具体的,所述第一开关管m1的源极连接到第一射频地rfgnd1,漏极连接到模拟地agnd,栅极连接到控制单元的第二控制端。

11、具体的,位于所述第二射频电路的第二控制电路包括第二控制开关s2、第二开关管m2、以及与第二开关管m2并联的第二导通电阻r2;

12、所述第二控制开关s2的一端连接到第二射频输入端rf2,另一端连接到第二射频地rfgnd2;所述第二控制开关s2的控制端连接到控制单元的第四控制端。

13、具体的,所述第二开关管m2的源极连接到第二射频地rfgnd2,漏极连接到模拟地agnd,栅极连接到控制单元的第一控制端。

14、具体的,当第一射频电路导通时,se1闭合导通,s1打开截止,射频天线到rf1通路导通;se2和m1打开截止,s2和m2闭合导通;

15、当第二射频电路导通时,se2闭合导通,s2打开截止,射频天线到rf2通路导通;se1和m2打开截止,s1和m1闭合导通。

16、具体的,导通电阻的阻值小于2ohm。

17、另一方面,本申请提供一种射频开关芯片片上模拟地与射频地连接电路封装结构,用于射频开关芯片片上模拟地与射频地连接电路,在基板上设置用于模拟地的agndpad、用于第一射频输入端的rf1 pad、用于第二射频输入端的rf2 pad、用于射频天线的antpad、用于控制单元的ctrl pad、以及用于电源的vdd pad;

18、所述agnd pad通过引线引出一个agnd pin、rf1 pad通过引线引出rf1pin、rf2pad通过引线引出rf2 pin、ant pad通过引线引出ant pin、ctrl pad通过引线引出ctrlpin、以及vdd pad通过引线引出vdd pin;

19、在射频开关芯片片上模拟地与射频地连接电路的第一射电路工作时,第一射频地rfgnd1通过连通的模拟接地agnd引出到agnd pin;

20、在射频开关芯片片上模拟地与射频地连接电路的第一射电路工作时,第二射频地rfgnd2通过连通的模拟接地agnd引出到agnd pin。

21、本申请还提供另一种射频开关芯片片上模拟地与射频地连接电路封装结构,用于射频开关芯片片上模拟地与射频地连接电路,在基板上设置用于第一射频地的rfgnd1pad、用于第二射频地的rfgnd2 pad、用于第一射频输入端的rf1 pad、用于第二射频输入端的rf2 pad、用于射频天线的ant pad、用于控制单元的ctrl pad、以及用于电源的vdd pad;

22、所述rfgnd1 pad和rfgnd2 pad分别通过引线共同引出一个gnd pin、rf1 pad通过引线引出rf1 pin、rf2 pad通过引线引出rf2 pin、ant pad通过引线引出ant pin、ctrlpad通过引线引出ctrl pin、以及vdd pad通过引线引出vdd pin;

23、在射频开关芯片片上模拟地与射频地连接电路的第一射电路工作时,模拟接地agnd通过连通的第一射频地rfgnd1和对应的引线引出到agnd pin;

24、在射频开关芯片片上模拟地与射频地连接电路的第一射电路工作时,模拟接地agnd通过连通的第二射频地rfgnd2和对应的引线引出到agnd pin。

25、本申请实施例提供的技术方案带来的有益效果至少包括:2t掷数的射频开关芯片,将两个对称的射频电路设计成分别设置由控制单元控制通断的双开关,其中一开关位于射频输入和射频天线之间,另一个开关位于射频输入和射频地之间,在模拟地和射频地之间加入mos管和导通电阻,并将mos管的控制端与另一射频通路的控制开关连接。在一侧射频通路导通时,将该侧射频地断开,而将对侧射频地与模拟地连通,实现双射频地公用模拟地,从而减少在及岛上布设的pad数量,方便适应后续更新到更小尺寸封装形式。

技术特征:

1.一种射频开关芯片片上模拟地与射频地连接电路,其特征在于,包括射频天线、控制单元、对称设置的第一射频电路和第二射频电路;所述第一射频电路和第二射频电路共同连接到射频天线和控制单元上;

2.根据权利要求1所述的连接电路,其特征在于,所述第一射频电路的第一射频输入端rf1与射频天线之间设置有第一开关se1,所述第二射频电路的第二射频输入端rf2与射频天线之间设置有第二开关se2;

3.根据权利要求2所述的连接电路,其特征在于,位于所述第一射频电路的第一控制电路包括第一控制开关s1、第一开关管m1、以及与第一开关管m1并联的第一导通电阻r1;

4.根据权利要求3所述的连接电路,其特征在于,所述第一开关管m1的源极连接到第一射频地rfgnd1,漏极连接到模拟地agnd,栅极连接到控制单元的第二控制端。

5.根据权利要求4所述的连接电路,其特征在于,位于所述第二射频电路的第二控制电路包括第二控制开关s2、第二开关管m2、以及与第二开关管m2并联的第二导通电阻r2;

6.根据权利要求5所述的连接电路,其特征在于,所述第二开关管m2的源极连接到第二射频地rfgnd2,漏极连接到模拟地agnd,栅极连接到控制单元的第一控制端。

7.根据权利要求6所述的连接电路,其特征在于,当第一射频电路导通时,se1闭合导通,s1打开截止,射频天线到rf1通路导通;se2和m1打开截止,s2和m2闭合导通;

8.根据权利要求6所述的连接电路,其特征在于,导通电阻的阻值小于2ohm。

9.一种射频开关芯片片上模拟地与射频地连接电路封装结构,用于权利要求1-7任一所述的射频开关芯片片上模拟地与射频地连接电路,其特征在于,在基板上设置用于模拟地的agnd pad、用于第一射频输入端的rf1 pad、用于第二射频输入端的rf2 pad、用于射频天线的ant pad、用于控制单元的ctrl pad、以及用于电源的vdd pad;

10.一种射频开关芯片片上模拟地与射频地连接电路封装结构,用于权利要求1-8任一所述的射频开关芯片片上模拟地与射频地连接电路,其特征在于,在基板上设置用于第一射频地的rfgnd1 pad、用于第二射频地的rfgnd2pad、用于第一射频输入端的rf1 pad、用于第二射频输入端的rf2 pad、用于射频天线的ant pad、用于控制单元的ctrl pad、以及用于电源的vdd pad;

技术总结

本申请公开一种射频开关芯片片上模拟地与射频地连接电路及封装结构,涉及射频开关芯片领域,两个对称的射频电路分别设置由控制单元控制通断的双开关,一开关位于射频输入和射频天线之间,另一开关位于射频输入和射频地之间,在模拟地和射频地之间加入MOS管和导通电阻,并将MOS管的控制端与另一射频通路的控制开关连接。在一侧射频通路导通时,将该侧射频地断开,而将对侧射频地与模拟地连通,实现双射频地公用模拟地,从而减少在及岛上布设的pad数量,方便适应后续更新到更小尺寸封装形式。

技术研发人员:刘刚,杨震,赵云,郭天生,赵鹏

受保护的技术使用者:江苏乾合微电子有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!