一种高精度的低重频窄脉冲延迟控制电路的制作方法

本技术涉及模拟集成电路,具体涉及一种高精度的低重频窄脉冲延迟控制电路。

背景技术:

1、低重频窄脉冲的延迟控制电路当前主要应用于通信领域、音频处理、粒子物理实验、脉冲激光实验和声学、电磁学、机械系统等物理仿真实验中。此类延迟控制电路具备低重频窄脉冲的特性,与低重频窄脉冲类的探测信号进行时间对齐或时间延迟控制,实现测量、激发、控制等多种功能。低重频窄脉冲的信号测量、激发、控制越发要求高精度、高稳定性、高可控性。

技术实现思路

1、本实用新型的目的在于克服现有技术的不足,提供一种高精度的低重频窄脉冲延迟控制电路,以实现低重频窄脉冲信号的高精度延迟控制。

2、本实用新型的目的是通过以下技术方案来实现的:

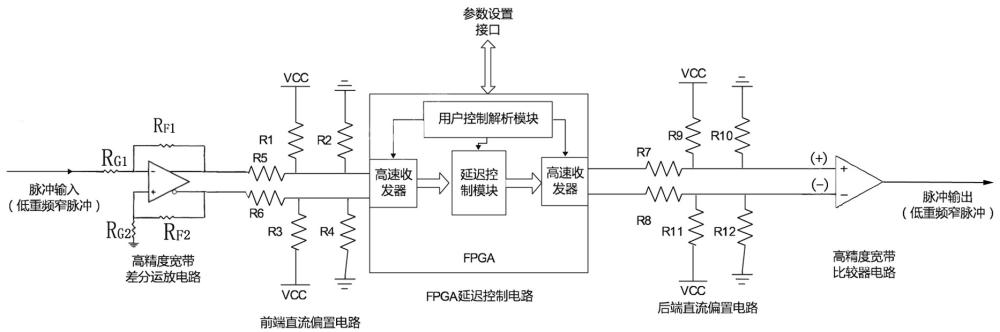

3、一种高精度的低重频窄脉冲延迟控制电路,包括依次连接的高精度宽带差分运放电路、前端直流偏置电路、fpga延迟控制电路、后端直流偏置电路和高精度宽带比较器电路;

4、所述的fpga延迟控制电路包括用户控制解析模块、第一高速收发器、延迟控制模块和第二高速收发器,所述的用户控制解析模块用于接收外设的参数并发送给第一高速收发器、延迟控制模块和第二高速收发器,第一高速收发器和第二高速收发器分别用于接收和发送延迟控制模块处理前后的低重频窄脉冲信号;

5、所述的高精度宽带差分运放电路用于将输入的低重频窄脉冲信号转化为两路差分信号;前端直流偏置电路用于将低重频窄脉冲信号的直流偏置电平偏移到第一高速收发器所需的直流偏置电平;fpga延迟控制电路用于通过用户设置参数对脉冲信号进行延迟控制处理;后端直流偏置电路用于对fpga延迟控制电路输出的低重频窄脉冲信号进行调制;高精度宽带比较器电路用于比较调制后产生的正负电压,得到所需要的低重频窄脉冲电信号。

6、进一步地,所述的高精度宽带差分运放电路包括第一运算放大器、电阻rf1、电阻rf2、电阻rg1和电阻rg2,低重频窄脉冲信号经电阻rg1输入到第一运算放大器的反相输入端,第一运算放大器的同相输入端通过电阻rg2接地,所述的电阻rf1的两端分别与第一运算放大器的反相输入端和同相输出端连接,电阻rf2的两端分别与第一运算放大器的同相输入端和反相输出端连接。

7、进一步地,所述的电阻rf1、电阻rf2、电阻rg1和电阻rg2满足以下关系:

8、rf1=rf2

9、rg1=rg2

10、

11、其中 v in为输入的低重频窄脉冲信号的电压; v dm为第一高速收发器的io电平的差分电压, v in_out为第一运算放大器单端输出电压。

12、进一步地,所述的第一运算放大器的等效带宽b大于输入信号的最小脉冲宽度的倒数的十倍。

13、进一步地,所述的前端直流偏置电路具有两个输入端和两个输出端,包括电阻r1~r6,电阻r1~r4满足以下关系:

14、

15、其中vcc为电源电压,vcm为第一高速收发器接口的直流偏置电平,rs为传输线的特征阻抗。

16、进一步地,所述后端直流偏置电路包括电阻r7~r12,后端直流偏置与前端直流偏置电路的结构对称。

17、进一步地,所述的第一高速收发器包括高速输入io接口和1:n串并转换模块,1:n串并转换模块用于将输入的高速串行输入信号进行1:n的串并转换,输出低速并行信号。

18、进一步地,所述的第二高速收发器包括高速输出io接口和n:1并串转换模块,n:1并串转换模块用于将低速并行信号进行n:1并串转换,输出高速串行输入信号。

19、进一步地,所述的延迟控制模块包括计数器和nbits的循环移位器,分别用于信号整数部分和小数部分的延迟。

20、进一步地,所述的高精度宽带比较器电路包括第二运算放大器,第二运算放大器的正相输入端和反相输入端分别与后端直流偏置电路的两个输出端连接,第二运算放大器的输出端输出延迟后的低重频窄脉冲信号。

21、本实用新型的有益效果是:

22、针对当下高精度、高稳定性、高可控性的需求,本实用新型实施例提供的一种低重频窄脉冲的延迟控制电路,针对低重频窄脉冲具备可调控延迟数量、高精度延时控制、低抖动性的特点,且能用过参数设计设置广泛应用于多领域中。

23、具体地,本实用新型具备以下优良性能:

24、(1)可编程调节延迟数量:可根据实际应用场景,通过参数上的设计计算设置电路,精准匹配工作环境并控制信号的延迟和相位,适应更广阔范围的探测、激发、控制等功能。

25、(2)高精度的延迟控制:延迟控制的时间精度可达到100ps,支持多科研领域的高精度探测、激发、控制实验系统。

26、(3)电路低抖动性:针对信号品质和稳定性要求较高的应用,低抖动性电路能够提供更稳定和精确的输出信号,减小因抖动引起的误差。在特定领域入通信、音频处理、数据采集中,低抖动性减少系统信噪比、避免干扰和失真,提高系统性能和信号质量。低抖动性也减少调试成本、系统故障风险以及系统后续的维修成本。

技术特征:

1.一种高精度的低重频窄脉冲延迟控制电路,其特征在于:包括依次连接的高精度宽带差分运放电路、前端直流偏置电路、fpga延迟控制电路、后端直流偏置电路和高精度宽带比较器电路;

2.根据权利要求1所述的一种高精度的低重频窄脉冲延迟控制电路,其特征在于:所述的高精度宽带差分运放电路包括第一运算放大器、电阻rf1、电阻rf2、电阻rg1和电阻rg2,低重频窄脉冲信号经电阻rg1输入到第一运算放大器的反相输入端,第一运算放大器的同相输入端通过电阻rg2接地,所述的电阻rf1的两端分别与第一运算放大器的反相输入端和同相输出端连接,电阻rf2的两端分别与第一运算放大器的同相输入端和反相输出端连接。

3.根据权利要求2所述的一种高精度的低重频窄脉冲延迟控制电路,其特征在于:所述的电阻rf1、电阻rf2、电阻rg1和电阻rg2满足以下关系:

4.根据权利要求2所述的一种高精度的低重频窄脉冲延迟控制电路,其特征在于:所述的第一运算放大器的等效带宽b大于输入信号的最小脉冲宽度的倒数的十倍。

5.根据权利要求1所述的一种高精度的低重频窄脉冲延迟控制电路,其特征在于:所述的前端直流偏置电路具有两个输入端和两个输出端,包括电阻r1~r6,电阻r1~r4满足以下关系:

6.根据权利要求5所述的一种高精度的低重频窄脉冲延迟控制电路,其特征在于:所述后端直流偏置电路包括电阻r7~r12,后端直流偏置与前端直流偏置电路的结构对称。

7.根据权利要求1所述的一种高精度的低重频窄脉冲延迟控制电路,其特征在于:所述的第一高速收发器包括高速输入io接口和1:n串并转换模块,1:n串并转换模块用于将输入的高速串行输入信号进行1:n的串并转换,输出低速并行信号。

8.根据权利要求7所述的一种高精度的低重频窄脉冲延迟控制电路,其特征在于:所述的第二高速收发器包括高速输出io接口和n:1并串转换模块,n:1并串转换模块用于将低速并行信号进行n:1并串转换,输出高速串行输入信号。

9.根据权利要求1所述的一种高精度的低重频窄脉冲延迟控制电路,其特征在于:所述的延迟控制模块包括计数器和nbits的循环移位器,分别用于信号整数部分和小数部分的延迟。

10.根据权利要求1所述的一种高精度的低重频窄脉冲延迟控制电路,其特征在于:所述的高精度宽带比较器电路包括第二运算放大器,第二运算放大器的正相输入端和反相输入端分别与后端直流偏置电路的两个输出端连接,第二运算放大器的输出端输出延迟后的低重频窄脉冲信号。

技术总结

本技术公开了一种高精度的低重频窄脉冲延迟控制电路,涉及模拟集成电路技术领域;包括:依次连接的用于将输入的低重频窄脉冲信号转化为两路差分信号的高精度宽带差分运放电路、用于将低重频窄脉冲信号的直流偏置电平偏移到第一高速收发器所需的直流偏置电平的前端直流偏置电路、用于通过用户设置参数对脉冲信号进行延迟控制处理的FPGA延迟控制电路、用于对FPGA延迟控制电路输出的低重频窄脉冲信号进行调制的后端直流偏置电路和用于比较调制后产生的正负电压,得到所需要的低重频窄脉冲电信号的高精度宽带比较器电路。本技术可实现低重频窄脉冲的高精度可调节延迟控制,还可减小电路抖动性。

技术研发人员:蒙顺开

受保护的技术使用者:海豚乐智科技(成都)有限责任公司

技术研发日:20240116

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!